# MODEL DQ614 DISC CONTROLLER **INSTRUCTION MANUAL**

**March 1984**

Distributed Logic Corporation 12800-G Garden Grove Blvd. Garden Grove, California 92643 Telephone: (714) 534-8950 TELEX: 681399

Copyright ©1984 by

Distributed Logic Corporation

Printed in the United States of America

## TABLE OF CONTENTS

| Section |                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

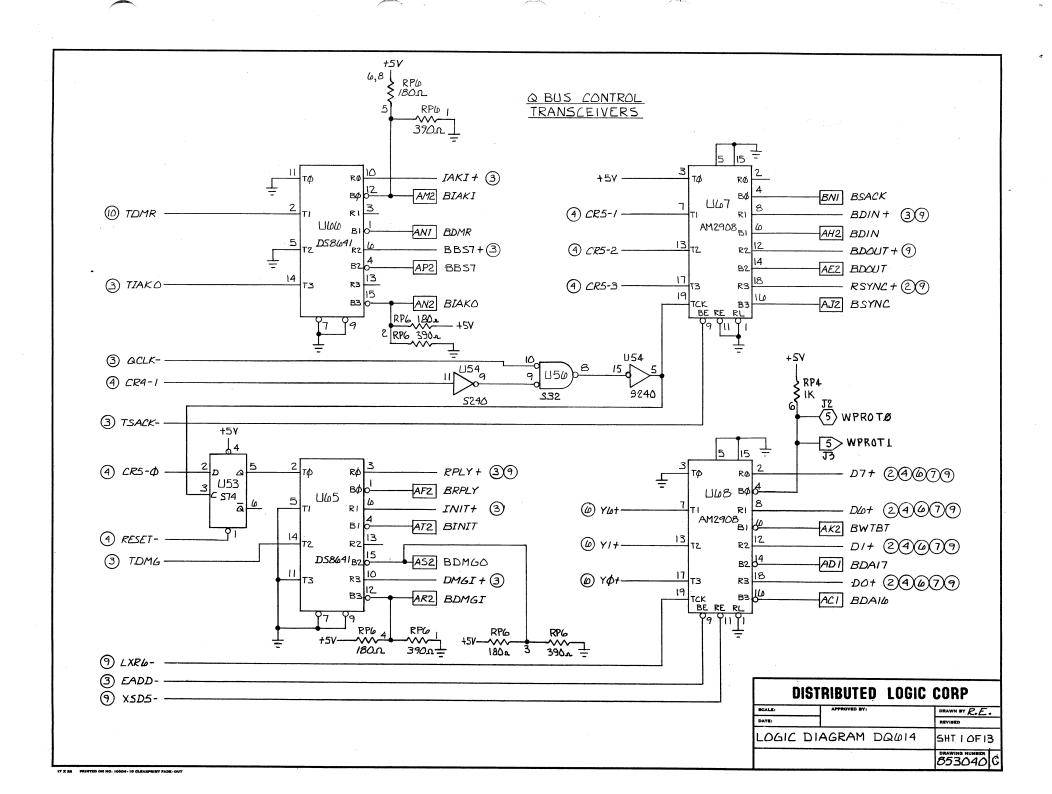

| 1       | DESCRIPTION Introduction Controller Characteristics LSI-11 Q Bus Interface Interrupt Disc Interface                                                                                                                                                                                                                                                                                                               | 1-1<br>1-1<br>1-1<br>1-2                                                                           |

|         | Disc Interface Operating System Compatibility Controller Specifications                                                                                                                                                                                                                                                                                                                                           | . 1-3<br>. 1-3                                                                                     |

| 2       | INSTALLATION Inspection Pre-Installation Checks Installation                                                                                                                                                                                                                                                                                                                                                      | . 2-1<br>. 2-1                                                                                     |

| 3       | OPERATION Introduction Precautions and Preoperation Checks Bootstrap Switches Bootstrap Procedure Format and Test Programs Diagnostic Test Program Test Controller Test Disc Drive Format                                                                                                                                                                                                                         | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-4<br>3-4<br>3-4                                               |

|         | Sequential Read Selected Read Random Seek, Read Random Seek, Write Data, Read Data, Compare Test Test ECC Logic Assign Alternate Track                                                                                                                                                                                                                                                                            | 3-5<br>3-5<br>3-5<br>3-5                                                                           |

| 4       | PROGRAMMING Programming Definitions Operations Interrupts Diagnostic Control/Status Register Bus Address Register                                                                                                                                                                                                                                                                                                 | 4-1<br>4-2<br>4-2<br>4-3<br>4-4                                                                    |

| •       | Disc Address Register RLDA on a SEEK Command RLDA on a READ or WRITE Data Command RLDA on a GET STATUS Command Multipurpose Register During Read/Write Command for Word Count During a Get Status Command Address Extension Register                                                                                                                                                                              | 4-5<br>4-5<br>4-6<br>4-6<br>4-7<br>4-7                                                             |

| 5       | TROUBLESHOOTING AND THEORY Basic System Troubleshooting Controller Symptoms Physical Layout Term Listing Adjustment Procedure for Data Separator Theory Computer Interface Microprocessor Functions RAM Data Buffer Peripheral Interface-Write Data Path ECC — Write MFM — Write Peripheral Interface — Read Data Path Phase-Locked Loop — Read Data ECC — Read Address Mark Detect and Byte Clock Control — Read | 5-1<br>5-1<br>5-1<br>5-1<br>5-6<br>5-6<br>5-7<br>5-8<br>5-8<br>5-8<br>5-14<br>5-14<br>5-15<br>5-16 |

| 6       | Clocks                                                                                                                                                                                                                                                                                                                                                                                                            | 0-10                                                                                               |

## **ILLUSTRATIONS**

| Figure                                                                                                      |                                                                                                                                                                                                                                                                                                                    | Page                                                                               |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

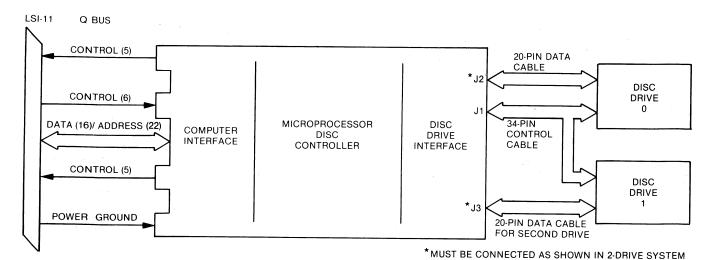

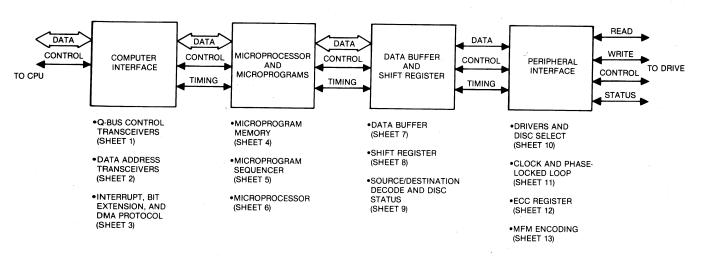

| 1-1                                                                                                         | Disc Controller System Simplified Diagram                                                                                                                                                                                                                                                                          | 1-1                                                                                |

| 2-1<br>2-2                                                                                                  | Controller Configuration Typical Backplane Configuration                                                                                                                                                                                                                                                           | 2-2<br>2-4                                                                         |

| 4-1                                                                                                         | Register Summary                                                                                                                                                                                                                                                                                                   | 4-2                                                                                |

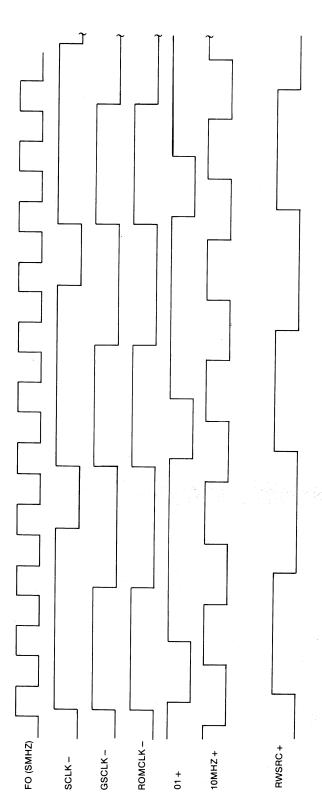

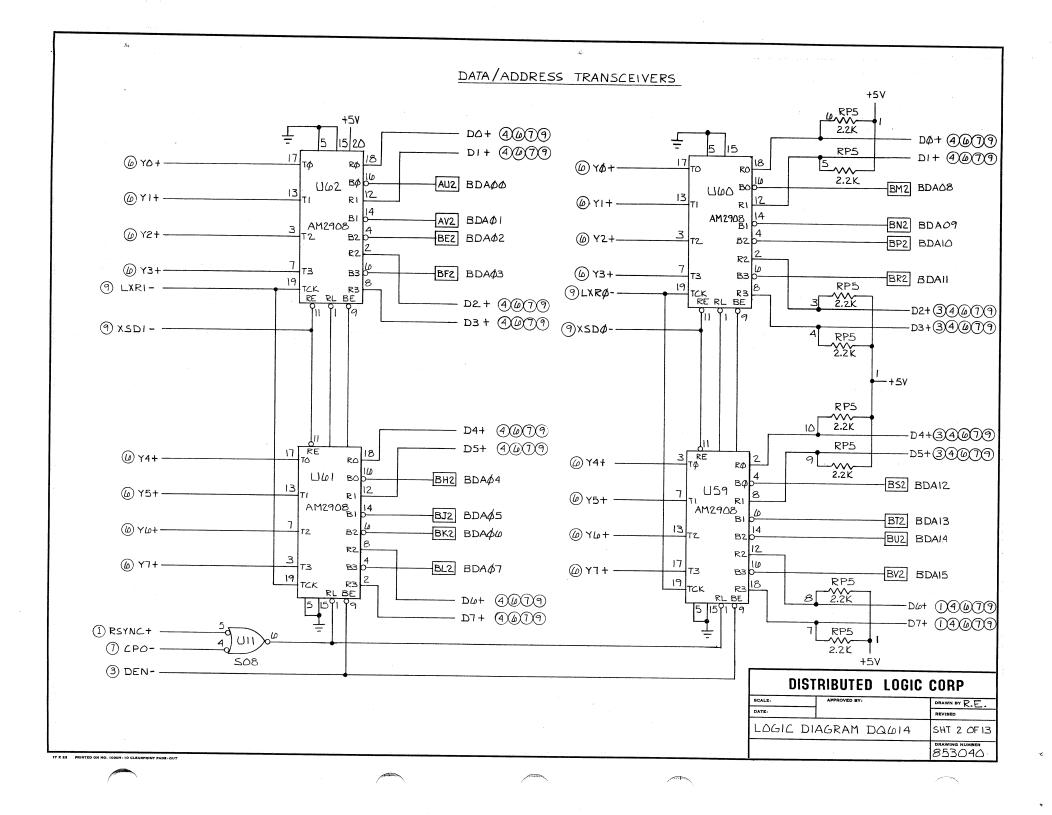

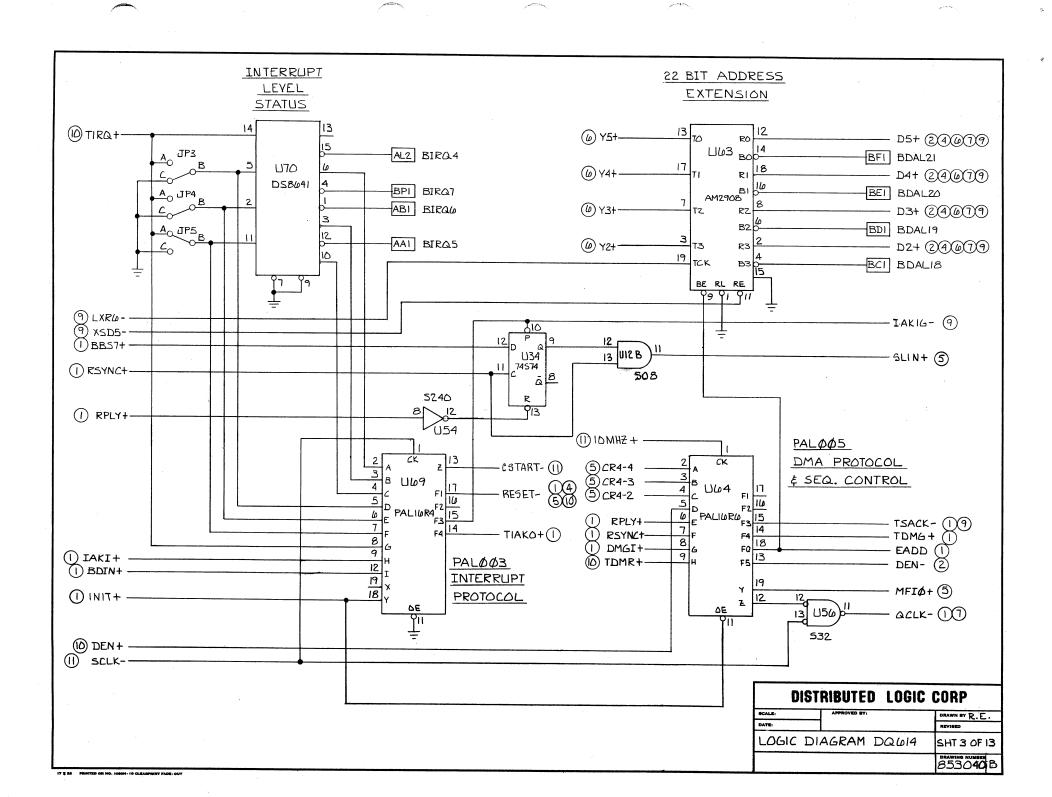

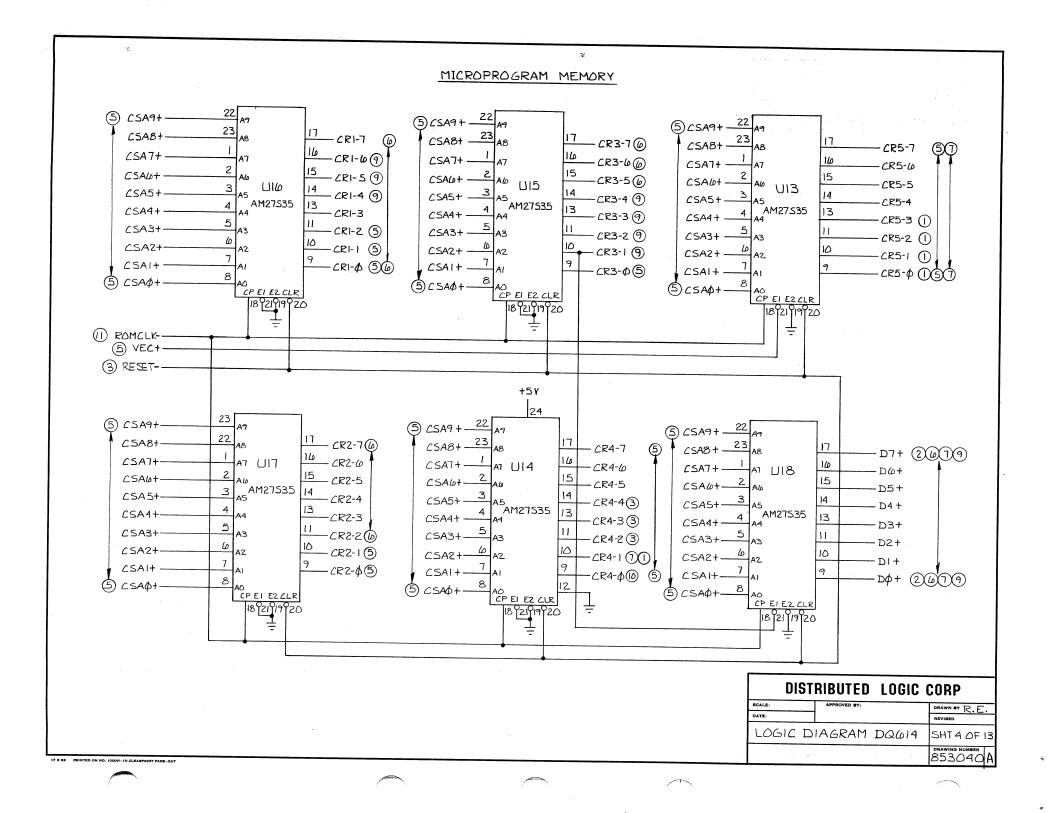

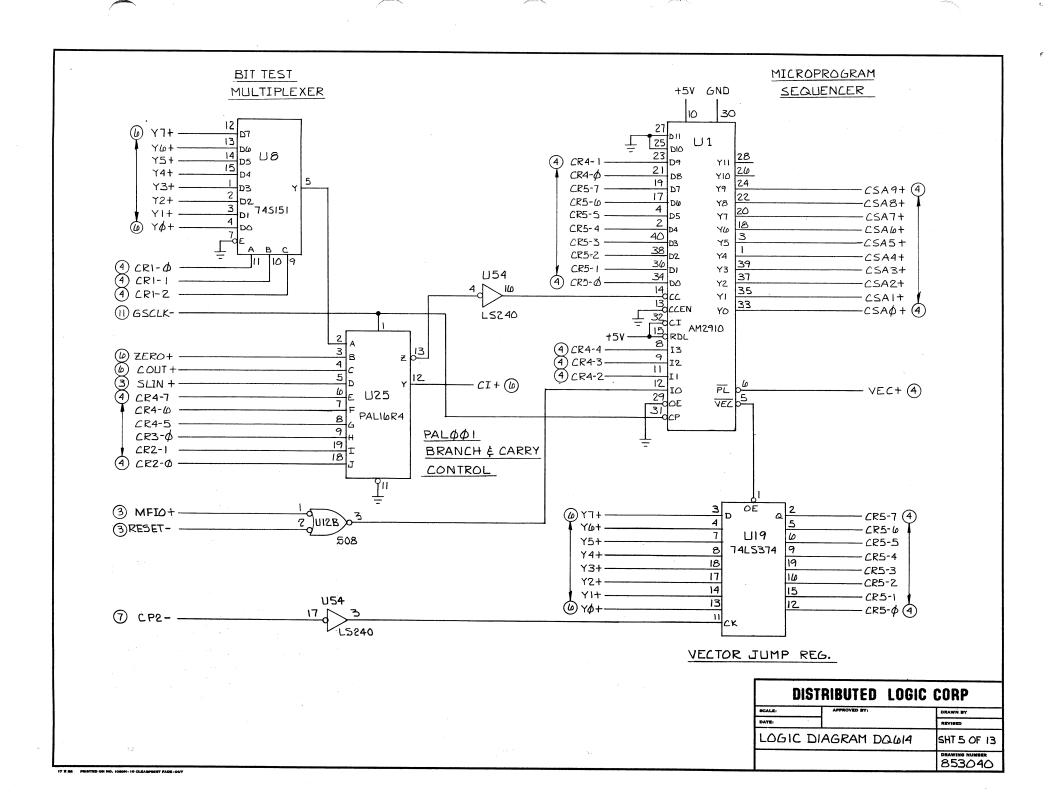

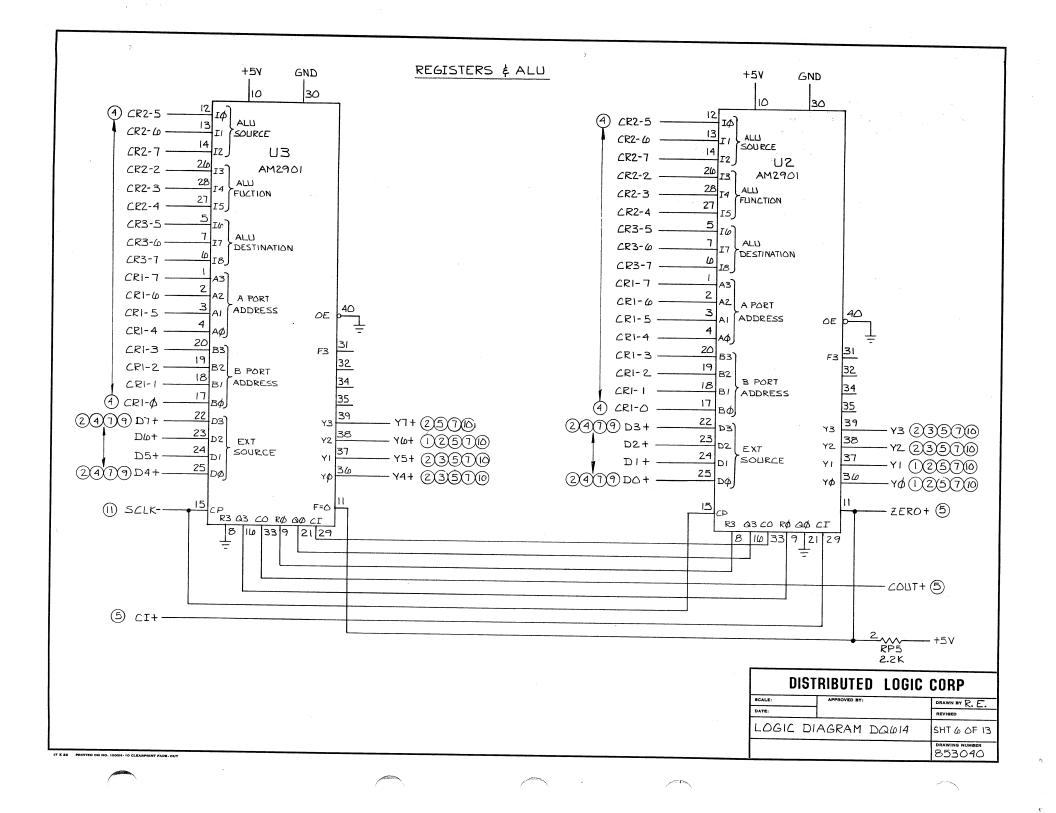

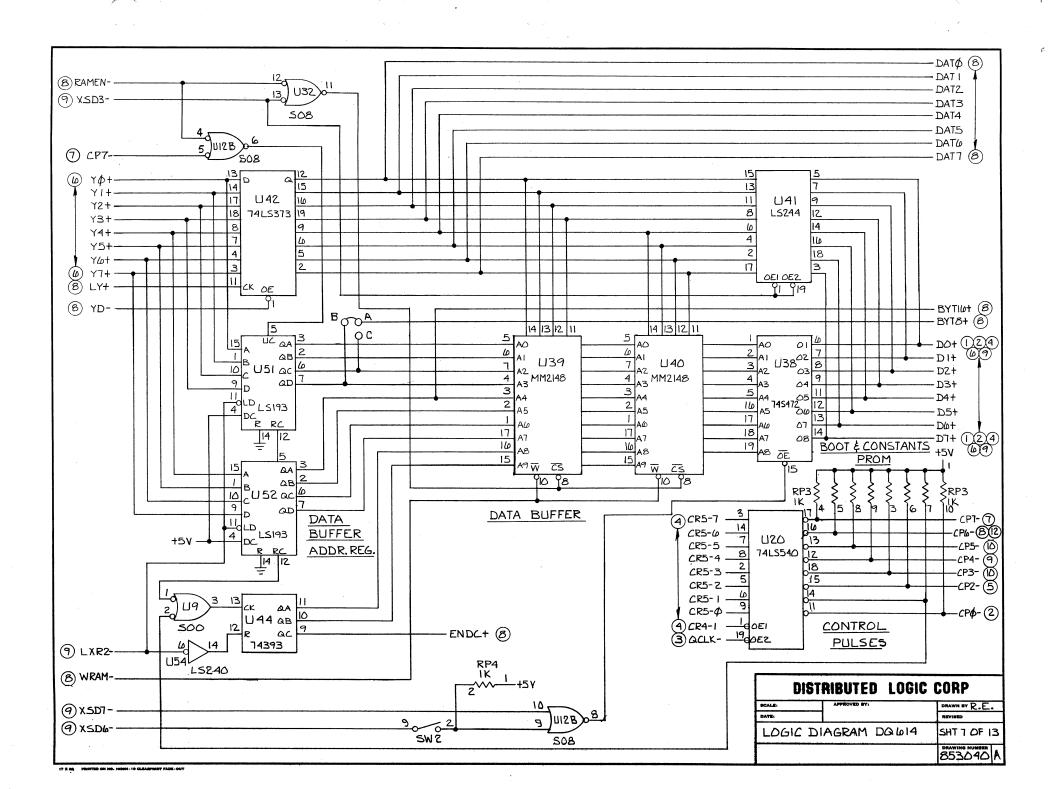

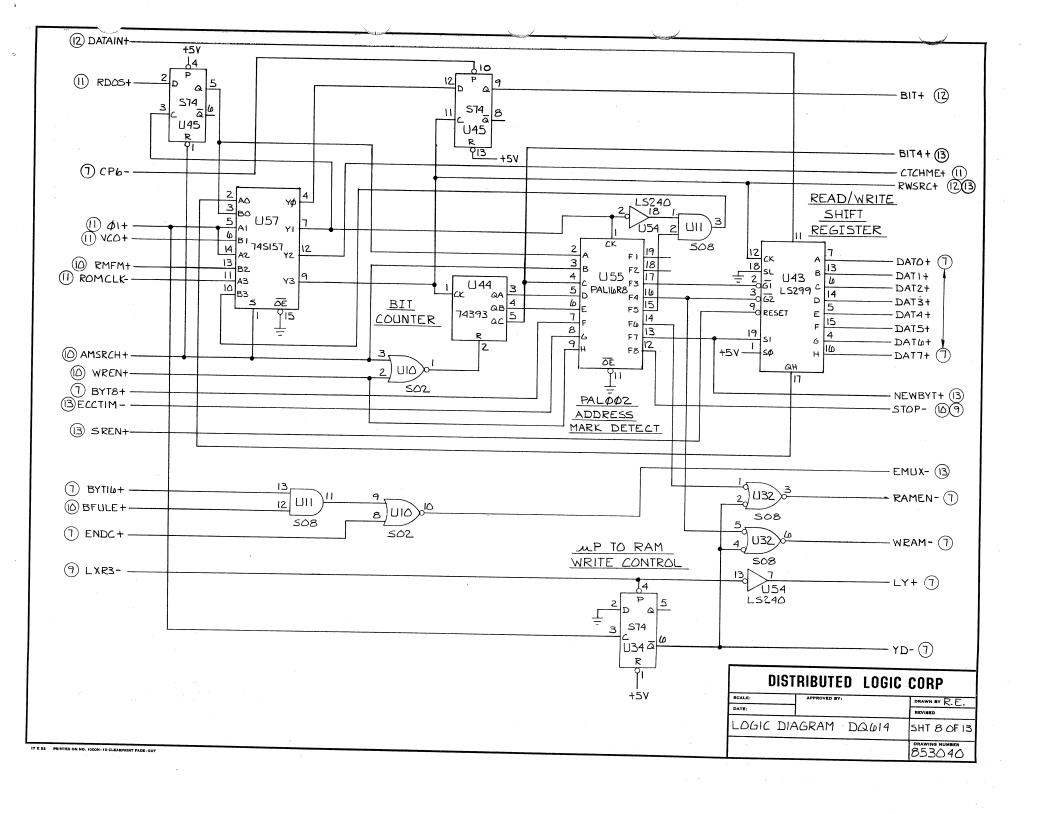

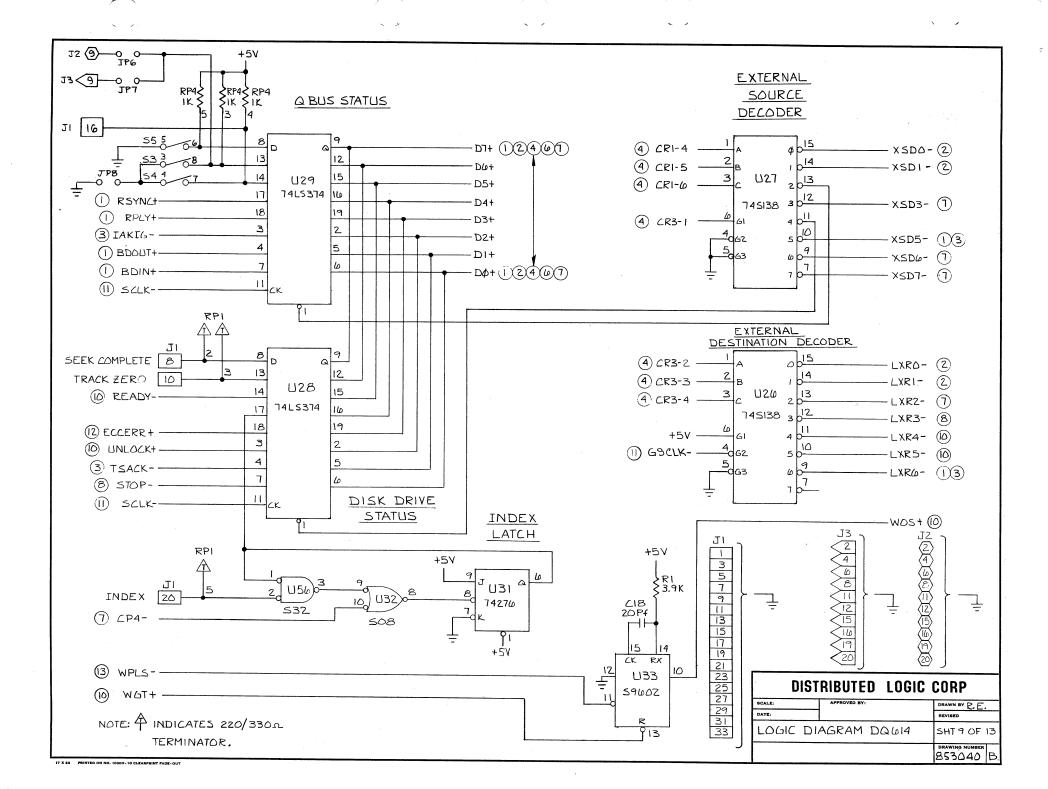

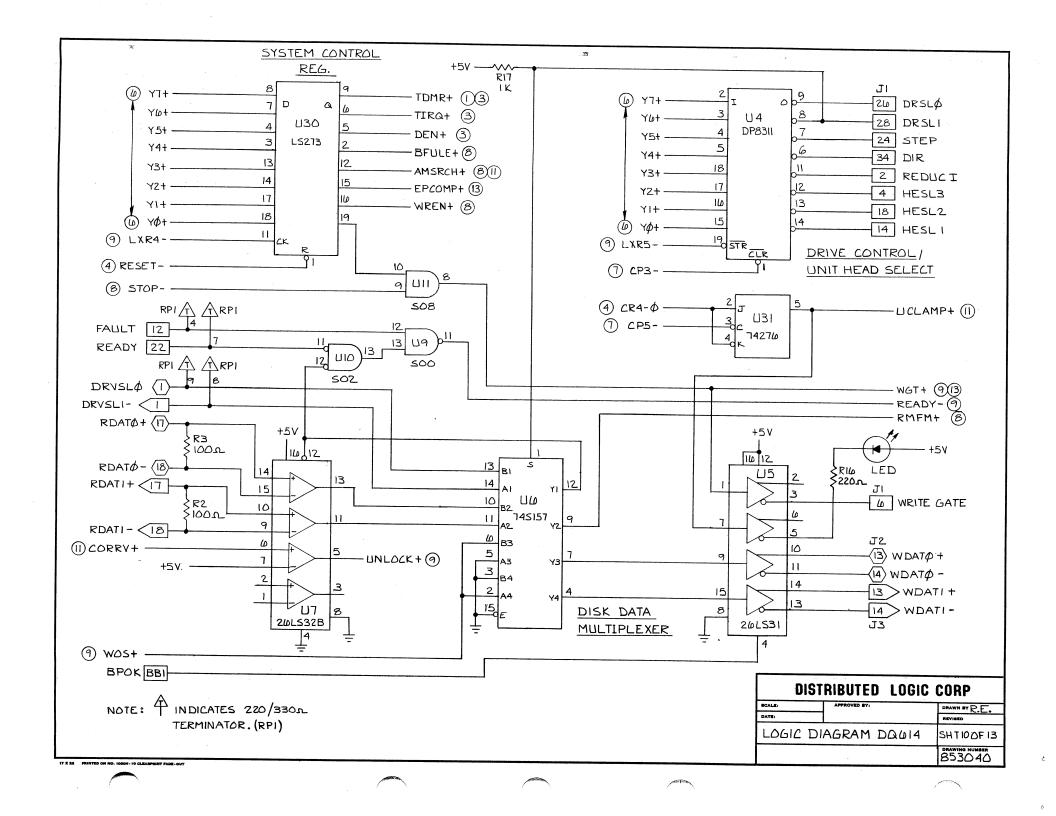

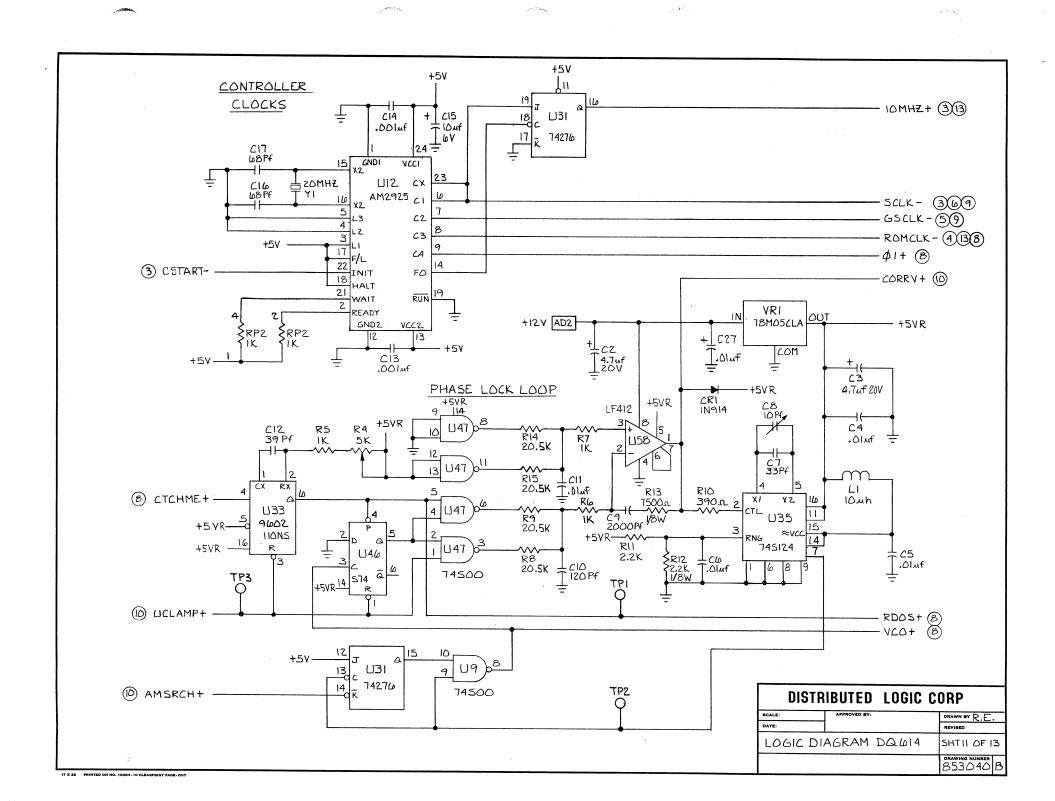

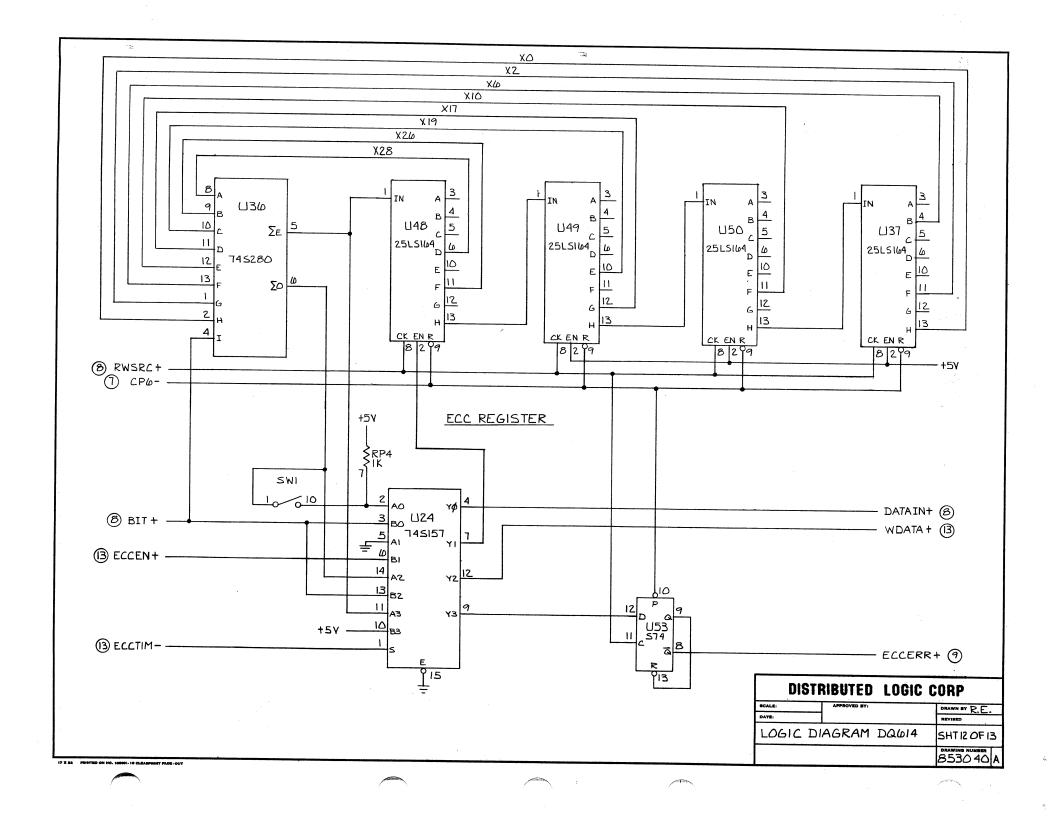

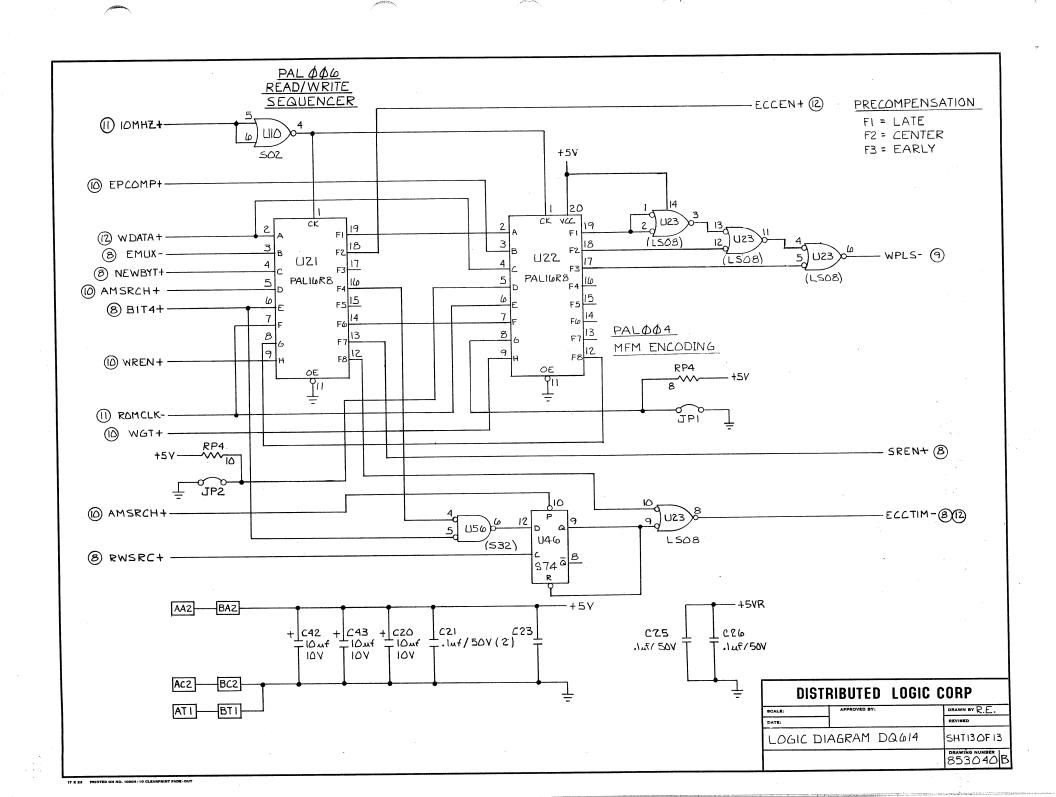

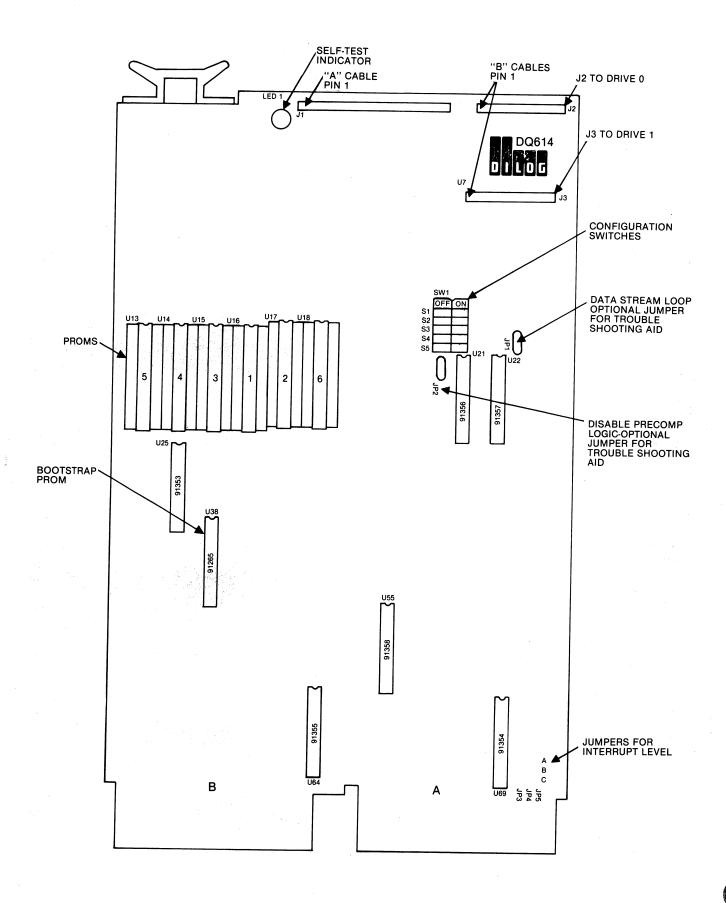

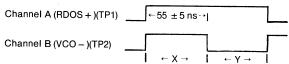

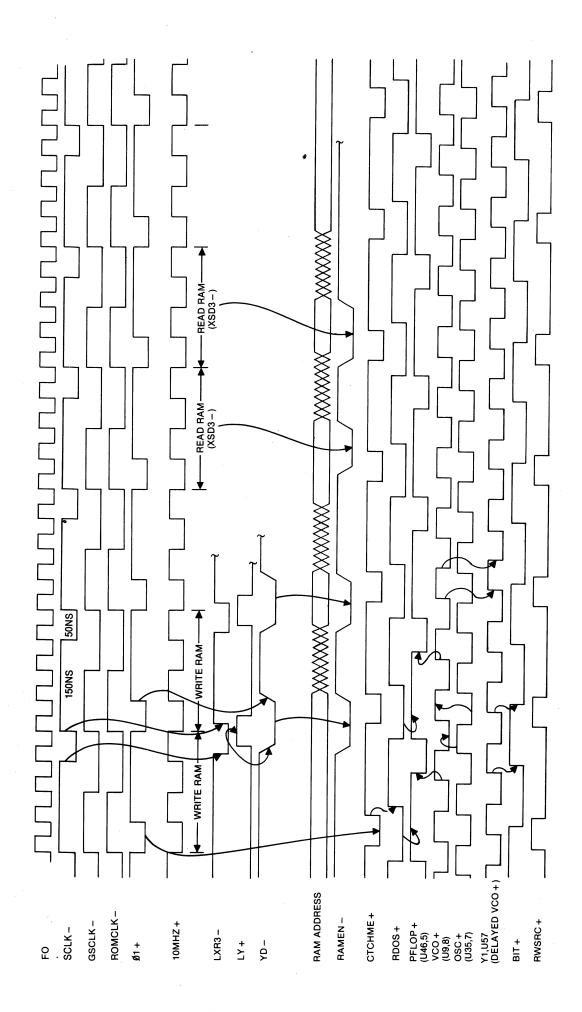

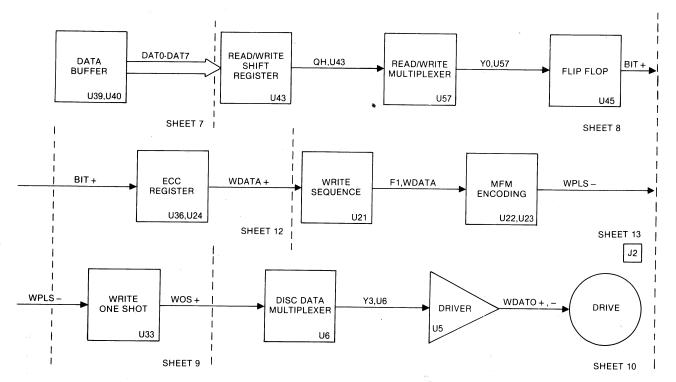

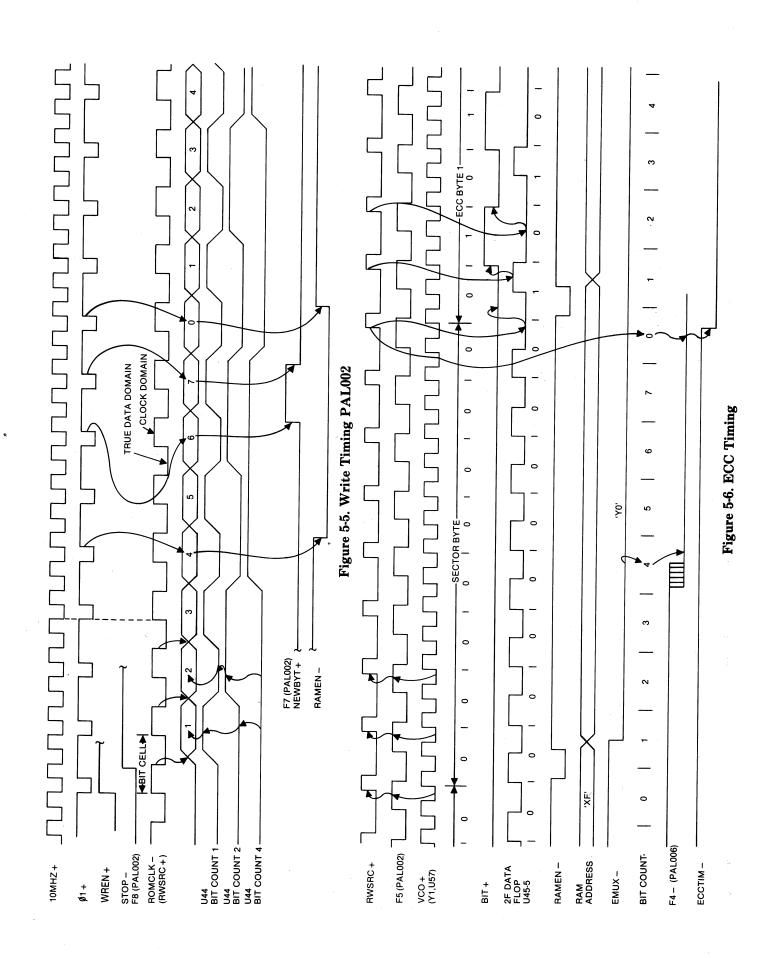

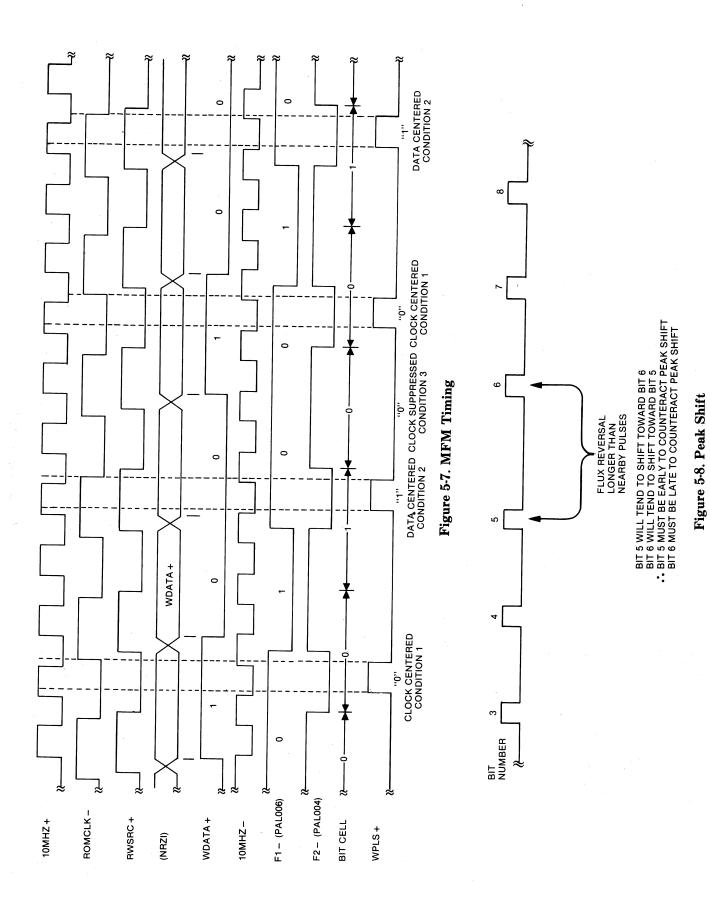

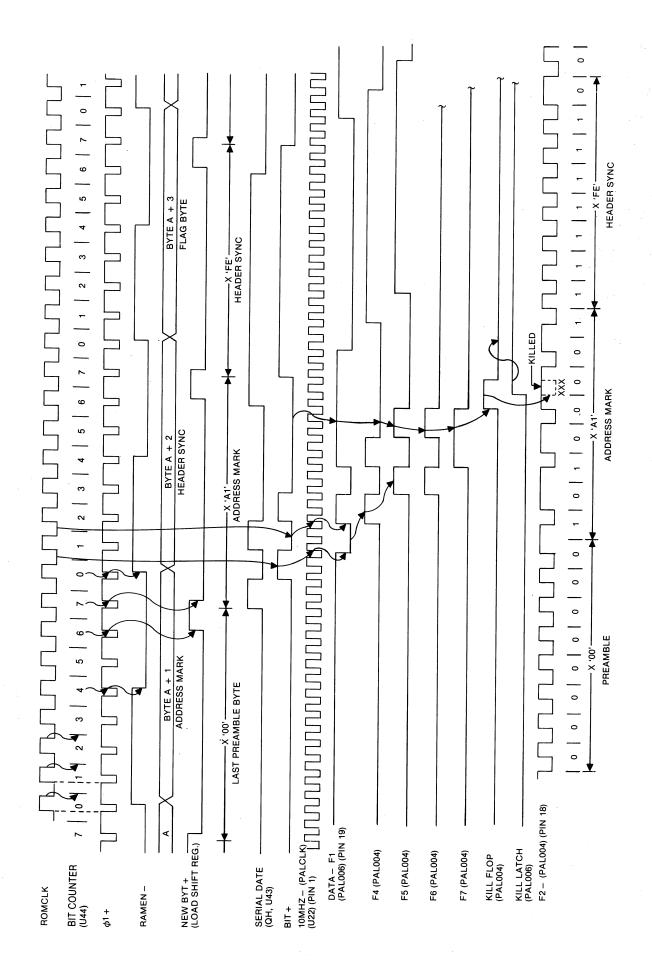

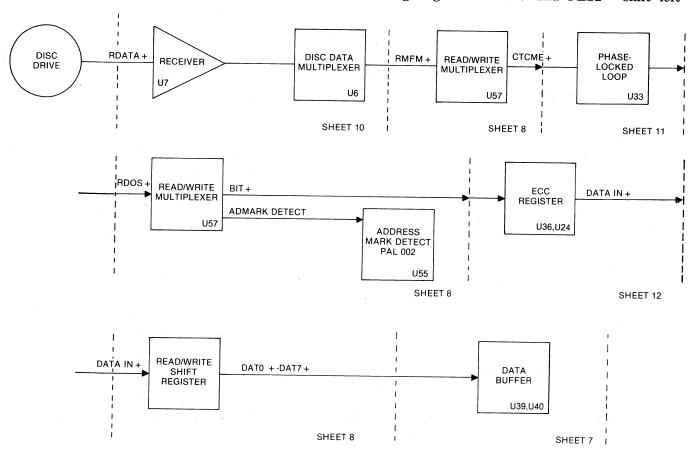

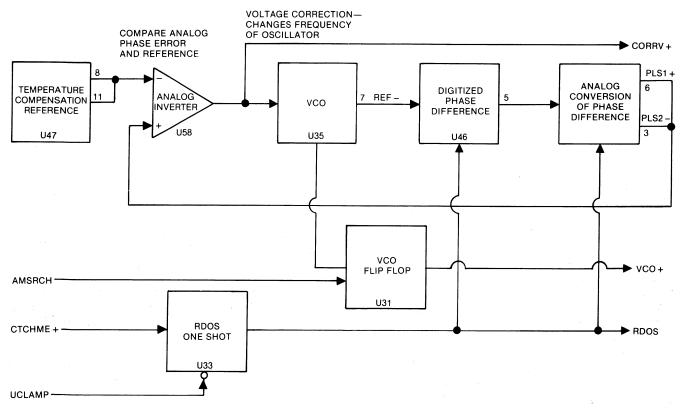

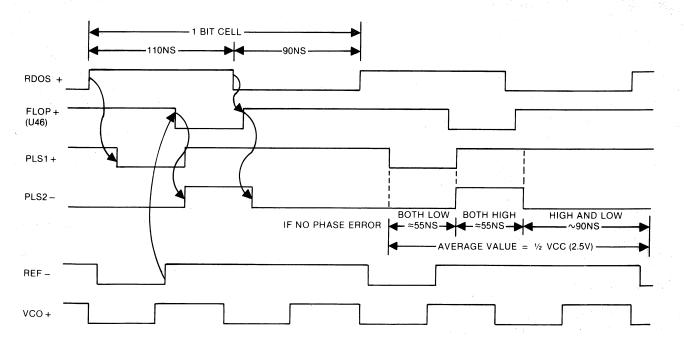

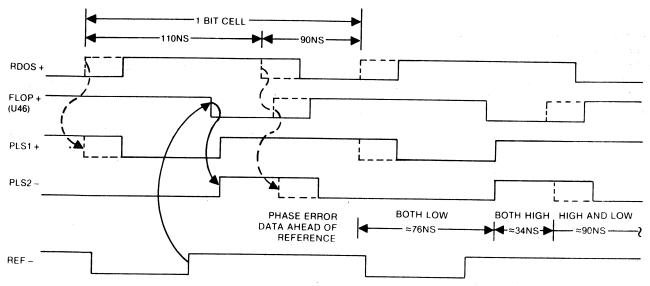

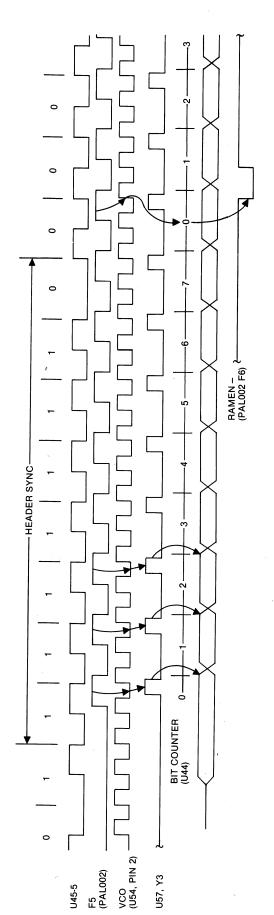

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9<br>5-10<br>5-11<br>5-12<br>5-13<br>5-14<br>5-15 | Board Layout Simplified Block Diagram Ram Address Chip Select Timing Write Data Path Write Timing PAL002 ECC Timing MFM Timing Peak Shift Address Mark and KILL Timing Read Data Path Simplified Diagram of Phase-Locked Loop PLL Timing with No Phase Error PLL Timing with Phase Error Byte Clock Control Clocks | 5-6<br>5-9<br>5-10<br>5-11<br>5-12<br>5-12<br>5-13<br>5-14<br>5-15<br>5-15<br>5-16 |

|                                                                                                             | TABLES                                                                                                                                                                                                                                                                                                             |                                                                                    |

| Table                                                                                                       |                                                                                                                                                                                                                                                                                                                    | Page                                                                               |

| 1-1<br>1-2<br>1-3                                                                                           | Controller/Q-Bus Interface Lines Controller to Drive I/O Interface — "A" Cable Controller to Drive Data Cable — "B" Cable                                                                                                                                                                                          | 1-3                                                                                |

| 2-1<br>2-2                                                                                                  | Configuration Switches Component and Jumper Options                                                                                                                                                                                                                                                                | 2-3                                                                                |

| 5-1<br>5-2<br>5-3                                                                                           | Controller Symptoms Term Listing Enable Precompensation                                                                                                                                                                                                                                                            | 5-2<br>5-4<br>5-10                                                                 |

### SECTION 1 DESCRIPTION

### INTRODUCTION

This manual describes the installation, operation, programming, troubleshooting, and theory of operation of Distributed Logic Corporation (DILOG) Model DQ614 Disc Controller. The controller interfaces DEC\* LSI-11 based computer systems to ST506 compatible Winchester disc drives. The complete controller occupies one dual-wide module in the backplane. Full sector buffering in the controller matches the transfer rate of the disc drive and the CPU. The controller is software compatible with DEC drivers, emulating RL01/RL02 drives.

### CONTROLLER CHARACTERISTICS

The disc controller links the LSI-11 computer to one or two disc storage units. Commands from the computer are received and interpreted by the controller and translated into a form compatible with the disc units. Buffering and signal timing for data transfers between the computer and the discs are performed by the controller.

A microprocessor is the sequence and timing center of the controller. The control information is stored as firmware instructions in read-only-memory (ROM) on the controller board. One section of

\*DEC is a registered trademark of Digital Equipment Corporation.

the ROM contains a diagnostic program that tests the functional operation of the controller. This self-test is done automatically each time power is applied or under operator control by pressing the RESET switch. A green diagnostic indicator on the controller board lights if self-test passes.

Data transfers are directly to and from the computer memory using the DMA facility of the LSI-11 I/O bus. In addition, the controller monitors the status of the disc units and the data being transferred and presents this information to the computer upon request. An error correction code (ECC) with a 32-bit checkword corrects error bursts up to 11 bits. To compensate for media errors, bad sectors are skipped and alternates assigned, and there is an automatic retry feature for read errors. The controller is capable of addressing two megawords and controlling up to two disc drives in various configurations up to a total on-line capacity of 40 megabytes. Figure 1-1 is a simplified diagram of a disc system.

### LSI-11 Q BUS INTERFACE

Commands, data and status transfers between the controller and the computer are executed via the parallel I/O bus (Q bus) of the computer. Data transfers are direct to memory via the DMA facility of the Q bus; commands and status are under programmed I/O. Controller/Q bus interface lines are listed in Table 1-1.

Figure 1-1. Disc Controller System Simplified Diagram

Table 1-1. Controller/Q-Bus Interface Lines

| BUS PIN                                                                                 | MNEMONIC                                     | INPUT/<br>OUTPUT |                                                                                                                                                          |

|-----------------------------------------------------------------------------------------|----------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| AJ1, AM1, RT1, BJ1,<br>BM1, BT1, BC2, CJ1,<br>CM1, CT1, CC2, DJ1,<br>DM1, DT1, DC2      | GND                                          | 0                | Signal Ground and DC return.                                                                                                                             |

| AN1                                                                                     | BDMR L                                       | 0                | Direct Memory Access (DMA) request from controller: active low.                                                                                          |

| AP1                                                                                     | BHALT L                                      | N/A              | Stops program execution. Refresh and DMA is enabled. Console operation is enabled.                                                                       |

| AR1                                                                                     | BREF L                                       | N/A              | Memory Refresh.                                                                                                                                          |

| BA1                                                                                     | BDCOK H                                      | . 1              | DC power ok. All DC voltages are normal.                                                                                                                 |

| BB1                                                                                     | врок н                                       | N/A              | Primary power ok. When low activates power fail trap sequence.                                                                                           |

| BN1                                                                                     | BSACK L                                      | 0                | Select Acknowledge. Interlocked with BDMGO indicating controller is bus master in a DMA sequence.                                                        |

| BR1                                                                                     | BEVNT L                                      | N/A              | External Event Interrupt Request.                                                                                                                        |

| BV1, AA2, BA2, CA2,<br>DA2                                                              | +5                                           | l .              | + 5 volt system power.                                                                                                                                   |

| AD2, BD2                                                                                | + 12                                         | N/A              | + 12 volt system power.                                                                                                                                  |

| AE2                                                                                     | BDOUT L                                      | I/O              | Data Out. Valid data from bus master is on the bus. Interlocked with BRPLY.                                                                              |

| AF2                                                                                     | BRPLY L                                      | I/O              | Reply from slave to BDOUT or BDIN and during IAK.                                                                                                        |

| AH2                                                                                     | BDIN L                                       | 1/0              | Data Input. Input transfer to master (states master is ready for data). Interlocked with BRPLY.                                                          |

| AJ2                                                                                     | BSYNC L                                      | I/O              | Synchronize: becomes active when master places address on bus; stays active during transfer.                                                             |

| AK2                                                                                     | BWTBT L                                      | I/O              | Write Byte: indicates output sequence to follow (DATO or DATOB) or marks byte address time during a DATOB.                                               |

| AL2                                                                                     | BIRQ L                                       |                  | Interrupt Request.                                                                                                                                       |

| AM2<br>AN2<br>CM2<br>CN2                                                                | BIAK1I L<br>BIAK1O L<br>BIAK2I L<br>BIAK2O L | 0  1             | Serial Interrupt Acknowledge input and output lines routed from Q-Bus, through devices, and back to processor to establish and interrupt priority chain. |

| AT2                                                                                     | BINIT L                                      | 1 1              | nitialize. Clears devices on I/O bus.                                                                                                                    |

| AU2, AV2, BE2, BF2,<br>BH2, BJ2, BK2, BL2,<br>BM2, BN2, BP2, BR2,<br>BS2, BT2, BU2, BV2 | BDAL0 L<br>through<br>BDAL15 L               | I/O [            | Data/address lines, 0-15.                                                                                                                                |

| AR2<br>AS2<br>CR2<br>CS2                                                                | BDMG11 L<br>BDMG10 L<br>BDMG21 L<br>BDMG20 L |                  | OMA Grant Input and Output. Serial DMA priority line from computer, through devices and back to computer.                                                |

| AP2                                                                                     | BBS7 L                                       | I E              | Bank 7 Select. Asserted by bus master when address in upper 4K bank is placed on the bus.                                                                |

| AC1, AD1, BC1, BD1,<br>BE1, BF1                                                         | BDAL 16 L<br>-BDAL 21 L                      |                  | extended Address Bits 16-21                                                                                                                              |

## INTERRUPT

The interrupt vector address is factory set to address 160. The vector address is programmed in a PROM on the controller, allowing user selection.

Interrupt requests are generated under the following conditions:

- 1. A hard error occurs.

- 2. A soft error occurs. Soft errors are checksum errors (CSE).

- 3. The designated number of words has been transferred.

- A selected disc drive has accepted a seek or drive reset command.

- 5. A seek or drive reset function has been completed.

### DISC INTERFACE

The controller interfaces with one or two disc drives through 34- and 20-pin cables. If two drives are used, the 34-pin control cable is daisy chained to drive 0 and 1. The 20-pin data cables are connected separately from the controller to each drive. The maximum cable length is 20 feet. Table 1-2 lists the control interface signals. Table 1-3 lists the data interface signals.

### OPERATING SYSTEM COMPATIBILITY

RT11: The emulation is transparent to the RT11 version 4.0 operating system, using the standard device handler supplied by DEC.

RSX11\*: The emulation is transparent to the RSX11 version 4.0 operating system, using the standard device handler supplied by DEC.

RSTS\*: The emulation is transparent to the RSTS version 7.1 operating system, using the standarad device handler supplied by DEC.

### CONTROLLER SPECIFICATIONS†

- Mechanical The DQ614 is completely contained on one dual module 8.62 inches high by 5.19 inches wide and plugs into and requires one dual slot in any DEC LSI-11 backplane.

- Computer I/O—

- Register Addresses (PROM selectable)

- Control/Status Register (RLCS) 774 400

- Bus Address Register (RLBA) 774 402

- Disc Address Register (RLDA) 774 404

- Multipurpose Register (RLMP) 774 406

- Address Extension Register (RLAE) 774 410

- Data Transfer

- Method: DMA

- Maximum block size transferred in a single operation is 16K words.

- Bus Load

- 1 std unit load

- Address Ranges

- Computer Memory: to 2 megawords

- Interrupt Vector—Four interrupt levels jumper selectable. Factory set to Address 160, level 5.

Table 1-2. Controller To Drive I/O Interface — "A" Cable

| Si (SU 00 =                        | Τ.  | i .        |

|------------------------------------|-----|------------|

| Signal Name (DILOG Term)           | Pin | Source     |

| Ground                             | 1   | 1.00       |

| REDUCE WRITE CURRENT<br>(REDUCE I) | 2   | Controller |

| Ground                             | 3   |            |

| HEAD SELECT 3 (HESL3)              | 4   | Controller |

| Ground                             | 5   |            |

| WRITE GATE                         | 6   | Controller |

| Ground                             | 7   |            |

| SEEK COMPLETE (SEEK COMP)          | 8   | Drive      |

| Ground                             | 9   | × 0        |

| TRACK 0                            | 10  | Drive      |

| Ground                             | 11  |            |

| WRITE FAULT (FAULT)                | 12  | Drive      |

| Ground                             | 13  |            |

| HEAD SELECT 1 (HESL1)              | 14  | Controller |

| Ground                             | 15  |            |

| SELECT/NOT USED                    | 16  | Drive      |

| Ground                             | 17  |            |

| HEAD SELECT 2 (HESL2)              | 18  | Controller |

| Ground                             | 19  |            |

| INDEX                              | 20  | Drive      |

| Ground                             | 21  | 1          |

| READY                              | 22  | Drive      |

| Ground                             | 23  |            |

| STEP                               | 24  | Controller |

| Ground                             | 25  | • .        |

| DRIVE SELECT 1 (DRSL1)             | 26  | Controller |

| Ground                             | 27  |            |

| DRIVE SELECT 2 (DRSL2)             | 28  | Controller |

| Ground                             | 29  |            |

| DRIVE SELECT 3 (DRSL3)             | 30  | Controller |

| Ground                             | 31  |            |

| NOT USED                           | 32  |            |

| Ground                             | 33  |            |

| DIRECTION IN                       | 34  | Controller |

- Disc Drive I/O

- Connector—One 34-pin flat ribbon cable and two 20-pin flat ribbon cables.

- Signal: ST506 compatible

- Power: +5 volts @ 3.5 amps (typical), +12 volts at 300 milliamps from computer power supply.

- Environment: Operating temperature 0°C to 45°C., humidity 0 to 70% non-condensing.

- Shipping Weight: 5 pounds including documentation and cables.

- Shock—Non-repetitive of less than 0.5G.

†Specifications subject to change without notice.

<sup>\*</sup>RSX and RSTS are registered trademarks of Digital Equipment Corporation.

Table 1-3. Controller to Drive Data Cable — "B" Cable

| Signal         | Pin | J2<br>Term               | J3<br>Term               | Source                                 |

|----------------|-----|--------------------------|--------------------------|----------------------------------------|

| DRIVE SELECTED | 1   | DRIVE SELECTED<br>UNIT 0 | DRIVE SELECTED<br>UNIT 1 | Drive                                  |

| Ground         | 2   |                          | _                        | _                                      |

| Reserved       | 3   | _                        | _                        |                                        |

| Ground         | 4   |                          | _                        | _                                      |

| Reserved       | 5   | _                        | _                        | _                                      |

| Ground         | 6   | <del></del>              | _                        | _                                      |

| Reserved       | 7   | _                        | _                        |                                        |

| Ground         | 8   | _                        | _                        |                                        |

| Reserved       | 9   | _                        |                          | ·                                      |

| Spare          | 10  |                          | _                        |                                        |

| Ground         | 11  | _                        | _                        |                                        |

| Ground         | 12  |                          |                          |                                        |

| WRITE DATA +   | 13  | WDAT0 +                  | WDAT1 +                  | Controller                             |

| WRITE DATA -   | 14  | WDAT0 -                  | WDAT1 –                  | Controller                             |

| Ground         | 15  | <del></del>              | <u> </u>                 | —————————————————————————————————————— |

| Ground         | 16  |                          | _                        | <u> </u>                               |

| READ DATA +    | 17  | RDAT0 +                  | RDAT1 +                  | Drive                                  |

| READ DATA -    | 18  | RDATO -                  | RDAT1 –                  | Drive                                  |

| Ground         | 19  | _                        | <del>-</del>             |                                        |

| Ground         | 20  |                          | _                        |                                        |

### SECTION 2 INSTALLATION

### INSPECTION

The padded shipping carton that contains the controller board also contains an instruction manual and may contain cables if this option is exercised. The controller is completely contained on the dual-size printed circuit board. Disc drives, if supplied, are contained in separate shipping cartons. Inspect the controller and cables for damage.

### **CAUTION**

If damage to any of the components is noted, do not install. Immediately inform the carrier and DILOG.

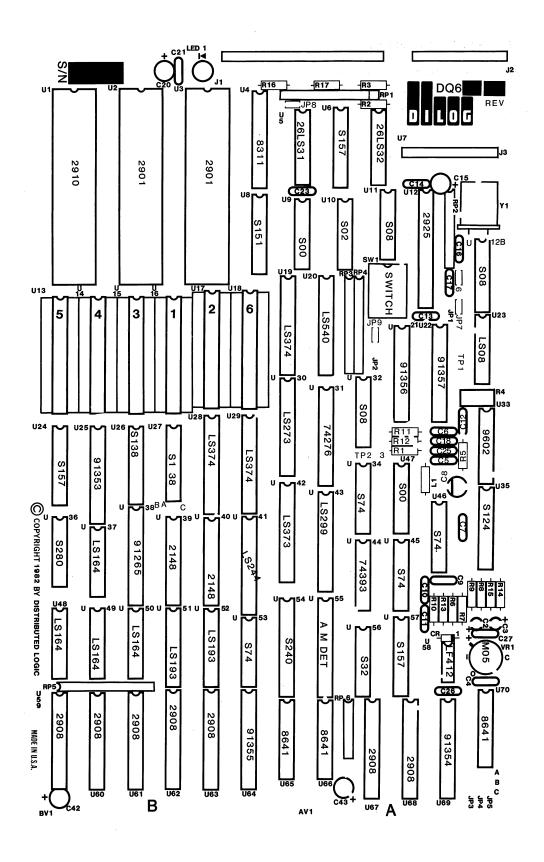

Installation instructions for the disc drive are contained in the disc drive manual. Before installing any components of the disc system, read Sections 1, 2 and 3 of this manual. Figure 2-1 illustrates the configuration of the controller. Table 2-1 lists the configuration switch setting, and Table 2-2 lists component and jumper options. Ensure the board is properly configured before installing.

### PRE-INSTALLATION CHECKS

There are various LSI-11 configurations, many of which were installed before DEC made a hard disc available for LSI-11 based systems. Certain configurations require minor modifications before operating the disc system. These modifications are as follows:

- A. If the system contains a REV11-C module, it must be placed closer to the processor module (higher priority) than the controller if the DMA refresh logic on the REV11-C is enabled.

- B. If the 4K memory on the DK11-F is not used and the memory in the system does not require external refresh, the DMA refresh logic on the REV11-C should be disabled by removing jumper W2 on the REV11-C module.

- C. If the system contains a REV11-A module, the refresh DMA logic must be disabled since the module must be placed at the end of the bus (REV11-A contains bus terminator).

- D. If the REV11-C module is installed, cut the etch to pin 12 on circuit D30 (top of board) and add a jumper between pin 12 and pin 13 of D30.

- E. If the system requires more than one backplane, place the REV-11 terminator in the last available location in the last backplane.

### INSTALLATION

To install the controller module, proceed as follows:

### CAUTION

Remove DC power from mounting assembly before inserting or removing the controller module.

Damage to the backplane assembly may occur if the controller module is plugged in backwards.

Select the backplane location into which the controller is to be inserted. Be sure that the disc controller is the lowest priority DMA device in the computer except if the DMA refresh/bootstrap ROM option module is installed in the system. The lowest priority device is the device farthest from the processor module. Note that the controller contains a bootstrap ROM.

### NOTE

The controller may be inserted into any A-B connector slot, all of which are Q-bus slots. On some backplanes, C-D slots may be Q-bus slots or may be interconnect slots. Before inserting the controller in any C-D slot, check the appropriate DEC documentation.

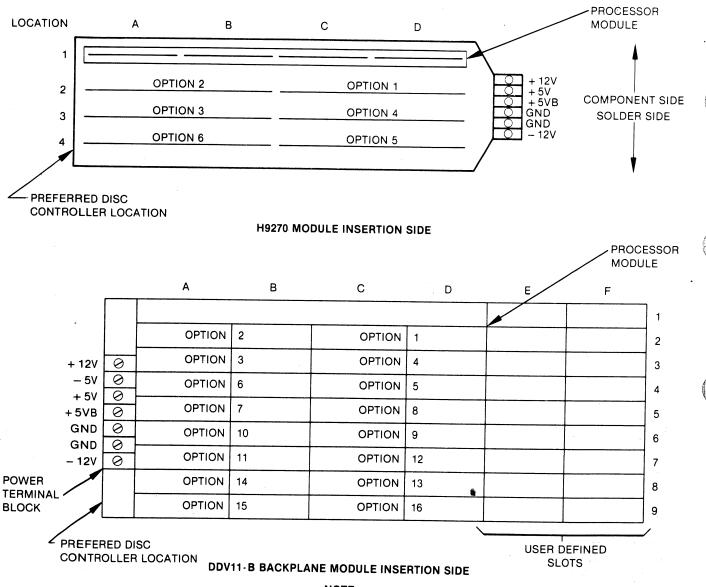

There are several backplane assemblies available from DEC and other manufacturers. Figure 2-2 shows typical backplane configurations. Note that the processor module is always installed in the first location of the backplane or in the first location in the first backplane of multiple backplane systems.

It is important that all option slots between the processor and the disc controller be filled to ensure that the daisy-chained interrupt (BIAK) and DMA (BDMG) signal be complete to the controller slots. If there must be empty slots between the controller and any option boards, the following backplane jumpers must be installed:

| FROM                     | то                 | SIGNAL               |

|--------------------------|--------------------|----------------------|

| C0 × N2<br>C0 × S2       | C0 × M2<br>C0 × R2 | BIAK1/L0<br>BDMG1/L0 |

| Last Full<br>Option Slot | Controller Slot    |                      |

Figure 2-1. Controller Configuration

**Table 2-1. Configuration Switches**

| SWITCH     | POSITION | DESCRIPTION                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| S1         | ON       | The ECC syndrome is saved during a read operation. Upon detection of an error, the controller can use the syndrome to determine if the error is correctable. If correctable, the controller will transparently correct the error.                                                                                 |  |  |  |  |

|            | OFF      | he ECC syndrome is discarded during a read operation. Upon detection of an rror, the controller will determine that the error is uncorrectable (because of the ack of proper syndrome). This mode should be used by the operator when unning diagnostics, so that all media flaws can be detected and mapped out. |  |  |  |  |

| S2         | ON       | Controller bootstrap enabled.                                                                                                                                                                                                                                                                                     |  |  |  |  |

|            | OFF      | Controller bootstrap disabled.                                                                                                                                                                                                                                                                                    |  |  |  |  |

| S3, S4     |          | Identify, to the microprocessor, the last logical RL unit that exists on physical drive zero:                                                                                                                                                                                                                     |  |  |  |  |

|            |          | SW3 SW4 PHYSICAL ZERO PHYSICAL ONE                                                                                                                                                                                                                                                                                |  |  |  |  |

|            |          | OFF OFF DL0 DL1, DL2, DL3 OFF ON DL0, DL1 DL2, DL3 ON OFF DL0, DL1, DL2 DL3 ON ON DL0, DL1, DL2, DL3                                                                                                                                                                                                              |  |  |  |  |

| <b>S</b> 5 | ON       | Controller assumes alternate address for bootstrap ROM of 175 000. (Must be used for LSI 11/23 plus CPU, module M8189.)                                                                                                                                                                                           |  |  |  |  |

|            | OFF      | Controller assumes primary address for bootstrap ROM of 173 000                                                                                                                                                                                                                                                   |  |  |  |  |

When shipped from the factory, all switches will be off if the order is for a controller only. If the order is for drive integration, the switches will be set for that configuration.

Table 2-2. Component and Jumper Options

| OPTION                    | LOCATION  | DESCRIPTION                                                                                                                                     |  |  |  |

|---------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Special Bootstrap*        | U38       | PROM—allows the user to incorporate bootstrap programs not supported by DILOG.                                                                  |  |  |  |

| Loop back data stream     | U22-U23   | JP1—Jumper removed (etch cut) forces the write logic to create a data stream which can be looped back into the read logic. Troubleshooting aid. |  |  |  |

| Abort Precompensation     | U32       | JP2—Jumper removed (etch cut) aborts the controller precompensation logic when writing data. Troubleshooting aid.                               |  |  |  |

| Interrupt Level           | U70       | JP3, JP4, JP5—This option consists of cutting etches and installing wires. For the interrupt levels, the jumpers are connected as follows:      |  |  |  |

|                           |           | JP3 JP4 JP5                                                                                                                                     |  |  |  |

|                           | *         | Interrupt Level 4 B-C B-C B-C Interrupt Level 5 B-C B-C A-B Interrupt Level 6 B-C A-B B-C Interrupt Level 7 A-B A-B B-C                         |  |  |  |

| Drive 0 Cartridge Changed | JP6 (U22) | Must be removed.                                                                                                                                |  |  |  |

| Drive 1 Cartridge Changed | JP7 (U22) | Must be removed.                                                                                                                                |  |  |  |

| Enable Sector Pulse       | JP8 (U5)  | Must be removed.                                                                                                                                |  |  |  |

| Enable Switches 3 and 4   | JP9 (U32) | Must be installed.                                                                                                                              |  |  |  |

| Read Postamble            | JP (U32)  | JUMPER A-B Must be installed A-C Must be removed                                                                                                |  |  |  |

<sup>\*</sup>If the special bootstrap option is required, the sales order should indicate this. The loop back data stream and abort precompensation will not have the etch cut when shipped. The interrupt level shipped from the factory is Level 5, Address 160.

2. To the controller connectors, install cables J1, J2, and J3, respectively. Ensure the pin 1's are oriented as shown in the illustration.

### Note

It may be necessary to remove the strain relief bar on the J3 cable to install the connector.

3. Gently position the module slot connectors into the backplane and press until the connectors are firmly seated into the backplane.

- Apply equal pressure to both sides of the controller when installing or removing.

- 4. Route the cables to the drive; assure pins are properly aligned; and connect the cables. Ensure that the bus terminator is installed in the last drive in the system.

- 5. Refer to the disc drive manual, the computer manual, and Section 3 of this manual, for operating instructions.

MEMORY CAN BE INSTALLED IN ANY SLOT; IT IS NOT PRIORITY DEPENDENT AND DOES NOT NEED TO BE ADJACENT TO THE PROCESSOR.

CONTROLLERS ARE ALSO COMPATIBLE WITH H9273A MODULES.

Figure 2-2. Typical Backplane Configuration

### SECTION 3 OPERATION

### INTRODUCTION

This section contains procedures for operating the computer system with the controller and a disc drive or drives. An understanding of DEC operating procedures is assumed.

## PRECAUTIONS AND PREOPERATIONAL CHECKS

The following precautions should be observed while operating the system. Failure to observe these precautions could damage the controller, the disc, the computer, or could erase a portion or all of the stored software.

- 1. Ensure all switches listed in Table 2-1 are properly set.

- 2. Ensure all jumpers listed in Table 2-2 are properly installed.

- 3. Verify that the controller board is firmly seated in the backplane connection.

- 4. Verify that the cables are properly installed in the controller and in the disc drive.

- 5. Apply power to the drive, the computer and the terminal.

- 6. Verify that the green diagnostic LED on the edge of the controller board lights.

### **BOOTSTRAP SWITCHES**

When switch 2 is on (closed), the controller bootstrap is enabled. The DILOG program will boot the system for RL01/RL02 or RX02 Floppy disc dual density. When switch 2 is off (open), the bootstrap is disabled, and the controller will boot from the standard DEC REV-11 module.

When switch 5 is on (closed), the controller will assume the alternate address 175000 for the bootstrap ROM. When switch 5 is off (open), the controller will assume the primary address 173000 for the boostrap ROM

### Note

If a system has more than one device with bootstrap capabilities enabled, the bootstraps must be at different addresses.

### BOOTSTRAP PROCEDURE

The following assumes the system is in ODT mode. Note that the bootstrap can be used under processor Power Up Mode 2 conditions. Refer to the appropriate DEC manual for a discussion of the Power Up Modes. Further note that the disc drive does not need to be READY to enter the bootstrap.

Reset the system by pressing RESET or enter the following (characters underlined are output by the system; characters not underlined are input by the operator):

- @ 173000G or 175000G Depends on switch and jumper configuration above.

- \* Respond for appropriate logical unit with DY0 or DY1 <CR> for RX02 or DL0, DL1, DL2 or DL3 <CR> if RL01/RL02.

### FORMAT AND TEST PROGRAMS

To format the disc, the operator identifies the drive type, the emulation (RL01 or RL02) and the alternate cylinders required, and the program basically does the rest. For testing, the operator identifies the test and the unit, and the program exercises the system.

To run the program, load the medium and enter R DQ614 after the program is loaded. The following will appear:

ARE YOU RUNNING THE DIAGNOSTIC VIA A CRT. (Y OR N)?

ENTER NUMBER OF DRIVES ON SUB-SYSTEM (1 OR 2)?

If the answer to the first question is no, the program will not list current cylinder addresses (a printout, for example, would be too extensive). To the second question, answer 1 or 2. The disc drive menu will appear next listing a sequential number, the name of the manufacturer and the model number. The following will also appear:

XXX DRIVE (0 or 1) XXX

ENTER THE NUMBER CORRESPONDING TO THE DISC DRIVE.

OR

The number to be entered is the sequence number on the list not the model number. Manufacturers and models are listed below. Select the next page of the menu by pressing N or the previous page by pressing P.

If the drive to be formatted is not listed in the menu, press E and the following will appear:

ENTER NUMBER OF HEADS (D)

ENTER NUMBER OF CYLINDERS(D)

REDUCE WRITE CURRENT AT CYLINDER (NOT USED) Default <CR>

START PRECOMPENSATION AT CYLINDER (NOT USED)

ENTER NUMBER CORRESPONDING TO PROPER STEP RATE:

1 = 26 US

2 = 280 US

3 = 2.1 MS

4 = 3.0 MS

The information above is taken from the manufacturer's specifications. Head and cylinder number are entered in decimal (D). Write current and precompensation requests do not require responses for all drives. If no response is required, press the carriage return for an answer. For the step rate, enter the sequence number and not the timing value.

After the drive is selected, the disc configuration will be selected:

## DISC CONFIGURATION XXX DRIVE 0 XXX

## ENTER NUMBER CORRESPONDING TO THE TYPE OF RL UNIT

1 = RL01 (10240 Blocks; XXX CYLINDERS) 2 = RL02 (20480 Blocks; XXX CYLINDERS)

(XXX) = CYLINDERS NOT YET ALLOCATED

### YOU HAVE XXX CYLINDERS

USE THE <TAB> TO ENTER

TYPE OF RL UNIT

# CARRIAGE RETURN COMPLETES CONFIGURATION PROCEDURE

DL0: ( ) DL1: ( ) DL2: ( ) DL3:

Use the tab when entering the type of RL unit (1 or 2). Use the carriage return to exit after a physical drive is partitioned. The program will automatically calculate the number of cylinders remaining after the selection of the RL unit. The operator has the option of selecting a truncated unit or allocating the remaining cylinders as alternates, or a combination of both. If the remainder is less than 1 megabyte, the program automatically allocates the remainder as alternates. The alternate cylinders that are allocated are for the physical drive and not the logical unit. The operator allocates the alternate

cylinders and the program calculates and allocates the truncated unit. The following is an example:

The first logical unit is to be an RL01 and there are 65 cylinders remaining, 5 of which are to be alternates and 60 truncated. The following underlined numbers or keys are entered:

# ENTER NUMBER OF ALTERNATE CYLINDERS (D)? 5 < CR >

### Note

If there is no tab on the terminal, use control I.

If two drives are selected, the cursor may appear at DL1, DL2, or DL3, depending upon how many logical units are selected. In the previous example, if two drives are selected, the cursor will be positioned at DL2.

A truncated unit of 60 cylinders will appear in DL1. The following will appear:

When all logical units are partitioned, the summation message will be similar to the following:

### DISC SUBSYSTEM CONFIGURATION

| LOGICAL | <b>PHYSICAI</b> | _                | RECORD |

|---------|-----------------|------------------|--------|

| UNIT    | DRIVE           | <b>MEGABYTES</b> | SIZE   |

| DL0     | 0               | 10.48            | 20480  |

| DL1     | 0               | 4.17             | 8160   |

| DL2     | 1               | 5.24             | 10240  |

| DL3     | 1               | 5.24             | 10240  |

PHYSICAL DRIVE 0 HAS 30 ALTERNATE TRACKS

PHYSICAL DRIVE 1 HAS 54 ALTERNATE TRACKS

SET SWITCH 3 OFF SET SWITCH 4 ON

ARE YOU SURE (Y OR N)?

Partitioning is then completed.

10. CMI 5640

The following is a partial list of manufacturers and model numbers that can be formatted:

1. AMPEX PYXIS 8 11. EVOTEK ET-5510 2. AMPEX PYXIS 13 12. ET-5520 3. AMPEX PYXIS 16 13. ET-5530 4. AMPEX PYXIS 20 14. ET-5540 5. AMPEX PYXIS 27 15. FUJITSU M2231A 6. COMPUTER 16. FUJITSU M2232A MEMORIES CMI-5410 17. INTERNATIONAL 7. CMI 5412 **MEMORIES IMI-5006** 8. CMI 5616 18. IMI-5006H 9. CMI 5619 19. IMI-5012H

20. IMI-5018H

21. MINISCRIBE 1006 46. RMS/DISCTRON 519 22. MINISCRIBE 1012 47. RMS/DISCTRON 526 23. MINISCRIBE 3006 48. SEAGATE ST406 24. MINISCRIBE 3010 49. SEAGATE ST412 25. MINISCRIBE 4010 50. SEAGATE ST419 26. MINISCRIBE 4020 51. SEAGATE ST506 27. MITSUBISHI 4861 52. SHUGART SA602 28. MITSUBISHI 4862 53. SHUGART SA604 29. MITSUBISHI 4863 54. SHUGART SA606 30. OLIVETTI HD562/11 55. SYQUEST SO306 31. RODIME 102 **56. TANDON 602E** 32. RODIME 104 **57. TANDON 602S** 33. RODIME 202 **58. TANDON 603E** 34. RODIME 203 35. RODIME 204 **59. TANDON 603S** 60. TEXAS INSTRU-36. RODIME 206 **MENTS TI-506** 37. RODIME 208 61. TI-525/61 38. RMS/DISCTRON 503 62. TI-525/122 39. RMS/DISCTRON 504 63. ATASI 3020 40. RMS/DISCTRON 506 64. ATASI 3033 41. RMS/DISCTRON 509 65. ATASI 3046 42. RMS/DISCTRON 512 66. OLIVETTI HD562/13 43. RMS/DISCTRON 513 **67. MEMOREX 306**

**68. MEMOREX 310**

44. RMS/DISCTRON 514

45. RMS/DISCTRON 518

### DIAGNOSTIC TEST PROGRAM

The format/test program contains the following:

- 1. TEST CONTROLLER

- A. Registers

- B. Data Buffer

- 2. TEST DISC DRIVE

- A. Disc Ready

- B. Disc Restore (seek to cylinder 0)

- 3. FORMAT

- A. Write Headers

- B. Read Headers

- C. Write Data Test Pattern

- D. Read Data Test Pattern

- 4. SEQUENTIAL READ

- 5. SELECTED READ

- 6. RANDOM SEEK, READ

- 7. RANDOM SEEK, WRITE, READ, AND COMPARE

- 8. TEST ECC LOGIC

- 9. ASSIGN ALTERNATE TRACK

### **Test Controller**

The program will automatically test the controller registers and data buffer. The program will only display error messages during this test; the display will be:

### DATA BUFFER ERROR

or the mnemonics of the seven controller registers, the location and contents (in Octal). The display of the registers is followed by a 4-line message to aid in isolating the specific problem.

### Note

Whenever an error occurs and the registers are displayed, an audio alarm signal is generated to notify the operator.

The 4-line message is as follows:

| DISC ADDRESS HE      | AD |

|----------------------|----|

| CYLINDER             |    |

| TYPE OF COMMAND      |    |

| CONTROL STATUS ERROR |    |

| DRIVE STATUS         |    |

"DISC" lists the head and cylinder (in decimal) where the error occurred. An example of Type of Command is Read Data Command. An example of Control Status is Seek Error. The Drive Status will display:

USE C TO CONTINUE

USE O TO TRANSFER TO ODT

USE L TO REBOOT YOUR SYSTEM

"C" is used to continue the test. "O" is used for ODT (on-line debugging technique), "L" is used to initiate the system bootstrap.

#### Test Disc Drive

After the controller test is performed, the program will automatically test the drive for ready and restore. The disc address is not displayed during this test.

#### **Format**

The operator may either select logical units sequentially or select one or more specific logical units to be formatted. Program messages are presented for formatting in logical unit number sequence, i.e.:

FORMAT DL0 (Y OR N)? FORMAT DL1 (Y OR N)? FORMAT DL2 (Y OR N)? FORMAT DL3 (Y OR N)?

FORMAT ALTERNATE CYLINDERS (DRIVE 0 OR DRIVE 1)

### Note

Before any write operation, the program will display ARE YOU SURE? This aids the operator in preventing reformatting of a previously formatted logical unit (possibly destroying good data).

During formatting, the following messages will appear sequentially:

| WRITING HEADERS CURRENT CYLINDER ADDRESS          |

|---------------------------------------------------|

| READING HEADERS CURRENT CYLINDER ADDRESS          |

| WRITING DATA TEST PATTERNCURRENT CYLINDER ADDRESS |

| READING DATA TEST PATTERNCURRENT CYLINDER ADDRESS |

When reading and writing headers, the program will display the cylinder addresses sequentially. The test pattern tests are also sequentially selected, and the cylinder address displayed will correspond to current address being read.

After each logical unit is formatted, the display will be:

DL\_\_\_\_ FORMAT AND VERIFICATION COMPLETE

### Sequential Read

For this test, the display will be:

## SEQUENTIAL READ (ALL CYLINDERS AND HEADS?)

If the response is No, the program will jump to the Selected Read test. If the response is Yes, the current cylinder address is displayed as each cylinder is read. If an error is detected, the register contents and location are displayed with the 4-line identification message, and the following:

## ASSIGN ALTERNATE TRACK FOR DEFECTIVE TRACK?

If no alternates (spares) are available, the following will be displayed:

### NO ALTERNATE CYLINDER AVAILABLE

When marking or assigning alternate tracks, the following error messages may occur:

TRACK HAS ALREADY BEEN MARKED DEFECTIVE TRACK HAS ALREADY BEEN MARKED ALTERNATE

### **Selected Read**

For this test, the display will be:

READ DLO (Y OR N)?

If the response is No, the next logical unit will be displayed. If the response is Yes, the current cylinder address is displayed and each cylinder is read. If an error is detected, the register contents and location are displayed with the 4-line identification message. The ASSIGN ALTERNATE TRACK message appears, and error messages if the track has been marked DEFECTIVE or ALTERNATE.

### Random Seek, Read

For this test, the display will be:

## RANDOM SEEK, READ OF DRIVE (ALL CYLINDERS AND HEADS)?

This test selects a random cylinder, logical unit, and a sector address within the cylinder. The test then reads data and tests for errors. All logical units are used in this test. Alternate cylinders cannot be assigned during this test. The terminal keyboard space (SP) character is used to exit this test.

If an error is detected, the register content and locations are displayed with the 4-line identification message.

This check also ensures controller mapping is correct.

## Random Seek, Write Data, Read Data, Compare Test

If the response is No, each logical unit will appear in sequence until the response is Yes:

DL0?

DL1?

DL2?

DL3?

This test selects a random cylinder address and random sector address and writes five sectors (2560 bytes) of random data. The data written is then read into CPU memory and compared for read errors. This test allows logical units to be tested. The terminal keyboard space character (SP) is used to exit from this test.

This test ensures that the controller is executing the write check command correctly and ensures that the controller is zero-filling the disc correctly.

### **Test ECC Logic**

The following message will appear for this test:

TEST ECC?

DL0:?

DL1:?

DL2:?

DL3:?

ARE YOU SURE?

If ECC testing is selected, answering "Y" to "TEST ECC?" the program will prompt the operator to specify a unit. The unit selected will then be used to test the ECC logic.

### Note

The unit selected will be written on.

The program selects whether a correctable or noncorrectable error is to be programmed; then the program creates an error; writes the sector with the error to the disc; reads to memory; then the program decides whether the error is noncorrectable or correctable.

If noncorrectable, the program checks to ensure an error has been returned by the controller.

If correctable, the program checks to make sure there has been no error returned by the controller, and checks to ensure the error was corrected in the proper manner. If this test fails, the message is one or more of the following:

CONTROLLER INDICATES CORRECTABLE ERROR

CONTROLLER INDICATES NONCORRECT-ABLE ERROR

ERROR BURST IS CORRECTABLE

# ERROR BURST IS NONCORRECTABLE ERROR BURST WAS NOT CORRECTED

The space character (SP) is used to exit from this test.

### Assign Alternate Track

This test may be used if the disc drive manufacturer provides a map describing defective tracks. The message is:

ASSIGN ALTERNATE TRACK FOR DEFECTIVE TRACK (Y OR N)?

If the response is No, the program will revert to:

USE R TO REPEAT

USE O TO TRANSFER TO ODT

USE L TO REBOOT YOUR SYSTEM

If the response is Yes, the display will be: PHYSICAL DRIVE (0 or 1)? (Only if two drives are present)

CYLINDER ADDRESS (0 TO \_\_\_\_)

Enter the cylinder address, in decimal, of the defective track. If the cylinder address entered is incorrect, the message will be repeated.

| The next message will be: |   |

|---------------------------|---|

| HEAD ADDRESS (0 TO        | ) |

Enter the head address, in decimal, of the defective track. If the head address entered is incorrect, the message will be repeated.

The next message will be:

MAP OUT

CYLINDER \_\_\_\_\_ HEAD \_\_\_\_

ARE YOU SURE? (Y OR N)

If No, the program will repeat the first message of this test. If Yes, an alternate cylinder is assigned and the message is:

ALTERNATE CYLINDER ASSIGNED

Other messages to appear may be:

TRACK ALREADY MARKED DEFECTIVE or

TRACK ALREADY MARKED ALTERNATE

The program will then repeat the first message of this test.

### SECTION 4 PROGRAMMING

### PROGRAMMING DEFINITIONS

Function — The expected activity of the disc system (write, seek, read, etc.).

Command — To initiate a function (halt, clear, go, etc.)

Operations — One or more orders executed in a prescribed sequence that causes a function to be performed.

Address — The binary code placed in the BDAL0-15 lines by the bus master to select a register in a slave device. Note memory other than computer internal memory, i.e., peripheral device registers, the upper 4K (28-32K) address space is used.

Register — An associated group of memory elements that react to a single address and store information (status, control, data) for use by other assemblies of the total computer system.

### **OPERATIONS**

WRITE—When the controller is given a write command it will perform the mapping algorithm, do an implied seek if one is necessary, and then do the write operation. The controller will perform spiral operations until the word count is exhausted, unlike the real RL controller.

READ—The read is performed like the write, except for the direction of data flow.

RESTORE—The real RL controller does not have an implicit restore command, so the restore operation has been incorporated into the "Get Status" command. When a "Get Status" is performed, and bit 4 of the RLDA register is set, the selected disc drive will be positioned to track zero.

WRITE FORMAT—When a write command is issued to the controller and bit 15 of the RLMP register is a zero, the write data command will be changed to a write format command.

Format commands read/write a fixed buffer size of 51 words. The format commands start and end at the index signal from the disc. There are 3 words from the table for each of the 17 headers in a track. The physical position of a header in the table determines its physical position in the track.

When a read/write command is issued with bits 15 and 14 reset, the firmware responds to this as a format command with inhibit seek. The firmware will perform the desired format command on the head addressed by the RLDA in map override form, but will not do any seek previous to the command.

When read/write command is issued with bits 15 reset and bit 14 set, the firmware responds to this as a format command with seek and map override. The firmware will use the RLDA as real head and cylinder addresses, will seek to the desired position in the disc and perform the desired read/write format function.

The general flow of a program to format the disc is of a 4 pass operation. In pass one the headers are written, and the controller erases all the data fields. In pass two the headers are verified. In pass three the disc data fields are written and in pass four the data fields are verified.

The initial command in the formatting program is to do a restore on the physical unit. The restore command does not require any cylinder calculations, so it can be performed on an unformatted disc drive.

When the drive has been restored to track zero, then head zero can be written with a write format/inhibit seek. This command, since it also does no cylinder calculations can be performed on an unformatted disc drive.

Once cylinder zero, head zero has been formatted, then commands with seeks can be performed.

READ FORMAT—When a read command is issued to the controller and bit 15 of the RLMP is a zero, the read data command will be changed to a read format command.

SEEK—Since the physical characteristics of the disc do not match the RL01/RL02 it is emulating, the normal seek command is essentially worthless and does no operation on the real disc. All read/write commands are preceded with an implied seek operation that is performed by the firmware. Whenever the firmware is required to do an implied seek, it will verify its new disk position (format commands excepted). An implied seek will also occur when a command continues across a real disc cylinder boundary.

The implied seek operation consists of reading the first available header. The firmware then calculates the difference in real cylinders between its present position, and the desired position. The firmware then issues step pulses to the disc at timed intervals. When the heads have settled at the new cylinder, a header is read and the cylinder address is verified by firmware to be correct.

WRITE CHECK—The command begins like a read command, and finds the requested sector on the disc, and reads it into the controller's data buffer. The firmware will then DMA data from the

computer and compare the data against the data in the buffer. A miscompare will set the data error status.

CONTROLLER CLEAR—The command will clear the RLBA and RLAE and RLDA registers and the error status in the RLCS register. The RLMP most significant byte will be cleared, then bits 15 and 14 set (to avoid accidental format commands). The RLMP least significant byte will be loaded with the revision number of the microcode. This command duplicates the effects of a bus initialization, except the microcode does not do the self test.

WRITE DIAGNOSTIC MODE—The command is restricted to a one sector operation. It is also to be done only on the last physical sector in a track. The command is a write data command with bit 14 of the RLMP cleared. The word count is to be one sector plus 2 words. The RLMP value is then octal 137376. The command will write the data buffer and instead of appending the 32 bit controller generated ECC check character to the end of the buffer, it will write the last two words of the data buffer as the ECC characters.

READ DIAGNOSTIC MODE—The command is restricted to a one sector operation. There is no restriction on the disc address. The data buffer passed to memory will begin with the third word of the data field. The last two words of the data buffer will contain the ECC check character read from the disc. The data error status is indeterminate during this command, and should be ignored.

### **INTERRUPTS**

The controller will interrupt after commands complete if bit 6 of the RLCS is set. Note that doing a BIS of bit 6 to the RLCS does not give an interrupt, as in some other controllers.

### DIAGNOSTIC

The diagnostic is named DQ614, available from the software department. The revision of the diagnostic will be displayed on the startup message.

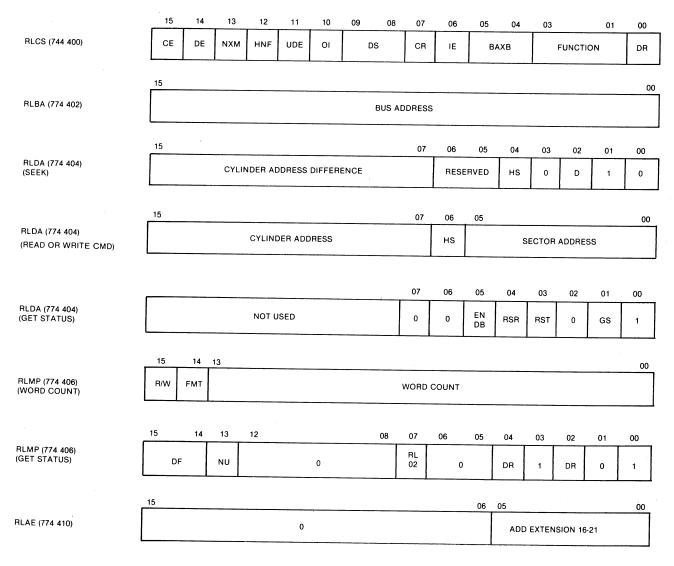

Figure 4-1. Register Summary

## Control/Status Register 774 400 (RLCS)

The Control/Status Register (RLCS) has the bus address 774 400. The purpose of the register is to

pass commands to the controller, and to pass status back to the program.

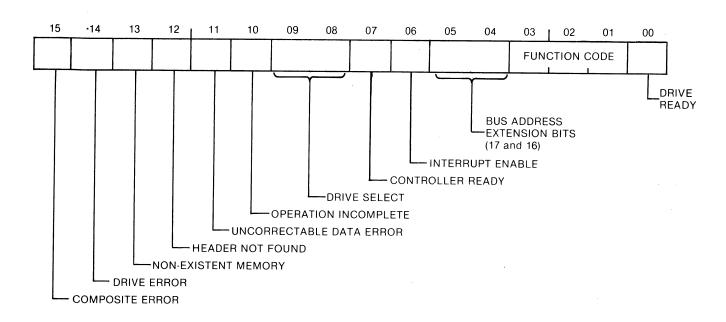

### BIT(S) DESCRIPTION

DRIVE READY—When set, indicates drive is ready.

01, 02, 03 FUNCTION CODE—The function code is a three bit field that defines one of eight possible commands to the controller.

COMMAND 0 Controller Reset—This command will reset the controller and the internal flags.

(0 0 0) At the completion of the command the revision number of the microcode will be in the LSB of the multipurpose register. This command is similar to the Bus Initialization signal except that the "INIT" signal also causes the microprocessor to perform its self test.

COMMAND 1 Write Check—This command will compare a table in memory against the data on the disc. A miscompare will set the uncorrectable error status. The controller will not perform error correction on the data read from the disc.

COMMAND 2 Get Status—This command is used to obtain the drive status, restore the disc, and Read/Write into the controller data buffer for diagnostic purposes. The exact operation is determined by bits in the RLDA Register.

COMMAND 3 Seek—This command will present status to the program to indicate a seek is performed, but no action will really take place. The controller functions with transparent seeking taking place after the mapping algorithm is performed, so this command is essentially a NO-OP.

COMMAND 4

(1 0 0)

Read Headers—This command will present status to the program to indicate a read headers is performed but no action will really take place. The software uses this command in conjunction with the seek command, which is also essentially a NO-OP as this one.

COMMAND 5 Write Data—This command will write data blocks onto the disc. Alternately if bit 15 of the multipurpose register is a zero, the command will write headers onto the disc, and erase the data fields (a write format command).

COMMAND 6 Read Data-This command will read data blocks from the disc. Alternately if  $(1\ 1\ 0)$ bit 15 of the multipurpose register is a zero, the command will read headers from the disc. (A read format command.) COMMAND 7 Read Data-This command will function as command six, but if command six  $(1\ 1\ 1)$ encounters an uncorrectable data field it will stop, and not transfer bad data. This command will transfer the bad data before halting the operation. BUS ADDRESS EXTENSION BITS (17 and 16)—These bits are Bus Extension bits 17(5) and 04, 05 16(6). These are identical to bits 1 and 0 of RLAE Register and can be set by writing into either register. These bits increment everytime the RLBA Register overflows. 06 INTERRUPT ENABLE—When set, this bit allows the controller to interrupt the processor at the end of an operation. CONTROLLER ENABLE—When cleared by the software, this bit indicates that the controller 07 is to start an operation. When set by the controller, this bit indicates that the controller is ready to accept another command. 08-09 DRIVE SELECT-These bits determine which of four logical units is selected. 10 OPERATION INCOMPLETE-The Operation Incomplete status when set, indicates that the controller passed the initial requirements to start the operation, but that an error was encountered during operations. 11 UNCORRECTABLE DATA ERROR-The ECC Error Status when set, indicates that the controller has made two attempts to read the data and has been unable to correct the error. Refer to Table 2-1 for the implications of Switch one on this status. 12 HEADER NOT FOUND—The Header Not Found status when set, indicates that the controller has searched the data track for three spins of the disc and has not been able to locate the desired data block. NON-EXISTENT MEMORY—The Non-Existent Memory status when set, indicates that dur-13 ing a DMA cycle the controller as Bus Master, did not receive a response from the memory addressed within 20 us. 14 DRIVE ERROR-The Drive Error bit when set, indicates the controller has determined that there exists a problem in the drive that will not allow the command to proceed further. This bit can be set if the controller determines that (1) The drive has gone "NOT READY", (2) The drive fault line goes true, (3) The drive selected status from the drive goes false during a command, (4) During any transparent seek operation if the controller detects a positioning error during its verify positioning cycle, (5) If the continuation of an operation will attempt to exceed the end of a logical unit.

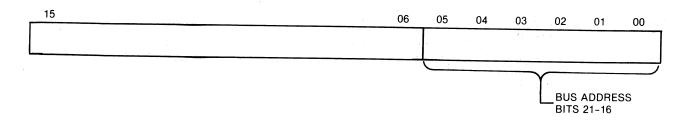

# BUS ADDRESS REGISTER (RLBA) 774 402

| 15    |  | 00 |

|-------|--|----|

|       |  |    |

|       |  |    |

| ( ) · |  |    |

|       |  |    |

COMPOSITE ERROR-The Composite Error bit when set, indicates that one or more of the

The address of RLBA is 774 402. The bits of this register contain the bus address of data transferred during read or write check operations. The register is incremented by two at the end of each transfer. If

error bits (14-10) is set.

the system has extended memory, the RLBA will overflow to the EX MEM bits (04, 05) of the RLCS to reflect the extended bus address. This is a read/write register cleared by INIT or RESET functions.

15

## DISC ADDRESS REGISTER 774 404 (RLDA)

The Disc Address register has the bus address of 774 404. The purpose of the register is to pass disc addresses to the controller.

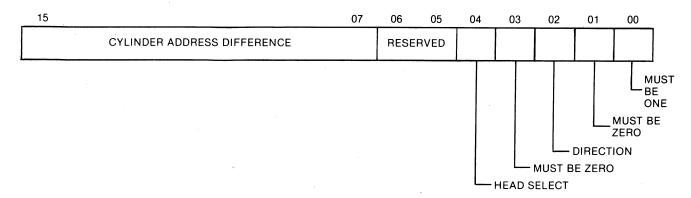

### RLDA on a SEEK command.

| BIT(S) | DESCRIPTION                                                                                                                                                                                                         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00     | Must be 1                                                                                                                                                                                                           |

| 01     | Must be 0                                                                                                                                                                                                           |

| 02     | DIRECTION—This bit indicates the direction in which a seek is to take place. When the bit is set, the heads move to a higher cylinder address. When the bit is cleared, the heads move to a lower cylinder address. |

| 03     | Must be 0                                                                                                                                                                                                           |

| 04     | HEAD SELECT—This bit indicates which head (disc surface) is to be selected. Set=lower, clear=upper.                                                                                                                 |

| 05-06  | Reserved                                                                                                                                                                                                            |

| 07-15  | CYLINDER ADDRESS DIFFERENCE—These bits indicate the number of cylinders the heads are to move on a seek.                                                                                                            |

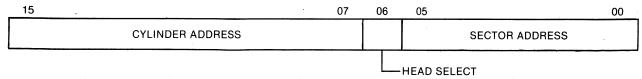

# RLDA on a READ or WRITE data command. (RL01/RL02 Disc Address)

| BIT(S) | DESCRIPTION                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------|

| 00-05  | SECTOR ADDRESS—These bits indicate the addressed sector.                                            |

| 06     | HEAD SELECT—This bit indicates which head (disc surface) is to be selected. Set=lower, clear=upper. |

| 07-15  | CYLINDER ADDRESS—These bits indicate the address of the cylinder being accessed.                    |

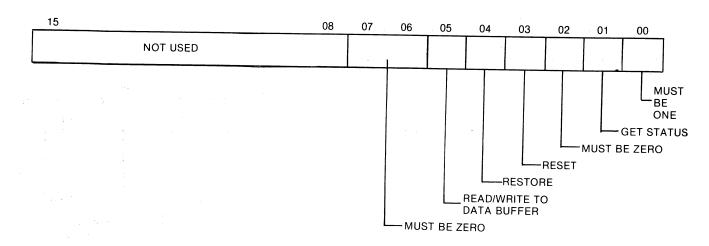

## RLDA on a GET STATUS command.

| BIT(S) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00     | Must be 1                                                                                                                                                                                                                                                                                                                                                 |

| 01     | GET STATUS—When set, enables status to be put into the Multipurpose Register by Get Status function code.                                                                                                                                                                                                                                                 |

| 02     | Must be 0                                                                                                                                                                                                                                                                                                                                                 |

| 03.    | RESET—When set, causes the drive to clear its Error Register before sending a status word to the Controller.                                                                                                                                                                                                                                              |

| 04     | RESTORE—When set, this bit causes the heads to return to cylinder 0.                                                                                                                                                                                                                                                                                      |

| 05     | READ/WRITE TO DATA BUFFER—When set on a get status command, allows access to the controller internal data buffer. When the programmer outputs a word to the Multipurpose Register it will be written into the internal data buffer. When the programmer inputs a word from the Multipurpose Register the word will be read from the internal data buffer. |

| 06-07  | Must be 0                                                                                                                                                                                                                                                                                                                                                 |

| 08-15  | Not Used                                                                                                                                                                                                                                                                                                                                                  |

# MULTIPURPOSE REGISTER 774 406 (RLMP)

The Multipurpose register has the bus address of 774 406. The purpose of the register is to pass the word count to the controller on a read/write com-

mand, and to pass disc status back to the program on a get status, and to move data into/out of the controller buffer during a diagnostic test.

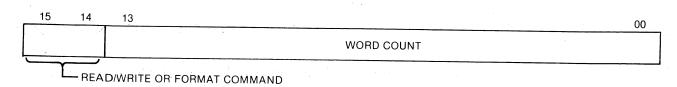

### **During Read/Write Command for Word Count**

### BIT(S) DESCRIPTION

WORD COUNT—These bits are the 2's complement of the total number of words to be transferred during a read, write or write check operation. The register is incremented by one after each transfer. When the register overflows (all WC bits go to zero), the transfer is completed and the controller action is terminated at the end of the current disc sector.

14-15 These bits indicate the following:

15, 14 SET; Read/write data command.

15 SET, 14 CLEAR; Read/write data command with ECC Diagnostic Mode.

15 CLEAR, 14 SET; Format command with seek.

15 CLEAR, 14 CLEAR; Format command with no seek.

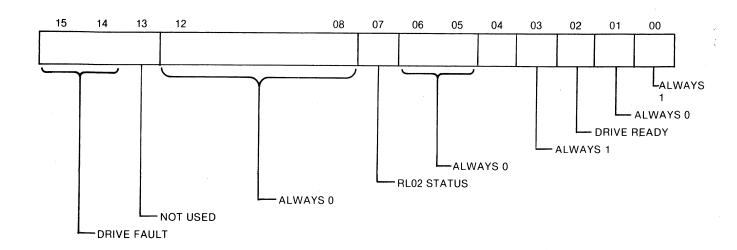

### **During a Get Status Command**

RLMP is used to read/write the data buffer by using the GET STATUS command with bit 5 or RLDA.

| BIT(S) | DEFINITION                                                                                                                                                                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00     | Always 1.                                                                                                                                                                           |

| 01     | Always 0.                                                                                                                                                                           |

| 02, 04 | DRIVE READY—When bits 02 and 04 are set, the drive is ready for operation.                                                                                                          |