# Honeywell

# SYSTEM INITIALIZATION PROGRAM LOGIC MANUAL

SERIES 60 (LEVEL 68)

**MULTICS**

## RESTRICTED DISTRIBUTION

SUBJECT:

Internal Organization of Multics System Initialization.

#### SPECIAL INSTRUCTIONS:

This Program Logic Manual (PLM) describes certain internal modules constituting the Multics System. It is intended as a reference for only those who are thoroughly familiar with the implementation details of the Multics operating system; interfaces described herein should not be used by application programmers or subsystem writers; such programmers and writers are concerned with the external interfaces only. The external interfaces are described in the Multics Programmers' Manual, Commands and Active Functions (Order No. AG92), Subroutines (Order No. AG93), and Subsystem Writers' Guide (Order No. AK92).

As Multics evolves, Honeywell will add, delete, and modify module descriptions in subsequent PLM updates. Honeywell does not ensure that the internal functions and internal module interfaces will remain compatible with previous versions.

This PLM is one of a set which, when complete, will supersede the <u>System Programmers' Supplement to the Multics Programmers' Manual</u> (Order No. AK96).

THE INFORMATION CONTAINED IN THIS COPYRIGHTED DOCUMENT IS THE EXCLUSIVE PROPERTY OF HONEYWELL INFORMATION SYSTEMS. DISTRIBUTION IS LIMITED TO HONEYWELL EMPLOYEES AND CERTAIN USERS AUTHORIZED TO RECEIVE COPIES. THIS DOCUMENT SHALL NOT BE REPRODUCED OR ITS CONTENTS DISCLOSED TO OTHERS IN WHOLE OR IN PART.

DATE:

February 1975

ORDER NUMBER:

AN70, Rev. 0

#### PREFACE

Multics Program Logic Hanuals (PLMs) are intended for use by Multics system maintenance personnel, development personnel, and others who are thoroughly familiar with Multics internal system operation. They are not intended for application programmers or subsystem writers.

The PLMs contain descriptions of modules that serve as internal interfaces and perform special system functions. These documents do not describe external interfaces, which are used by application and system programmers.

Since internal interfaces are added, deleted, and modified as design improvements are introduced, Honeywell does not ensure that the internal functions and internal module interfaces will remain compatible with previous versions. To help maintain accurate PLM documentation, Honeywell publishes a special status bulletin containing a list of the PLMs currently available and identifying updates to existing PLMs. This status bulletin is distributed automatically to all holders of the System Programmers Supplement to the Multics Programmers Manual (Order No. AK96) and to others on request. To get on the mailing list for this status bulletin, write to:

Large Systems Sales Support

Multics Project Office

Honeywell Information Systems Inc.

Post Office Box 6000 (MS A-85)

Phoenix, Arizona 85005

# CONTENTS

|            |                              |         |       |       | Page         |

|------------|------------------------------|---------|-------|-------|--------------|

| Section I  | Overview                     |         |       |       | 11           |

|            | Strategy of Initialization   |         | •     | • •   | 1-2          |

|            | The Segment Loading Table    | (SLT)   | • •   | • •   | 1-4          |

|            | Name Table                   | (551).  | • •   | • •   | 1-12         |

| ,          |                              |         | • •   | •     |              |

|            | Creation of the SLT          | • •     | • •   | • •   | 1-12<br>1-13 |

|            | The Environment Passed to    | • • •   | • •   | • •   | 1-13         |

|            | Initialization               |         |       |       | 4 4 11       |

|            | The Initialization Environ   | mont    | •     | • ' • | 1-14         |

|            | Faults and Interrupts .      | ment.   | • •   | • •   | 1-17         |

| *          | Error Handling               | • •     | • •   | • •   | 1-17         |

|            | Error Handling               | • • •   | • • • | • •   | 1-19         |

|            | Segmentation and Paging      | • • •   | • • • | • •   | 1-20         |

|            | The PL/I Environment .       | • • •   | • , • | • •   | 1-23         |

|            | Traffic Control and Rin      | gs      | • • . | • •   | 1-24         |

|            | I/O Management               | • • •   | • •   | •     | 1-24         |

|            | Memory Management            | • • •   | • •   |       | 1-26         |

|            | Collections                  |         | ·     |       | 1-26         |

|            | Supervisor, Init and Ter     | mp Segs | • •   | •     | 1-27         |

|            | Main Memory Management       |         |       |       | 1-29         |

|            | Summary of Initialization    | Calls.  | • • • | • •   | 1-34         |

| Sootian II | 0.11                         |         |       |       |              |

| Section II | Collection 1                 |         |       |       | 2-1          |

|            | bootstrap!                   |         |       |       | 2-2          |

|            | bootstrap2 and Prelinking.   |         |       |       | 2-5          |

|            | correction   Fault Initial:  | ization |       | •     | 2-8          |

|            | nardcore 1/0 and Operator (  | Console |       |       |              |

|            | Initialization               |         |       |       | 2-10         |

|            | configuration initialization | on .    |       | •     | 2-12         |

|            | Interrupt Configuration      |         |       |       | _ ,_         |

|            | Initialization               |         |       |       | 2-16         |

|            | initializing Page Control.   |         |       | •     | 2-19         |

|            | Setting Up the System Se     | egment  | . · • | •     | - 1)         |

|            | Table (SST)                  |         |       |       | 2-19         |

|            |                              | • •     | · • • | •     | ~- ı j       |

iii

# CONTENTS (cont)

|                                       |                                   | Page        |

|---------------------------------------|-----------------------------------|-------------|

|                                       | Initializing Storage System       |             |

|                                       | Devices and the FSDCT             | 2-22        |

|                                       | The Making Paged of Segments      | 2-25        |

|                                       | Final Initialization of           |             |

|                                       | Collection 1                      | 2-28        |

|                                       | Retrospect on Collection 1        | 2-28        |

|                                       | noticeptor on collection i        | 2-20        |

|                                       |                                   |             |

| Section III                           | Collection 2                      | 2 1         |

|                                       | Collection 2                      | 3-1         |

|                                       | Preliminary Collection 2          | 3-2         |

|                                       | Triticlinations                   |             |

|                                       | Initializations                   | 3-3         |

|                                       | Hardcore and Outer Ring Segment   |             |

| · · · · · · · · · · · · · · · · · · · | Numbers                           | <b>3-</b> 5 |

|                                       | Root Directory Initialization     | 3-9         |

|                                       | Branch Creation and Connection    | 3-11        |

|                                       | Collection 2 Wrapups              | 3-14        |

|                                       | Collection 3                      | 3-14        |

|                                       | Initialization of Traffic Control | 3-15        |

|                                       | Idle Processes                    | 3-18        |

|                                       | Starting Processors               | •           |

|                                       | The Completion of Market C. t.    | 3-19        |

|                                       | The Completion of Traffic Control |             |

|                                       | Initialization                    | 3-22        |

|                                       | User I/O Initialization           | 3-22        |

|                                       | Communications Initialization     | 3-22        |

|                                       | The End of Initialization         | 3-24        |

|                                       | Retrospect on Collection 2        | 3-24        |

|                                       |                                   | <b>J</b>    |

|                                       |                                   |             |

| Section IV                            | Shutdown                          | 4-1         |

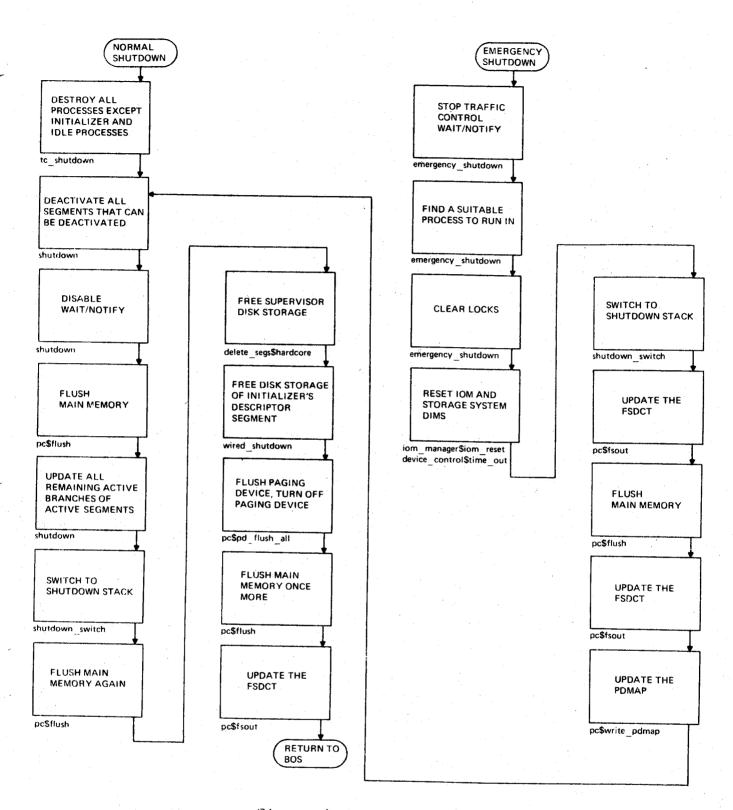

|                                       | Normal Shutdown                   | 4-4         |

|                                       | Normal Shutdown                   | 4-8         |

|                                       | Emergency bridgewith,             | 4-0         |

|                                       |                                   |             |

| Section V                             | Modula Daganintiana               | - 4         |

| DCC010H V                             | Module Descriptions               | 5-1         |

|                                       | Specialized Modules               | 5-1         |

|                                       | Utility Modules                   | 5-5         |

|                                       | delete_segs                       | 5-6         |

|                                       | find                              | 5-7         |

|                                       | freecore                          | 5-8         |

| i i                                   | make_sdw                          | 5-9         |

|                                       | tape_io                           | 5-11        |

|                                       | tane reader                       | J=11        |

iv

# CONTENTS (cont)

Appendix A. abs\_segs.

|                                                               | ILLUSTRATIONS                              |                      |

|---------------------------------------------------------------|--------------------------------------------|----------------------|

|                                                               |                                            |                      |

| Figure 1-<br>Figure 1-<br>Figure 1-<br>Figure 4-<br>Figure 4- | 2. Main Memory before Loading Collection 1 | 1-31<br>1-32<br>1-35 |

Page A-1

### SECTION I

#### OVERVIEW

This Program Logic Manual (PLM) describes the initialization of the Multics system. The term initialization, with respect to Multics, is used to describe the bringing up of the Multics operating system. Multics does not require a generation, "i.e., a creation of a version of Multics tailored to the requirements of a particular installation. Multics tailors itself to installation requirements, as specified on a deck of cards (the CONFIG deck) provided at initialization time (see the Multics Operators' Handbook, Order No. AM81 for details). the Multics System Tape (MST), which contains the Multics system, be used at any site. The operational procedure of taking an MST and loading it (via BOS, the Bootload Operating System; Bootload Operating System (BOS) PLM, Order No. AN74, details) is known as a bootload or boot. At the time of bootload, programs on the Multics System Tape create the Multics environment and read the programs and data on the tape into main memory and virtual memory. Configuration-dependent data processed and system data bases are initialized. The process creating the Multics environment is known as initialization.

This PLM describes the procedures, data bases, strategies, and policies used during Multics system initialization. This is to be distinguished from process initialization, which is the initialization of each Multics process shortly after it is initialization is covered in Process and Process PLM, Order No. AN60. This manual does not Processor <u>Control</u> the initialization of the system control, answering service, and accounting facilities. These facilities described in System and User Control, Order No. AN66 and System Administration, Order No. AN72. Thus, this manual describes only initialization of the hardcore supervisor at system bootload time.

A large part of initialization consists of the initialization of various subsystems within the supervisor. In many cases, this initialization is a crucial part of the operation of an individual subsystem and thus is also covered in some detail in the PLM describing that subsystem. This is particularly true of <u>Storage System</u>, Order No. AN61, <u>Process and Processor Control</u>, Order No. AN60, and <u>Reconfiguration</u>, Order No. AN71.

This PLM also covers system shutdown, whose organization and implementation are related to initialization. Shutdown consists of the orderly stopping of a Multics system, either by operator command, or by BOS command following a system crash. The latter is known as an emergency shutdown.

This PLM is organized as follows. Section I gives overviews, and discusses policies and environments not specific to any part of initialization or shutdown, but of interest during all of it. These descriptions are in some sense a collection of information about these policies throughout initialization. Because of its supreme importance throughout initialization, the Segment Loading Table (SLT) is described in Section I. Many of the details in the SLT description are not apparent until later sections. Sections II and III describe the two major phases of initialization. Descriptions of the programs, the building of the environment and overviews are provided. Section IV describes shutdown. Section V is a module-by-module listing of initialization and shutdown modules, providing capsuled descriptions of their function. Some miscellaneous modules are also described.

# STRATEGY OF INITIALIZATION

The overall strategy of initialization is that of a "bootstrap" process. That is, the first procedure of initialization runs in an environment devoid of all software assistance. Each new mechanism (segmentation, stacks, symbolic linkage, I/O, interrupts, paging, etc.,) is made operative as soon as possible and then used to enrich the environment in which further mechanisms are made operative. Many mechanisms have subsystems of the supervisor that control them and these subsystems must be initialized before the associated mechanism can be used. The initialization of most subsystems is

accomplished by a call from the initialization driver programs to an entry point in that subsystem devoted to the specific purpose required. Most of these subsystem initializations consist mainly of the setting up of data bases (threading of lists, initialization of arrays, etc.), frequently based upon configuration dependent data specified in the CONFIG deck.

Initialization can be viewed as the loading of procedures and data bases (in part) of the hardcore supervisor the Multics System Tape. The programs on the constitute precisely enough information to bring a bare hardware system (containing no data other than firmware) to Multics command level and allow a reloading of files to take place. previous existence of BOS and the CONFIG deck is assumed.) of the segments (procedures and data bases) on the MST ultimately up in the Multics Storage System; most do not. All of the hardcore supervisor is on the MST. None of it is retained from a previous bootload. Segments are arranged on the MST in such order that the earlier segments allow as many mechanisms as possible to be used in loading the later segments. For this purpose, the MST is divided into three collections, described later.

Initialization can be viewed as the loading of collection 1, the initialization of collection 1, the loading of collection 2, the initialization of collection 2, and the loading of collection 3. This is a very rough description, meant only to illuminate the use of collections.

Among the last mechanisms to become operative are the control and ring mechanisms. One processor (the bootload processor or bootload CPU) performs initialization. The bootload processor, while performing initialization, runs exclusively in ring 0. As traffic control all operative, it is not meaningful to ask in which process initialization is performed. However, the per-process data bases used by initialization ultimately become the corresponding data bases of the initializer process, Initializer.SysDaemon.z. can be said in general terms that the initializer process system initialization. The last step performs initialization is the calling of the first user-ring procedure of the initializer (system\_startup\_), or system control process.

## THE SEGMENT LOADING TABLE (SLT)

are two data bases of paramount importance to initialization. The first of these, the CONFIG deck, describes configuration-dependent data, including table sizes, various software allocations, interrupt cell, port and assignments, and available hardware. The CONFIG constructed by BOS, and is described in detail in the Multics Operators Handbook.

The other data base is the Segment Loading Table. The SLT consists of two logical parts, implemented as the two segments known as slt and name\_table, respectively. The first part, or the SLT proper, consists of some fixed information and an array, indexed by segment number, describing all that is known about each segment loaded from the MST. This information is supplied by the MST segment header, a four-word block supplied by the MST generator (see generate\_mst in the <a href="System Tools">System Tools</a> PLM, Order No. AN51), which precedes each segment on the tape. The MST generator derives the information from both the system header file and the segment itself. The information can be modified by initialization procedure in some cases.

As procedures and data bases are loaded from the MST by initialization, they are accessed via the segmentation mechanism. This allows the SLT to be accessed as an array indexed by the segment number assigned at that time. Thus, the SLT is essentially a map of the descriptor segment used by initialization. The segment number assigned is used thereafter by every process to access that segment when in ring 0. This is explained more fully in Section III under "Hardcore and Outer Ring Segment Numbers".

Associated with each SLT entry, or SLTE, is a variable variable-length ASCII-coded information. includes names of the segment and a possible access information control list (ACL) to be associated with the segment if it ultimately to go in the Multics storage system hierarchy (see "Branch Creation and Connection" in Section III). To allow the SLT to be accessed as an array, this information is stored in the Name Table, which is in the segment name\_table. Pointers in the SLTE connect the SLTE to the array of names for each segment in the name table. These names are needed to allow the various initialization procedures to reference themselves and their data Twice in initialization a special linker known as bases by name. the prelinker runs, resolving as many outward references of initialization procedures as is possible at that time. speak of the name of an initialization procedure or data base, it the name stored in the SLT Name Table to which we refer.

These names are also used as entrynames for those segments that ultimately go into the storage system and are added via the normal storage system name appending primitives (see hcs\_\$append\_branch and hcs\_\$append\_branchx in the Multics Programmers Manual Subroutines, Order No. AG93, also the Storage System PLM).

The segments used by initialization may be divided into two broad categories: those used only by initialization and subsequently discarded and those that are part of the normal Multics system. The former are known as initialization segments, the latter as supervisor segments. These terms are used only with respect to initialization. The segment numbers assigned to supervisor segments by initialization start at zero; initialization segment numbers start at 400. (All numbers given here are octal unless otherwise specified. Numbers given in English, e.g., thirty seven, are decimal. All numbers in PL/I declarations are decimal.)

Consider the declaration of the SLT.

declare 1 slt based (sltp) aligned,

2 name\_seg\_ptr pointer,

2 entry\_length fixed bin(18)

2 first\_sup\_seg fixed bin(18),

2 last\_sup\_seg fixed bin(18),

2 first\_init\_seg fixed bin(18),

2 last\_init\_seg fixed bin(18),

2 free\_core\_start bit(18) unaligned,

2 free\_core\_size bit(18) unaligned,

2 seg  $(0:81\overline{9}1)$  aligned,

3 slte like slte; /\*slte declaration given below\*/

#### where:

name\_seg\_ptr

is an ITS pointer to the SLT Name Table, word 0.

2. entry\_length

is 4.

3 first\_sup\_seg

is 0, the segment number or the lowest-numbered supervisor segment.

4. last\_sup\_seg

is the segment number of the highest-numbered (hence the last) supervisor segment loaded.

- 5. first\_init\_seg

- is 400, the number of the lowest-numbered initialization segment.

- 6. last\_init\_seg

- is the segment number of the highest-numbered initialization segment loaded.

- 7. free\_core\_start

- is the address, rounded up mod 64(10) and divided by 64(10) of the first free block of main memory after the permanent unpaged segments. This is explained under "Memory Management" and "bootstrap1."

- 3. free\_core\_size

is the number of whole 64 (10) word blocks (a block must start on a 64 (10) boundary) available between the end of the permanent unpaged segments and the beginning of the temporarily unpaged segments (also to be explained), after bootstrap1 has run.

9. seg

is the array of SLT entries.

Now consider the SLT entry declaration. Remember for segments that have the header attribute linkage, the linkage section has been stripped off by the MST generator and made into a separate segment. This segment has the names of the main (text) segment, with the suffix link appended to each and, with its header, follows the text segment immediately on the MST.

declare 1 slte based (sltep) aligned,

```

( 2 names_ptr bit (18),  /* word 0 */

2 path_ptr bit(18),

2 access bit(4),  /* word 1 */

2 cache bit(1),

2 pad1 bit(1),

2 pad2 bit(6),

2 wired bit(1),

2 paged bit(1),

2 per_process bit(1),

2 ds bit(1),

2 dirsw bit(1),

2 acl_provided bit(1),

```

```

2 pad3 bit(3),

2 branch_required bit(1),

2 init_seg bit(1),

2 temp_seg bit(1),

2 link_provided bit(1),

2 link_sect bit (1),

2 link_sect_wired bit(1).

2 combine link bit(1),

2 pre_linked bit(1),

2 pad4 bit(7),

2 cur_length bit(9), /* word 2 */

2 ringbrack(3) bit(3),

2 segno bit(18),

2 pad5 bit(3), /* word 3 */

2 max_length(9).

2 bit_count bit(24)) unaligned;

```

### where:

- 1. names\_ptr

- is the offset into the name table segment of the name structure for this segment, which is declared below.

- 2. path\_ptr

is the offset into the name table segment of the directory pathname structure (declared below) of this segment if slte.branch\_required is on. This is the name of the directory in the storage system hierarchy in which this segment is to be ultimately placed. Only some segments from the MST go into the storage system heirarchy.

3. access

is the first four bits of the access field of the SDW that are constructed by initialization for this segment. These are the Read, Execute, Write, and Privileged bits. This is not the access that goes into any ACL entry in the branch. This is the same access used in the hardcore descriptor for this segment in every process.

4. cache

is the SDW cache bit for the hardcore and initialization SDWs constructed for this segment. If on, the segment is to be allowed in the cache.

5. Wired

if this bit and the paged bit (see below) are on in this SLTE, this segment is to have all its pages wired (made nonreplaceable in main memory to page control). The segments pds and pl1\_operators\_ are special-cased and partly wired. If the paged bit is off, this bit is not meaningful.

6. paged

- specifies that the segment is to be made paged at an appropriate time. A paged segment can also be wired.

- 7. per\_process

- specifies, if on, that the SDW for this segment, as created by initialization, should not be used by process creation (see the <u>Process and Processor Control PLM</u> for details of process creation) when descriptor segments for new processes are created. By default, all of the SDWs for supervisor segments are put in a new descriptor segment when a process is created.

8. ds

is on in the SLTE for the descriptor segment itself. This flag is used to prevent threading of the descriptor AST entry of the segment (see "The Making Paged of Segments" in Section II).

9. dirsw

- specifies that this segment is a directory. Not currently used.

- 10. acl\_provided

- specifies that an ACL (access control list) structure, declared below, was supplied by the MST generator for this segment. It follows the pathname structure in the name table segment. This bit is only meaningful when the branch\_required bit is on.

- 11. branch\_required

- specifies that this segment is to go in the Multics Storage System hierarchy. A directory pathname, for the directory to contain this segment, is pointed to by the path\_ptr field (see above).

12. init\_seg

specifies that this segment is an initialization segment, to be discarded at the end of initialization. If this segment is a temp-seg, this bit is not on.

13. temp\_seg

specifies that this segment is a temp-seg. This is a type of initialization segment that is to be discarded at the first purging of such segments after it has been loaded. See "Memory Management" in this section.

14. link\_provided

specifies that the linkage section of this segment has been stripped off by the MST generator and follows this segment on the tape.

15. link\_sect

specifies that this segment is the linkage section of some other segment, stripped off by the MST generator. If on, the segment field specifies the segment number assigned to the corresponding text segment.

16. link\_sect\_wired

specifies that the linkage for this segment, which must be a text segment with the linkage\_provided bit on, must be wired. This information is used by the prelinker to determine whether the linkage for this segment should be combined with wired linkage for wired segments or nonwired linkage for nonwired segments.

17. combine\_link

specifies if the linkage for segment, which again must have the linkage\_provided bit on, should combined at all. Linkage segments, in general, are temp-segs, that combined and then discarded. Some are simply discarded, while others remain as self-standing supervisor segments. the paragraph on prelinking in Section II.

18. pre\_linked

is a flag created and used by the prelinker. If on, it indicates that the prelinker has already processed the linkage section of this segment. It prevents the prelinker from combining linkage twice on a segment.

19. cur\_length

is the cur\_length attribute specified for this segment in the header, pages. For segments in collection 2 and paged segments in collection 1, it is used by make\_sdw to determine which size entry should be allocated for this segment. cur\_length is usually exactly enough pages to include as many words as specified by the slte.bit\_count field. (This can only bе overridden supplying both the cur\_length bit\_count attributes in the MST header). bootstrap1 redefines the bit\_count cur\_length fields for the data segments for disk subsystems not part of the configuration being bootloaded, zeroing them. The cur\_length (and possibly max\_length) fields for certain tables in collections!1 and 2 can also dynamically changed at bootload time the TBLS CONFIG card.

20. ringbrack

is the array of ring brackets to go the branch for this segment if it goes in the storage system hierarchy. For the two segments return\_to\_ring\_0\_ and restart\_fault\_, however, these are brackets that go in hardcore descriptors for these segments. In other case do these ring brackets go in the hardcore descriptors in any process. These two special cases are necessary user-ring fault signalling mechanism (see "Hardcore and Outer Ring Segment Numbers" in Section III and the Process and Processor Control PLM).

21. segno

is the segment number allocated to the linkage section of this segment if the linkage\_provided bit is on, or the text segment corresponding to this segment if the link\_sect bit is on. This field is

used by the prelinker to locate definition sections and fill in LOT entries. (See the <u>Binding</u>, <u>Linking</u>, <u>and Makespace Management PLM</u>, Order No. AN81, for details on linking). This field is filled in by bootstrap1 and segment\_loader, the two segment loading programs, as the text-linkage pairing is determined.

22. max\_length

specifies the max\_length attribute given in the MST header. This is the maximum length, in pages, to which this segment is allowed to grow. It is ignored in the loading of segments in collection 1. If given, it is used to assign an AST entry of proper size for paged segments in collections 1 and 2. It overrides the cur\_length attribute. It is also used to set the max\_length attribute in the branches of segments that go in the storage system hierarchy.

The max\_length in the branches of the SLT and name\_table themselves are special cases, however (in the procedure init\_branches), as their own SLT entries do not reflect their correct length at the time that this branch creation is done.

23. bit\_count

is the actual length, in bits of the segment. This number is used to determine how much space should allocated for this segment in main memory if it is ever copied or moved. Furthermore, this is the number set in the branch of any segment that goes into the file hierarchy as its bit count. See cur\_length above.

### Name Table

where next\_loc is the relative address into the segment of the next available location where data can be stored.

The structure for one name is as follows:

- 1. count is the number of names given in this name structure.

- names are the structures giving the individual names.

- 3. size is the number of significant characters in the name.

- 4. name is the actual name, left-justified.

## Pathname Structure

If slte.branch\_required is on, slte.path\_ptr gives the relative address into the name\_table segment of this structure.

#### where:

- 1. size is the number of significant characters in the pathname.

- 2. name is the pathname of the directory in the storage system hierarchy into which this segment is to be placed. Note that only as many words as are needed to contain the significant characters are required.

If slte.acl\_provided is on, the ACL structure immediately follows the pathname structure. A description follows:

declare 1 acls based (aclp) aligned,

2 count fixed bin,

2 acl (50 refer (acls.count)),

3 userid char(32),

3 mode bit(36) aligned,

3 pad bit(36) aligned,

3 code fixed bin;

#### where:

- 1. count is the number of ACL terms provided in this structure.

- acl is the array of ACL terms.

- 3. userid is the User\_id (e.g., Greenberg.Multics.a) of this ACL term.

- 4. mode is the access mode for that userid. Currently, only the first three bits (read, execute, write) are defined.

- 5. code is part of the user interface to ACL terms and is not used by initialization.

# Creation of the SLT

The SLT is created by bootstrap1, the very first program of initialization. The first few entries in it are prefabricated in bootstrap1 and describe the descriptor segment, mailboxes and the fault vector, the processor utility segment, the configuration deck, and the SLT name table themselves. The SLT entries are described in the include file slt\_init.incl.alm, also used by the MST checker (see check\_mst in the <u>System Tools PLM</u>). There are also a few entries built in this way for initialization

<sup>&</sup>lt;sup>1</sup>The processor utility segment (processor\_utility\_segment), contains the floating fault vector (see the <u>Processor Manual</u>, Order No. AL39). Multics does not now use the floating fault feature.

segments, namely bootstrap1 and the physical record buffer, the latter used for reading tape during initialization. Those segments whose SLT entries are created by bootstrap1 from this include file (these segments are never loaded, per se) are sometimes referred to as collection 0.

They become paged at the time that other segments become paged. They are not wired. They are eventually put in the storage system hierarchy in >system\_library\_1. The segment number of the SLT is known to be seven as BOS uses it to find other segments and must start somewhere.

The SLT is also used by some user-ring debugging tools to obtain names of hardcore segments for error messages (see <u>User Debugging and Tracing Tools</u>, Order No. AN79) and by some tools (see the <u>System Tools</u> PLM, and <u>System Dump Analysis</u>, Order No. AN53).

# THE ENVIRONMENT PASSED TO INITIALIZATION

The following discussion describes machine state and data given to bootstrap1, the first program of initialization.

The command BOOT is given to BOS to initiate the bootloading of the Multics system. BOS maintains an "image" of Multics core, consisting of all of the core configured into the system not used by BOS, plus a disk buffer area representing the core that is held by BOS. The management of this buffer is described in the  $\underline{BOS}$  PLM, Order No. AN74. The final operation invoked by the BOOT command is the transfer of this buffer into actual core and the transfer of control to a set location.

Multics expects all of core to contain zeroes, except for four items, described later. Thus, the BOOT command zeroes the entire Multics core image.

Multics expects the data contained in the configuration (CONFIG) deck, in its mostly ASCII format as produced by BOS, to reside in location 6000, occupying one page. Thus, the BOOT command copies this information from its storage area within BOS to this point in the Multics core image.

Throughout all of Multics and BOS operation, the page at location 4000 contains a program known as the BOS toehold. This program is described in detail in the BOS PLM. Among its functions are the reading of the disk portion of the Multics core image into core and transfer of control as the last stage of a

BOOT or GO command, and the return of control to BOS and saving of the Multics core image as a result of an orderly or unexpected return to BOS. Multics expects this program to be in this location.

Location 4004 is known to contain a pair of instructions that, if executed in absolute mode, cause a restartable return to BOS, ("restartable" means that BOS can return to Multics at the instruction following the instruction that caused execution of the pair at location 4004.) The occupancy of this page and the location of that pair constitute all of the knowledge that Multics has of BOS. The area containing this toehold is not considered part of the Multics core image and is neither written out when the latter is saved on disk, nor restored when it is read back.

bootstrap1 also expects that the IOM mailbox contains sufficient information to determine the IOM channel number and device number of the tape drive on which the MST is mounted. BOS copies this information into the place in the Multics core image that corresponds to the IOM mailbox.

The final item expected by Multics is the first tape record (past the label and following end-of-file mark) of the Multics tape (MST) to be loaded into the core image. The first program on the tape is bootstrap1. Its first record is loaded so that location zero of this program is at location 10000, absolute. Preceding bootstrap1 on the MST are its MST control words (see generate\_mst in the <u>System Tools PLM</u>) and its SLT entry (from the MST header). This data in turn lies on a Multics standard tape record, which has a header eight words long. Thus, the physical tape record has to be loaded into some location lower than 10000. However, to facilitate the loading of the physical record into location 10000, the MST generator strips the first 40 words off bootstrap1 and pads enough words so that when the record is read location 10000.

Summarizing, the data items expected to be in core at the time control is transferred to bootstrap1 are the CONFIG deck, the BOS toehold, the first record of bootstrap1 itself, and the tape data in the IOM mailbox.

Multics also expects the DATANET 6600 FNP to have been properly bootloaded by BOS. It also expects the DATANET mailbox, the floating fault vector (currently not used) and the bulk store mailbox to be defined in their standard locations.

At BOOT time, BOS modified the CONFIG deck by the addition of a card known as the INTK (for INTaKt  $\langle \text{sic} \rangle$ ). Its format is

### INTK bootsw part

where bootsw is nonzero if this is a "warm" boot (a hierarchy is present on disk) and zero if cold (not present). part is the name of the partition on disk (normally MULT, but SALV if the salvager is being booted) that Multics is expected to use. This card is looked at by the procedures that must initialize access to the hierarchy (see "Branch Creation and Connection" in Section II).

bootstrap1 expects one and only one processor to be running. It expects to receive control at location 40 relative to its base It expects that the system controller in absolute mode. containing it has the processor on which it is running as control It expects the cache on this processor to be processor. inhibited. It expects index register 2 to contain the absolute location of word zero of bootstrap1, hence it makes no assumptions about where it is, other than that it is on a page boundary in the low-order memory. It expects that index register 0 contains the absolute address of the IOM mailbox and index 1 contains the base address of the interrupt vector, which, on the Model 6180, is always zero. It expects that the tape drive selected by the PCW in the IOM mailbox is in the right data mode and correctly positioned to read the second physical record of bootstrap1.

To facilitate system debugging and problem analysis, initialization interrogates the processor data switches on the bootload processor (the processor that entered bootstrap1) at several times, looking for specific patterns. If these patterns are found at the times they are sought, control is returned to BOS in an orderly fashion, allowing dumping and patching. A subsequent GO command issued to BOS restores control to the point where control left Multics. These patterns (in octal, where "x" represents "don't care") and the points at which they reenter BOS are:

- 123 4xx xxx xxx bootstrap1 has just received control from BOS. Only its first record is in core.

- 123 2xx xxx xxx bootstrap1 has read itself into core. Nothing else has been read in, still in absolute mode.

- 123 1xx xxx xxx bootstrap1 in appending mode, with most of its data bases initialized. Collection 1 not

loaded yet.

| 123 | x4x   | xxx | xxx | bootstrap1 ready to transfer control bootstrap2. Collection 1 loaded. | to |

|-----|-------|-----|-----|-----------------------------------------------------------------------|----|

| 123 | x2x   | xxx | xxx | Collection 1 loaded and initialized, ready load collection 2.         | to |

| 123 | x 1 x | xxx | xxx | Collection 2 loaded.                                                  |    |

| 123 | x x 4 | xxx | xxx | Collection 2 loaded and initialized, ready load collection 3.         | to |

| 123 | xx2   | xxx | xxx | Collection 3 loaded. Traffic control and I not yet initialized.       | /0 |

In the above patterns, the first nine bits (123) identify the data switch settings as "debugging return to BOS." The remaining bits are not mutually exclusive, i.e., more than one may be set, causing many returns to BOS. (These switch patterns can be remembered by the assumption that there are four pairs of values corresponding to stopping before and after loading collections 0, 1, 2, and 3. The 123 is ASCII for S, as in STOP.)

# THE INITIALIZATION ENVIRONMENT

The following discussion describes the growth of the Multics environment during initialization. This growth might be viewed as an extraction of relevant information from descriptions of the various parts of initialization. This discussion attempts to answer questions such as "When does paging first become effective?"

# Faults and Interrupts

Control is passed to bootstrap1 in absolute mode. The processor is functioning without any segmentation or paging. For the first few instructions, all instructions have the inhibit bit (bit 28) on. No assumptions are made about the contents of the fault and interrupt vectors in main memory. The timer register of the processor is loaded almost immediately with a very large number to prevent timer runouts.

One of the first tasks of bootstrap1 is to mask out interrupts, so that it can cease its use of the inhibit bit. Taking advantage of the inhibit bit could create a lockup fault,

so its use is to be minimized. bootstrap1 determines to which port on the low-order (bootload) memory the bootload processor is attached by interrogation of that system controller with an RGR command generated by an RSCR instruction. The execute interrupt mask assigned to that port is then masked so that no interrupts are allowed. The channel mask in the controller is set fully open as it has not yet been determined precisely what the configuration is.

Once this is done, use of the inhibit bit is curtailed. bootstrap1 now fills in all of the interrupt vector pairs in main memory to ignore interrupts. The fault vector is set to cause a fatal crash on all faults except timer runout, which is ignored. All interrupts are then enabled. Appending mode is soon entered. bootstrap1 eventually transfers to bootstrap2 after the loading of collection 1, which eventually gets to call (through initializer and init\_collections) initialize faults\$fault\_init\_one.

This is one of the earliest calls in initialization as it must take responsibility for fault handling away from bootstrap1. Here, the fault vector pairs for timer and lockup are set to pairs that ignore these faults, as are all interrupt vector This fault and interrupt ignoring is handled wired\_fim\$ignore, storing SCU data at prds\$ignore\_data. faults (directed fault 1) are directed to the proper entry, page\_fault\$fault, as are segment faults (directed fault 0, directed to fim \$primary\_fault\_entry), and connect faults (wired fim \$connect\_handler). Segment fault handling must be initialized because it is used in collection 2 initialization this time before all of the faults relevant to collection 2 have properly. initialized A11 other faults are directed ii\$unexp\_fault, storing SCU data prds\$sys\_trouble\_data. at Hence, unexpected faults during most of initialization store their SCU data here and this area is the first place to analyze during system problems relating to initialization. The floating fault vector, assumed at location 1020, is initialized to direct floating faults to a handler in fim, which crashes the system. The floating fault feature, under the control of the processor mode register, is currently not used by Multics.

Later in collection 1 initialization, data extracted from the configuration deck is used to determine the assignment of interrupt cells. This is done after system configuration (system controllers, processors) has been ascertained and verified. At this time, initialize\_faults\$interrupt\_init is called. This entry directs all interrupts to their final handlers, in most cases the interrupt interceptor (ii). During interrupt initialization (initialize\_faults\$interrupt\_init), all interrupts

1 - 18

AN70

other than the system trouble interrupt are masked off. this is complete, all legal system interrupts are then unmasked and the channel mask on the bootload system controller set properly. These masks are determined from the configuration All unassigned interrupts are directed syserr\$syserr\_int. Collection 2 is now loaded. Immediately before the accessing of the storage hierarchy, when bounds faults directories are possible, all faults are directed to their handlers. This is initialize\_faults\$fault\_init\_two.

### Error Handling

unexpected faults included, encountered All errors, bootstrap1 or the fault vectors set up by it, result the processor halting (on a DIS instruction) with an error code stored in the accumulator and registers stored in main memory. The identity of these errors must be ascertained from analysis of these quantities. Once initialize\_faults\$fault\_init\_one has run, unexpected faults cause a return to BOS with machine conditions stored at prds\$sys\_trouble\_data. Soon after this entry has been called, the procedures to initialize the operator's console under (its data bases, DCW lists, etc.) are called. Note that until interrupts are fully initialized, the operator's console runs without the use of interrupts. As the time zone in which Multics is running has not been established at this point, messages reported on the operator's console until the time zone has been established are generally incorrect (assumed Greenwich Time) in their time designation. initialize\_faults\$fault\_init\_one sets some pointers used for clock reading to temporary values, simply to allow clock reading to function without causing problems. The operator's console logging mechanism is not initialized until the end of initialization as this requires the support of the collection 1 full paging mechanism. After the operator's console has been successfully, most errors detected by programs initialized (configuration inconsistencies, errors normally detected Multics, etc.) cause a message to be printed on the operator's console and possibly logged. If the error is fatal, i.e., causes return to BOS, the problem can be analyzed by tracing the call history of syserr, the operator's console manager.

There are several circumstances in which errors detected by programs cause a return to BOS without a message. These include the taking of certain faults when disallowed. These returns to BOS are accomplished via the system trouble interrupt, a software-defined interrupt that causes all processors to halt, except the bootload processor, which returns to BOS. Again,

except the bootload processor, which returns to BOS. Again, machine conditions are stored at prds\$sys\_trouble data, allowing identification of the program that sent the system trouble interrupt.

Difficulty in initializing the operator's console also causes a return to BOS without a message.

# Segmentation and Paging

bootstrap1 receives control in absolute mode. As soon as it read itself in (remember that loads only its first BOS record), a descriptor segment is set up. as all segments set up by bootstrap1, is a contiguous, descriptor unpaged segment. It is set up off of the end of bootstrap1. SDWs are created in this descriptor segment to describe the descriptor segment itself, bootstrap1 itself, the interrupt vector (including the fault vector), the DATANET mailbox, the bulk store and IOM mailboxes, the configuration deck as passed by BOS and the floating fault vector. The SLT and the table are then laid out following the descriptor They are unpaged segments and descriptors are made to segment. describe them. The physical record buffer, a segment used as an I/O buffer for initialization's reading of the MST, is laid out The physical record buffer and bootstrap1 are initialization segments--all of the rest are segments. Appending mode (supervisor) is then entered. segments are loaded by bootstrap1, descriptors are constructed them. All of these segments are unpaged. The first paged segment to be constructed is the SCAS, or System Controller Addressing Segment. A segment named scas is loaded by bootstrap1 from the MST. It, like all others at this time is unpaged. procedure scas\_init, running at collection 1 initialization, in this segment a page table, eight entries long, for This segment has the zeroth word of its a segment. being the zeroth word of main memory in the system controller on processor port n (starting from zero). The "unpaged" bit of the SDW for this segment is turned off and the bound set to the minimum, 16(10) words. This segment is used for addressing controllers for functions other than storing retrieving data, specifically the RSCR and SSCR instructions. The page table for this segment is completely outside of the domain of page control, which is unaware of the existence of this page table. The areas of main memory pointed to by the scas page are not reserved -- they are used as normal pages of main memory, subject to other constraints. The SCAS is discussed more fully in "Configuration Initialization" in Section II.

1-20

AN70

The procedure initialize\_dims creates the first real segment. The File System Device Configuration Table (FSDCT), must be accessed if this is a warm bootload or created if a cold bootload. (See the Storage System PLM for details on the use of FSDCT.) An AST entry containing a page table initially with addresses is allocated. null A descriptor describing a paged segment, using this page table, replaces the descriptor for the zero-length segment fsdct. At this time, page control and I/O routines have been sufficiently initialized so that page faults can be taken. Nevertheless, pages cannot yet be withdrawn from or returned to the FSDCT as the latter is not yet wired, and a page fault during a page fault would result if an attempt were access it. If this is a warm boot, it is defined that made the first page of the FSDCT resides on record 0 of partition of the master device (the device with the lowest device that has a MULT partition.) This device address is inserted into the address field of the zeroth PTW of the FSDCT. defined that a file map (array of device addresses) for the FSDCT begins somewhere on its zeroth page. This file map is copied from the FSDCT into its own page table, other than the zeroth This access to the FSDCT causes a page fault, but there are no other pages in core that could get written out (causing deposits to the FSDCT if zero) and no page faults have been taken on pages with null address, causing no withdrawals from the As soon as the FSDCT is in core, it is wired and deposits FSDCT. and withdrawals can now function. Paging may be said to be operative at this point, although none of it is going on and only one legitimate (non-SCAS) segment is paged. Ιn the case cold boot, the FSDCT is created from scratch. Disk space is allocated for all pages of it, withdrawing it from the being created to avoid later withdrawals by page control. wired in this case too.

The procedure make\_segs\_paged (formerly update\_sst\_pl1) responsible for making the segments that should be paged into paged segments. This is true only for collection 1 segments, as segments in collections 2 and 3 are always paged. This procedure obtains an Active Segment Table Entry (ASTE) and page table for a descriptor segment, that will be paged. This descriptor segment will be used by initialization and the initializer process from that point on. This procedure obtains ASTE/page tables for all of the segments to be paged. It copies the unpaged segments (through an a privileged\_mode\_ut\$swap\_sdw\_in\_use) into auxiliary procedure, their new incarnations. The new SDW for the paged segment replaces the SDW for the unpaged segment in both the current (constructed by bootstrap1) descriptor segment and the descriptor segment built (the paged one). More will be said about this in the "Main Memory Management" in this Section and in "The Making Paged of

Segments" in Section II. Finally, the SDW of the new descriptor segment is loaded into the DBR. Paging and segmentation are fully operative at this point.

At the time collection 2 is being loaded, an ASTE/page table is allocated for each segment before it is loaded. The size of this page table, like those in collection 1, is determined by the procedure make\_sdw from the cur\_length and max\_length attributes in the SLTE of the segment, which precedes the text of the segment on the MST. The tape reading routine (tape\_reader) copies the segments being loaded directly into the segment being constructed. SDWs with correct access information are placed in the descriptor segment after the particular segment is loaded.

The initiation of segments and segment faults do not occur until the initialization of collection 2. The procedure init\_root\_dir makes a call (to initialize\_kst) to set up the KST of initialization (to become the KST of Initializer.SysDaemon.z) to be able to initiate segments. The root is initiated and a segment fault occurs on it. More is said about this under "Root Directory Initialization" in Section III, and the Storage System PLM. Segment faults can now be taken on all segments and branches can be appended and initiated via the normal storage system interfaces. Thus, the segments in collection 3 are loaded by simply appending branches to the storage system and copying segments from the physical record buffer, piece by piece, into the newly created segments. Access is set to allow this copying and set appropriately afterwards.

Branches must be created for some segments in collections 1 and 2. However, since segment faults taken by processes look to the branches of segments to find their AST entries, if active, collection 1 and 2 segments that are to have branches (be in the hierarchy), must have ASTEs and thus page tables and therefore must be paged. This requires many of those segments in collection 1 to be paged. Other than the FSDCT, shutdown stack, Paging Device Map Segment, and PRDS, all of the wired paged segments in collection 1 are paged for this reason.

The hardcore supervisor never takes a linkage fault. The initialization of the system search rules (thus initializing the linker mechanism) is one of the very last things done by system initialization.

1-22

AN70

### The PL/I Environment

bootstrap1 runs in privileged mode since issuing I/O instructions is one of its functions. It uses pointer registers to point to the SLT, Name Table, fault vector, physical record buffer, IOM mailbox, configuration deck, the descriptor segment, and each segment being loaded. It uses no stacks and all calls are made via index registers, i.e., TSXn instructions. It is impure; it modifies its own code and data. It makes no external references as there is no program to resolve such links. It does not even have a linkage section. It remembers the segment number of "interesting" segments as it passes them in loading.

bootstrap1 passes control to bootstrap2 once collection 1 is Among the information passed with control is the segment number of the segment pds, which will be used as a stack, and the segment number of the SLT manager, an initialization program that can resolve a segment name into a segment number from the SLT. As both bootstrap2 and its linkage section are initialization segments, the former precedes the latter immediately on the MST, and the fact that their segment numbers are contiguous is known bootstrap2. Thus, bootstrap2 loads the linkage pointer register with a pointer to the base of the segment whose segment is one greater than the segment number of bootstrap2, the latter being determined with an EPAQ instruction. bootstrap2 now establishes a stack frame on the segment pds, (known PDS"). Multics standard calls can now be made, but not through links, as these have not been snapped. Some information in the stack base of the pds is initialized. Itspointer to the signalling procedure is initialized to point to segment -2, word which would cause a fatal process error. The SLT manager is now called to ascertain the segment number of the prelinker. call is made based upon the segment number passed by bootstrap1, who noticed and remembered it as this segment loaded. As no links have been snapped, all of the procedures that run before prelinking (including bootstrap2, bootstrap1) are called via transfer vectors at their zeroth through nth words, different offsets corresponding to different Once prelinking is complete, these procedures are called in the normal PL/I fashion. Among the information prelinker by bootstrap2 is the segment number of the SLT the The prelinker (the programs pre\_link\_1 and pre\_link\_2) manager. attempts to snap all links in all hardcore linkage sections, which are conditionally (based on the SLT) combined into combined linkage segments. There is one combined linkage segment that always remains wired and one that is paged and unwired. the decision to place a linkage section in one or the other is

1-23 AN70

based upon SLT bits. A Linkage Offset Table (LOT), is created. (See the <u>Binding</u>, <u>Linking</u>, <u>and Makespace Management</u> PLM, Order No. AN81, for details on the LOT.) Once the prelinker returns to bootstrap2, symbolic calls can be made. bootstrap2 initializes pointers in the base of the PDS to point to various operators within the PL/I operator segment and PL/I programs can now be used (all programs were assembler-coded up to this point). The call-push-return mechanism is fully operative, and the PDS is being used as a stack (it is unpaged now and thus may not grow, it may grow after being made paged) and all symbolic references capable of being resolved have been resolved. program initializer is called (not transferred to). Signalling and the condition mechanism are not operative. attempts to signal cause the process-terminating pointer to be indirected through, causing the system to terminate operation (attempts to terminate the initializer process are always fatal to the system). After collection 2 is loaded, it is prelinked to and from collection 1 and itself. initialize\_fault\_\$fault\_init\_two\_sets this pointer to the normal signalling procedure, signal. This is the earliest time that signalable faults are allowed.

The PDS is used as a stack as soon as stacks are used at all. It becomes paged when other segments become paged, creating a unique problem involving the return from the segment paging routine which will be discussed under "The Making Paged of Segments" in Section II. The PRDS is used as a stack during interrupts and page faults, as in normal operation. It too becomes paged at the time that segments are made paged. The stack frame laid down by bootstrap2 remains on the PDS until the program initializer finally calls out (via init\_proc and gate\_init) to ring 1. Shutdown uses a special stack, shutdown stack, early in emergency shutdown or for the wired portion of normal shutdown.

### Traffic Control and Rings

Initialization runs in the address space that is to become the address space of the Initializer process, Initializer. SysDaemon.z. Until traffic control is initialized, after the loading of collection 3, control never leaves the initializer process. If any event (specifically, a disk page fault) must be waited on, a special loop in the program wired\_fim is entered by the traffic controller. This loop waits for a flag to be set by a routine that is called when an attempt is made to notify an event, invoked by an interrupt. These special handlings are done because the flag tc\_data\$wait\_enable is zero until traffic control is initialized. No directories should ever

be locked. Idle processes do not exist or run, and the body of the traffic controller (scheduler) is never entered until traffic control has been initialized by the procedure tc\_init. Initialization runs in hardware ring 0, not leaving this ring until init\_proc calls system\_startup\_ in ring 1, after all of the hardcore has been initialized.

### I/O Management

Input/Output during initialization consists of tape reading, operator's console writing, and paging. bootstrap1 physical tape reading routine in its first physical tape record. This routine is initialized to read the MST, from data left by in the IOM mailbox. It sets up LPWs, DCWs and PCWs to read the MST, and issues connects to the IOM. Once bootstrap1 has been read in, a more sophisticated tape reading routine within bootstrap1, which is knowledgeable about the format of Standard Tapes, including error retry conventions, is used to interface to the simpler routine. The sum of these two routines reads the segments and SLT headers of collection 1, using the segment physical\_record\_buffer as a single record tape buffer. The smaller routine that has read bootstrap1 is not knowledgeable these things, hence, bootstrap1 must be written on the MST without error.

During collection 1 initialization, the IOM manager and its data bases are initialized. This is the first initialization after the first fault initialization (see "Faults and Interrupts" earlier in this section). The operator's console is initialized next, without the logging facility. It uses the IOM manager to perform physical I/O. The clock reading and interrupt mechanisms for this work through interim methods that have already been described.

Collection 2 is loaded by a program called segment\_loader, invoked by the program initializer. This program calls a tape reading package called tape\_reader to read the MST. This program again knowledgeable about Multics Standard Tapes. It uses a program called tape\_io to perform physical I/0 via the IOM A device index is assigned to manager. the bootload tape drive/channel at the time this package initialized, is immediately before the loading of collection 2. Collection 3 is loaded by a program called load\_system (see "Memory Management" in this section), which also utilizes this tape reading package (tape\_reader and tape\_io),. After collection 3 has been loaded, bootload tape drive is rewound via tape\_reader\$final.

Paging I/O is initialized by the individual I/O routines for the storage system devices (disks, bulk store, etc.). routines are called at initialization entry pointialize\_dims, during collection 1 initialization. These entry points by This after happens both the IOM manager and interrupts initialized, but before paging is operative. These routines report to the IOM manager for device index assignment (except the bulk store control routine, as the bulk store interfaces directly system controllers, and hence, does not use the IOM). This initialization of communication with the IOM manager (see the <u>Supervisor Input/Output PLM</u>, Order No. AN65, for details on the IOM manager) includes communication of the identity of the interrupt handler of the routine, and base address for DCW lists. These routines are fully operative after this reporting has been done.

Other I/O device control routines (teletypes, I/O interfacer) are initialized after initialization of traffic control which follows the loading of collection 3. These routines are fully operative after initialization. The Network software is initialized by a call from an outer ring, via a gate, if a Network attachment is present, and is thus not part of system initialization.

Communication with the DATANET 6600 FNP needs initialization. This processor no is bootloaded by BOS. The initializations performed by Multics at collection initialization time, in the module dn355\_init, consist solely setting up some data for the DATANET communication routines. of pre-24.4 systems, this is done at collection 1 initialization time.

### MEMORY MANAGEMENT

The following discussion covers the development and use of different strategies for manipulating and managing main memory and virtual memory during initialization.

### Collections

As has been described, the Multics System Tape (MST) is divided into three collections of segments. The segments are separated by special control words known as collection marks, which are recognized by bootstrap1, segment\_loader and load\_system, the three segment loading programs. The significance of the three collections is as follows. There is much more data on the MST than can fit into main memory at any

one time. Hence, much of it will have to be loaded into virtual memory, i.e., loaded in the presence of an operative paging environment. Thus, a goal of initialization is the establishment of paged segmentation at the earliest possible time. Collection contains precisely those programs that are required accomplish this. All segments that are unpaged, as opposed paged and wired, appear in Collection 1. This is because only bootstrap1 can allocate unpaged, contiguous core in this way. Before System 24.4, the ability to wire segments in Collection 2 did not exist, and all wired segments were in Collection 1. Collection 2 contains all of the rest of the hardcore supervisor, i.e., all of the rest of the programs that will run in ring zero, and must be prelinked to programs in ring 0. The segments are loaded by the program segment\_loader directly into the Collection 3 consists of programs that are not part of the supervisor. These programs constitute precisely enough of system control and user environment to allow a reload of the storage system hierarchy to be performed. All of the programs in collection 3 are loaded directly into the hierarchy by the program load\_system.

# Supervisor, Init and Temp Segs

the first two collections are loaded, programs that will be used only by initialization and programs that will remain part of the Multics supervisor are added to the virtual memory. These segments are known as initialization segments supervisor segments, respectively. collections contains both types of and Each of the first segments. Among initialization segments, many are used only once (e.g., scs\_init, which initializes configuration-dependent data concerning port assignment and interrupt cells), and many are used more than once (e.g., tape\_io, which reads the Multics System Tape). Thus, a further subdivision is made within initialization segments: temp segs are segments that are to be discarded at the first opportunity following their use, and init segs proper, that are to be discarded at the end of initialization. Discarding these frees the AST entries they utilize, increasing the AST pool, and the disk and bulk store storage that they may occupy. Furthermore, it removes their SDWs from the descriptor segment that will belong to the initializer process. facilitate the use of this mechanism, many of the temp segs that In order to will be discarded after collection 1 are bound into a single bound segment, bound\_temp\_1. Temp segs to be discarded after collection 2 (those, obviously, are loaded in collection 2) in bound\_temp\_2. Init segs loaded in collection 1 are in bound\_init\_1, those loaded in collection 2 (used for loading collections 2 and 3, and initializations after collection 3 has

been loaded, e.g., the traffic controller) are in bound\_init\_2. Most linkage sections, stripped off of their text segments by the MST generator, are temp segs. The keywords init\_seg and temp\_seg in the MST header specify the assignment of these attributes to segments.

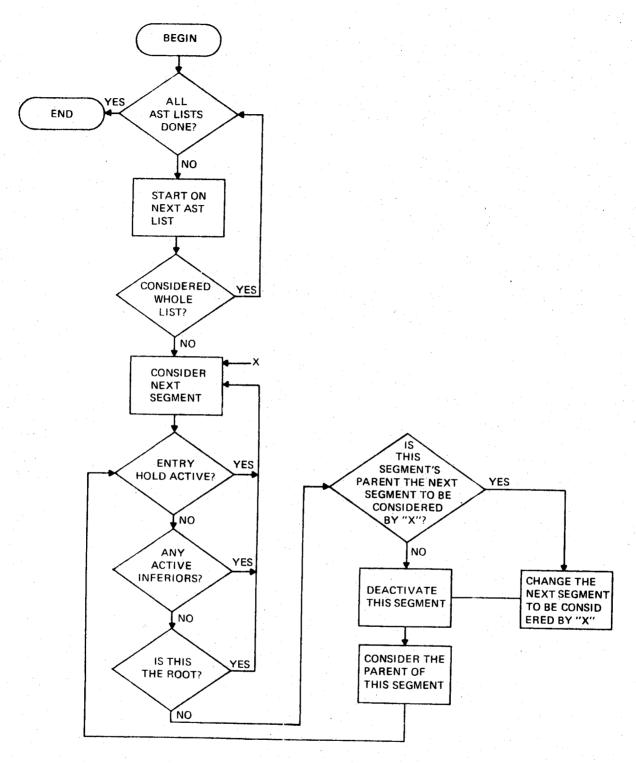

There are seven lists of ASTEs in the Active Segment There are four lists used by Multics while running, for (AST). the allocation and deallocation of ASTEs for segments on which segment faults have been taken. These correspond to the four sizes of AST entries, 4, 16, 64, and 256 (decimal, page table size in words.) A fifth list is called the hardcore list. AST entries for supervisor segments loaded in collection 2, and supervisor segments from collection 1 that obtain AST entries at the time that segments are made paged, are put on this list. However, those supervisor segments that ultimately go in the storage system hierarchy are not put on this list, but in one of four normal lists. This allows shutdown to process these segments when other active segments of the storage hierarchy are and/or have their branches updated. Shutdown also deactivated uses the hardcore list to delete (free the disk storage of) supervisor segments. Clearly, the code that does this and runs after this must not delete itself. Hence, all wired, paged, supervisor segments appear on no AST list in 24.4 and later systems. Most of shutdown, however, is unpaged code. AST list is maintained for init\_segs. AST entries allocated for init segs made paged in collection 1 initialization or loaded in collection 2 are put on this list. At the end of initialization this list is traversed, all of these entries are freed, and their segments deleted. The seventh list is the list of ASTEs of temp segs. Temp segs made paged in collection 1 or loaded in collection 2 have AST entries on this list. collection 2 is loaded, and again before collection 3 is loaded, this list is traversed and AST entries and secondary storage freed. Clearly, segments that are not paged and hence have no AST entries, occupy main storage permanently (if they are after segments are made paged.) paged The program delete\_segs is responsible for traversing AST lists and deletion of segments (for a description of delete\_segs see Section V).

Some special paged segments have their AST entries threaded out of any AST list to prevent both deletion or branch updating, which happens on the other lists. These segments are the PRDSs of processors, the shutdown stack, and the FSDCT, all of which must be used at shutdown time as segments are being deleted, and have no branches. The root is special-cased by shutdown to avoid deletion and branch updating.

1-28

AN70

# Main Memory Management

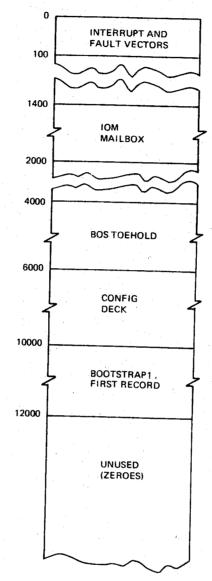

Figure 1-1 shows the layout of main memory as bootstrap1-1 receives control from BOS. The only information in main memory is the CONFIG deck, the BOS toehold, the information identifying the bootload tape drive and channel in the IOM mailbox and the first record of bootstrap1. The fault vectors, floating fault vectors, DATANET 6600 FNP and bulk store mailboxes are present, but contain no valid information.

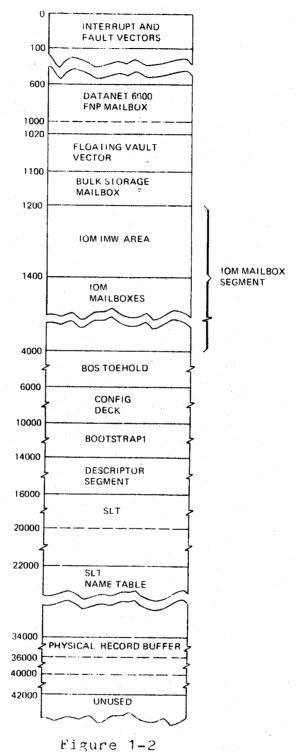

bootstrap1 proceeds to read itself in. It then lays out its descriptor segment, the SLT and SLT name table, and the physical record buffer directly after its own text. Descriptors are made to describe the mailboxes, CONFIG deck, and fault vectors. Figure 1-2 describes the layout of main memory at this time.

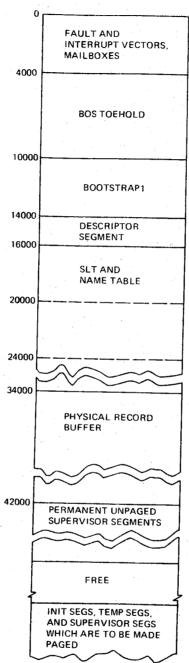

bootstrap1 now loads collection 1. As you will recall, all segments are unpaged at this time. Supervisor segments that are to remain unpaged are loaded following the end of the physical record buffer. This is where they will remain throughout Multics operation. They are loaded contiguously, one after the other, in ascending address order in main memory. Keep in mind that the mailboxes as well are permanent unpaged supervisor segments, but they were created as segments in preassigned location by bootstrap1 before collection 1 was loaded. All other segments loaded by bootstrap1 (including init and temp segs, and segments in collection 1 that are to be made paged) are loaded starting at the high-addressed end of available memory. They are allocated contiguously, one after the other, in descending address order in main memory. When all of these segments have been loaded, the starting address and length of the unused core remaining are copied in to the SLT (see the SLT discussion earlier in this section) for the later initialization of the pageable memory pool. Figure 1-3 now shows the layout of main memory.

Figure 1-1

Main Memory as bootstrap1 Receives Control

Main Memory Before Loading Collection 1

Figure 1-3

Main Memory After Loading Collection 1

Collection 1 is now initialized. All of the segments now existent are unpaged, and hence, no page faults are taken until creation of the FSDCT segment. Before this happens, though, the procedure init\_sst runs. This procedure creates the core map (see the <u>Storage System PLM</u>, Order No. AN61) among other data bases, and creates a core used list, consisting of all of the core blocks that lie entirely within the free region left by bootstrap1. Thus, the first few page faults on the FSDCT and the new paged descriptor segment are resolved in this area. If there is not enough room left to resolve these page faults, Multics will crash during initialization.

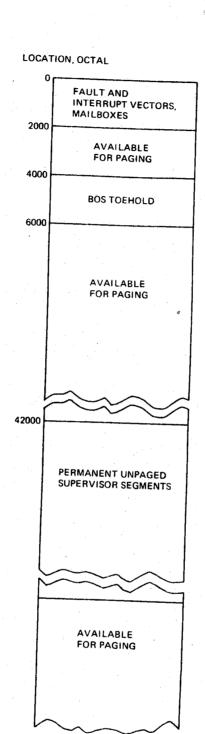

Once there is a minimal core used list, and paging is operative, the procedure make\_segs\_paged copies each of the segments at the high end of main memory (the temp, init, and paged supervisor segs) into paged segments, for which it has asked make\_sdw to fabricate AST entries based upon the SLTE information available. These segments are copied in descending address order, starting at the high end of memory. As each full page is copied, i.e., one core block worth of information from the high end of memory has been copied into paged segments, the core block is freed, i.e., added to the core used list (the pageable memory pool). During this operation, the amount of pageable memory increases due to this freeing. The occasional paged segments tends to decrease the amount of wiring of available memory. If at any time, the amount of available pageable memory becomes zero, Multics will crash. The time when the minimum amount of pageable memory is available during this operation "core high water mark" of is known as the initialization.

As each of these segments is successfully copied. descriptor for the new paged segment replaces the descriptor for the unpaged segment in both the old (unpaged) descriptor segment and the new (paged) one. This allows the main memory occupied by the old unpaged copy to be freed immediately. The configuration deck, the SLT, and its Name Table are also copied into paged they are not contiguous with the segments at the segments. As high end of main memory whose memory is freed sequentially, their main memory is not freed at this time. After all of this copying is done, a procedure called collect\_free\_core runs. This program does a marking-type garbage collection of main memory. All core found to be not in the core used list, but to contain a blocks word of an unpaged segment, are marked. The entire core map is scanned, and any core block which is marked is unmarked. Any core block that is found unmarked, and is in a currently configured (ON) system controller is added to the core used list. This frees the core formerly occupied by bootstrap1, the SLT and SLT name table and the physical record buffer before they were

made paged, and any other pages never freed (e.g., the page at 2000). The unpaged descriptor segment is then freed, after the new one is in use.

One may note that the physical record buffer becomes paged, and is wired. The initialization tape reader, tape\_io, constructs DCW lists that are cognizant of the fact that this segment is not contiguous in memory.

From this point on, main memory control is completely under control of page control. Figure 1-4 shows the current layout of main memory. The unpaged supervisor segments remain in place throughout Multics. Wired as well as unwired segments share the pageable core pool. The deletion of init\_segs removes the physical record buffer from memory (unwiring and deleting it).

Shutdown deletes segments, but has no particular effect on main memory allocation.

# SUMMARY OF INITIALIZATIONS CALLS

This subsection is a summary of all of the calls made by bootstrap2, initializer, and init\_collections, the latter two being simple call dispatchers. This is intended to give an overview of the sequence of initialization before we describe these procedures in detail in the next two sections.

bootstrap1 transfers to bootstrap2, collection 1 having been loaded.

call slt\_manager

ascertain segment number of prelinker.

call pre\_link 1

prelink collection 1.

call initialize\_faults\$fault\_init\_one

sets up interim fault handling, most faults set to be fatal. Page and segment faults legal. Interim clock reading set up.

call iom\_data\_init

IOM manager initialization. Channel tables and overhead channels set up. Mailboxes initialized.

Figure 1-4

Main Memory After make\_segs\_paged

call oc\_data\_init

Initializes operator's console data bases. Reports to IOM manager for device index assignment.

call scas\_init

system controller addressing segment (SCAS) set up. Processor and system controller configuration data processed and interpreted. RSW and RSCR instructions issued to verify this data.

call scs\_init

interrupt assignments ascertained. System masks fabricated. Process interrupt handlers set up. Interrupt handler entry points set up for interrupt interceptor. Control processor relations set up.

call trace\_init

debugging printer/tape facility set up, if selected. Reports to IOM manager for device assignment.

call init\_sst

system segment table (SST) organized. Core and PD maps and used lists set up. AST entries created, threaded into free lists. Core left by bootstrap1 freed.

call initialize\_faults\$interrupt\_init