SCIENTIFIC DATA SYSTEMS

Reference Manual

SDS 930 Computer

# SDS 930 BASIC INSTRUCTIONS

| Mnemonic                      | Octal Code                             | Name                                                | Page<br><u>Ref.</u> | Mnemonic                      | Octal Code                             | <u>Name</u>                                                                       | Page<br><u>Ref.</u> |

|-------------------------------|----------------------------------------|-----------------------------------------------------|---------------------|-------------------------------|----------------------------------------|-----------------------------------------------------------------------------------|---------------------|

| CENTRAL PRO                   | CESSOR                                 |                                                     |                     | BRANCH                        |                                        |                                                                                   |                     |

| LOAD, STORE                   |                                        |                                                     |                     | BRU A,T<br>BRX A,T            | 01<br>41                               | Branch Unconditionally Increment Index &Branch                                    | 14<br>14            |

| STA A,T                       | 35<br>36                               | Store A<br>Store B                                  | 8                   | BRM A,T<br>BRR A,T            | 43<br>51                               | Mark Place &Branch<br>Return Branch                                               | 15<br>15            |

| STX A,T<br>XMA A,T<br>LDX A,T | 37<br>62<br>71                         | Store Index<br>Exchange M and A<br>Load Index       | 8<br>9<br>8         | TEST/SKIP                     |                                        |                                                                                   |                     |

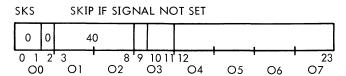

| LDB A,T<br>LDA A,T            | 75<br>76                               | Load B<br>Load A                                    | 8<br>8              | SKS A<br>SKE A,T              | 40<br>50                               | Skip if Signal Not Set<br>Skip if A Equals M                                      | 27<br>15            |

| EAX A,T                       | 77                                     | Copy Effective Address into index                   | 8                   | SKB A,T<br>SKN A,T            | 52<br>53                               | Skip if M and B Do Not Compare Ones Skip if M Negative                            | 16<br>16<br>16      |

| ARITHMETIC                    |                                        |                                                     |                     | SKR A,T<br>SKM A,T<br>SKA A,T | 60<br>70<br>72                         | Reduce M, Skip if < 0 Skip if A = M on B Mask Skip if M and A Do Not Compare Ones | 15<br>16            |

| SUB A,T<br>ADD A,T            | 54<br>55                               | Subtract M from A Add M to A                        | 10<br>9<br>10       | SKG A,T<br>SKD A,T            | 73<br>74                               | Skip if A Greater Than M<br>Difference Exponents; Skip                            | 15<br>16            |

| SUC A,T<br>ADC A,T<br>MIN A,T | 56<br>57<br>61                         | Subtract with Carry Add with Carry Memory Increment | 9<br>9              | SHIFT<br>LRSH N, T            | 0.66.24888                             | Logical Right Shift AB                                                            | 17                  |

| ADM A, T<br>MUL A, T          | 63<br>64                               | Add A to M<br>Multiply                              | 9<br>10             | RSH N, T<br>RCY N, T          |                                        | Right Shift AB Right Cycle AB                                                     | 17<br>17            |

| DIV A,T                       | 65                                     | Divide                                              | 11                  | LSH N,T<br>LCY N,T            |                                        | Left Shift AB<br>Left Cycle AB                                                    | 18<br>18            |

| LOGICAL                       |                                        |                                                     |                     | NOD N, T                      | 0 67 10XXX                             | Normalize; Decrement X                                                            | 18                  |

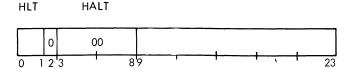

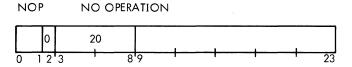

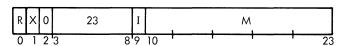

| ETR A,T<br>MRG A,T            | 14<br>16                               | Extract<br>Merge                                    | 11<br>11            | HLT                           | 00                                     | Halt                                                                              | 18                  |

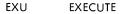

| EOR A,T                       | 17                                     | Exclusive Or                                        | 11                  | NOP<br>EXU A,T                | 20<br>23                               | No Operation<br>Execute                                                           | 19<br>19            |

| REGISTER CHA                  | NGE                                    |                                                     |                     | BREAKPOINT 1                  |                                        | 5 1 1 1 1 1 1 1 T                                                                 |                     |

| CLA<br>CLB<br>CAB             | 0 46 00001<br>0 46 00002<br>0 46 00004 | Clear A<br>Clear B<br>Copy A into B                 | 12<br>12<br>12      | BPT 4<br>BPT 3<br>BPT 2       | 0 40 20040<br>0 40 20100<br>0 40 20200 | Breakpoint No. 4 Test<br>Breakpoint No. 3 Test<br>Breakpoint No. 2 Test           | 19<br>19<br>19      |

| CBA<br>XAB                    | 0 46 00014<br>0 46 00014               | Copy B into A Exchange A and B                      | 12<br>12            | BPT I<br>OVERFLOW             | 0 40 20400                             | Breakpoint No. 1 Test                                                             | 19                  |

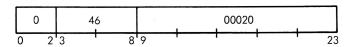

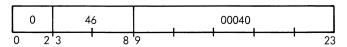

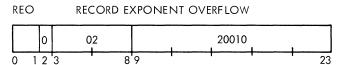

| CBX<br>CXB                    | 0 46 00020<br>0 46 00040               | Copy B into Index<br>Copy Index into B              | 13<br>13            | ROV<br>REO                    | 0 02 20001<br>0 02 20010               | Reset Overflow<br>Record Exponent Overflow                                        | 19<br>18            |

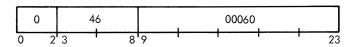

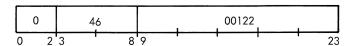

| XXB<br>STE                    | 0 46 00060<br>0 46 00122               | Exchange Index and B Store Exponent                 | 13                  | OVT<br>INTERRUPT              | 0 40 20001                             | Overflow Test; Reset                                                              | 19                  |

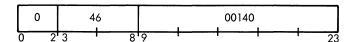

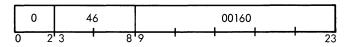

| LDE<br>XEE<br>CXA             | 0 46 00140<br>0 46 00160<br>0 46 00200 | Load Exponent Exchange Exponents Copy Index into A  | 14<br>14<br>13      | EIR                           | 0 02 20002                             | Enable Interrupts                                                                 | 23                  |

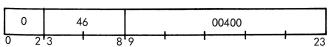

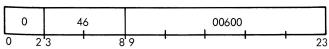

| CAX<br>XXA                    | 0 46 00400<br>0 46 00600               | Copy A into Index Exchange Index and A              | 13<br>13            | DIR<br>AIR<br>IDT             | 0 02 20004<br>0 02 20020<br>0 40 20002 | Disable Interrupts Arm Interrupts Interrupt Disabled Test                         | 23<br>23<br>23      |

| CNA<br>BAC                    | 0 46 01000<br>0 46 00012               | Copy Negative into A Copy B into A, Clear B         | 14<br>13            | IET                           | 0 40 20002                             | Interrupt Enabled Test                                                            | 23                  |

| ABC<br>CLR                    | 0 46 00005<br>0 46 00003               | Copy A into B, Clear A Clear AB                     | 13<br>12            | MEMORY EXTE                   | 0 06 200SR                             | Set Extension Register                                                            | 19                  |

| CLX                           | 2 46 00000                             | Clear X                                             | 13                  |                               | 0 40 4000T                             | Extension Register Test                                                           | 20                  |

Legend:

A = address; \*A = indirect address; T = tag field; N = number of shifts

Price: \$2.50

# SDS 930 COMPUTER REFERENCE MANUAL

February 1966

$SCIENTIFIC\ DATA\ SYSTEMS/1649\ Seventeenth\ Street/Santa\ Monica,\ California/(213) UP1-0960$

## **REVISIONS**

This publication, SDS 90 00 64D, dated February 1966, is a revision of the SDS 930 Computer Reference Manual, SDS 90 00 64C. Changes to the previous manual are indicated by a vertical line in the margin of the page.

# **RELATED PUBLICATIONS**

| Title of Manual                                       | Publication<br>Number |

|-------------------------------------------------------|-----------------------|

| SDS ALGOL 60 Reference                                | 90 06 99              |

| SDS 900 Series FORTRAN II Reference                   | 90 00 03              |

| SDS 900 Series FORTRAN II Operations                  | 90 05 87              |

| SDS MONARCH Reference                                 | 90 05 66              |

| SDS SYMBOL and META-SYMBOL Reference                  | 90 05 06              |

| SDS 920/930 Programmed Operators Technical            | 90 00 20              |

| SDS 930 Computer EXAMINER Diagnostic System Technical | 90 00 97              |

| SDS 900 Series Utility and Debug Package (AID)        | 01 20 13              |

| SDS Project Management System Reference               | 90 08 18              |

| SDS SORT/MERGE Reference                              | 90 09 97              |

| SDS Business Language Reference                       | 90 10 22              |

# CONTENTS

| I.   | GENERAL DESCRIPTION                                      | IV. | (Continued)                                      |

|------|----------------------------------------------------------|-----|--------------------------------------------------|

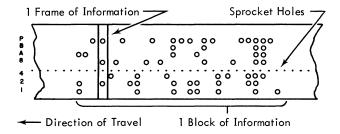

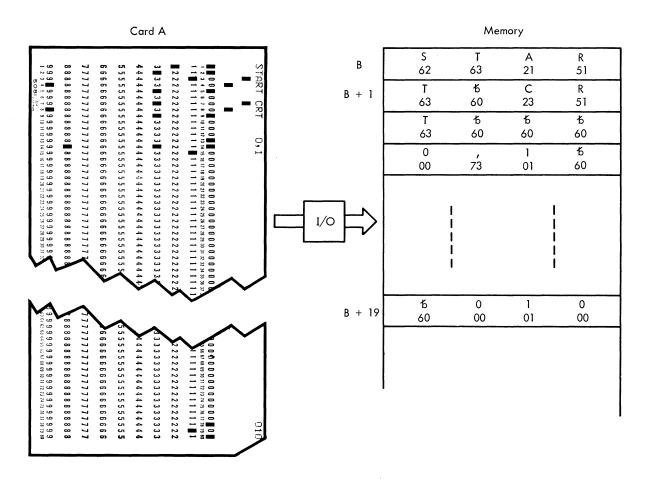

|      | Introduction1                                            |     | Peripheral Equipment Description 49              |

|      | SDS 930 Registers                                        |     | Paper Tape Input/Output                          |

|      | SDS 930 Memory 4                                         |     | Card Input/Output                                |

|      | Memory Word Formats 4                                    |     | Magnetic Tape Input/Output 56                    |

|      | Special Characteristics 6                                |     | Line Printer                                     |

| II.  | MACHINE INSTRUCTIONS                                     |     |                                                  |

|      |                                                          |     | APPENDICES                                       |

|      | Introduction 8                                           |     |                                                  |

|      | Load/Store Instructions                                  |     |                                                  |

|      | Arithmetic Instructions 9                                |     | SDS Character Codes                              |

|      | Logical Instructions                                     |     | Table of Powers of Two                           |

|      | Register Change Instructions                             |     | Octal-Decimal Integer Conversion Table A-3       |

|      | Branch Instructions                                      |     | Octal-Decimal Fraction Conversion Table A-7      |

|      | Test and Skip Instructions                               |     | Two's Complement Arithmetic A-10                 |

|      | Shift Instructions                                       |     | Optional Equipment                               |

|      | Control Instructions                                     |     | Data Multiplexing System                         |

|      | Breakpoint Tests                                         |     | Memory Interface Connection                      |

|      | Overflow Instructions                                    |     | Automatic Power Fail-Safe                        |

|      | Memory Extension Instructions                            |     | Memory Parity Interrupts                         |

|      | Floating Point Operations 20                             |     | Real-Time Clock                                  |

| III. | INTERRUPT SYSTEM                                         |     | Programmed Operator Instructions A-17            |

| 111. | INTERROFT STSTEM                                         |     | Channel Memory Access Priority A-19              |

|      | Delayity Intermed States                                 |     | Division Instruction                             |

|      | Priority Interrupt Operations 21                         |     | Instruction List – Functional Categories A-20    |

|      | Priority Interrupt Operations                            |     | Instruction List - Numerical Order A-25          |

|      | Interrupt Control                                        |     | Instruction List – Alphabetical Order A-29       |

|      | Enable/Disable Interrupt Instructions                    |     |                                                  |

|      | Arming Feature (Optional)                                |     |                                                  |

|      | Channel Interrupt Designations24                         |     | FIGURES                                          |

|      | End-of-Word/End-of-Transmission Interrupt                |     | TIGORES                                          |

|      | Operations; Compatible Mode 24.                          |     |                                                  |

|      | Count Equals Zero/End-of-Record;                         |     |                                                  |

|      | Extended Mode                                            |     | SDS 930 Computer (Frontispiece) iv               |

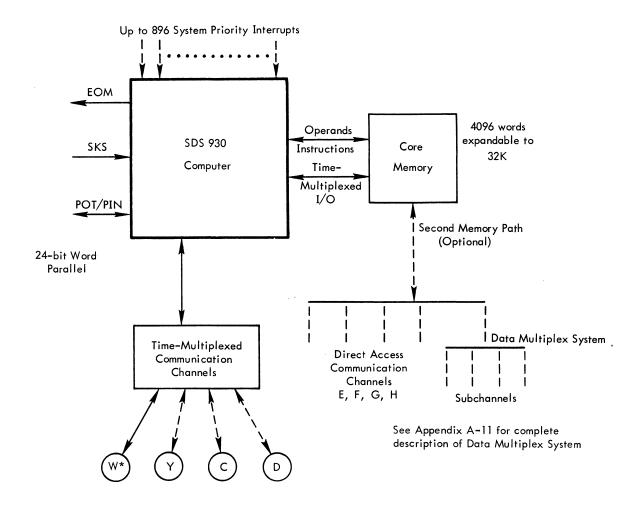

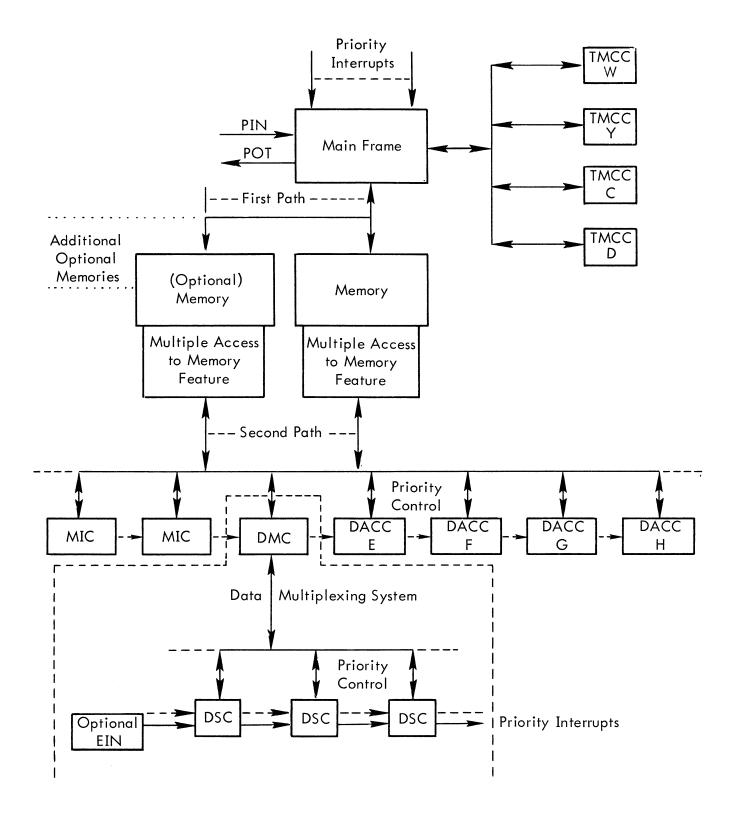

|      | 27.01.000 11.000 11.11.11.11.11.11.11.11.11.11.11.11.11. | 1-1 | SDS 930 Computer Configuration 2                 |

| IV.  | INPUT/OUTPUT INSTRUCTIONS 25                             | 1-2 | Basic Register Flow Diagram 3                    |

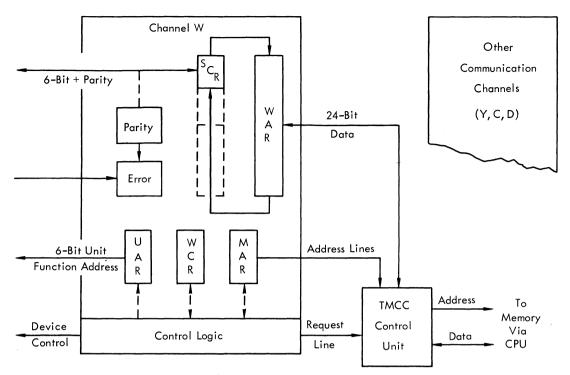

|      |                                                          | 4-1 | SDS 930 Time-Multiplexed Communication           |

|      | Introduction                                             |     | Channel, Block Diagram                           |

|      | Direct Memory Access System 26                           | 4-2 | SDS 930 Direct Access Communication              |

|      | Primary Input/Output Instructions 26                     |     | Channel, Block Diagram                           |

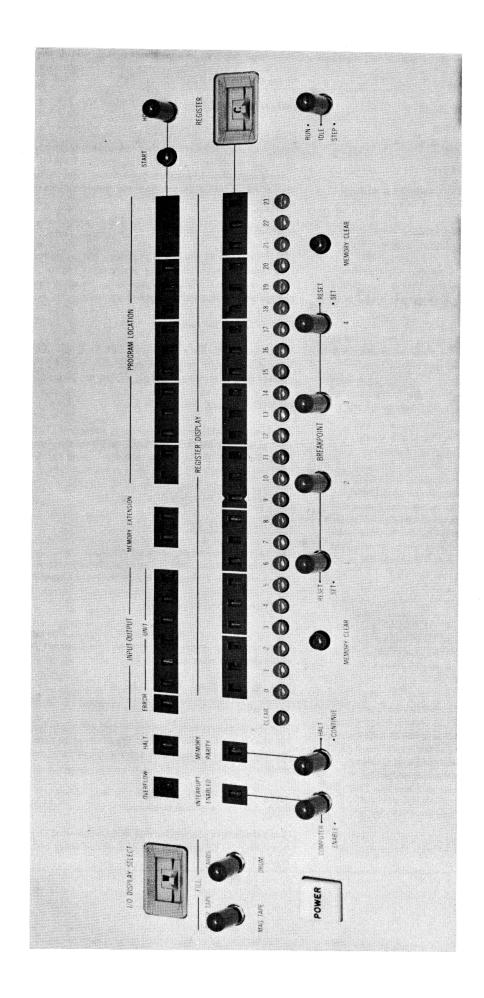

|      | Communication Channel Input/Output 28                    | 4-3 | SDS 930 Computer Control Panel 45                |

|      | Communication Channel EOM 31                             | 4-4 | Card Read Into Memory in Hollerith 52            |

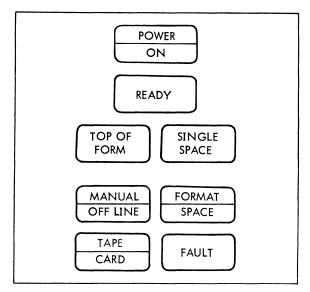

|      | Standard EOM/EOD Instructions 33                         | 4-5 | Printer Control Indicator Lights and Switches 62 |

|      | Compatible/Extended Input/Output Modes 34                | A-1 | SDS 930 Computer Overall Configuration A-12      |

|      | Input/Output Class EOM/EOD 34                            |     |                                                  |

|      | Terminal Functions; Extended Mode 35                     |     |                                                  |

|      | Channel and Device SKS                                   |     | TABLES                                           |

|      | Single–Word Data Transfer Via                            |     |                                                  |

|      | Channels W and Y                                         |     | ,                                                |

|      | Direct Parallel Input/Output Instructions 41             |     |                                                  |

|      | Single-Bit Input/Output41                                | 3-1 | Interrupt Location Assignments 22                |

|      | Communication Channel Programming 42                     | 4-1 | Unit Address Codes                               |

|      | Control Console 44                                       | 4-2 | Format Control Characters                        |

SDS 930 Computer

## I. GENERAL DESCRIPTION

#### INTRODUCTION

The SDS 930 is a high-speed, low-cost, general-purpose digital computer with the following characteristics:

- 24-bit word plus parity bit

- Binary arithmetic

- Single address instructions with

Index Register Indirect Addressing Programmed Operators

Basic core memory 4,096 words, expandable to 32,768 words, all addressable with

0.7 microsecond access time1.75 microsecond cycle time

- Memory overlap between Central Processor and I/O with two memory banks

- Memory available in 4, 8, and 16 K banks

- Multi-precision programming facility

- Typical execution times (including memory access and indexing)

#### Fixed-Point Operations (in microseconds)

Add 3.5 Multiply 7.0

#### Floating-Point Operations (in microseconds)

24-bit Fraction 39-bit Fraction (plus 9-bit Exponent) (plus 9-bit Exponent)

Add

77

92

Multiply

54

147

- Program interchangeability with other SDS 900 Series Computers

- Parity checking of all memory and input/output operations

- Priority Interrupt System

SDS I/O Options Interrupts 2 levels standard, 38 optional

System Interrupts, 896 optional

- Optional power fail-safe feature permits saving contents of memory and programmable registers in case of power failure.

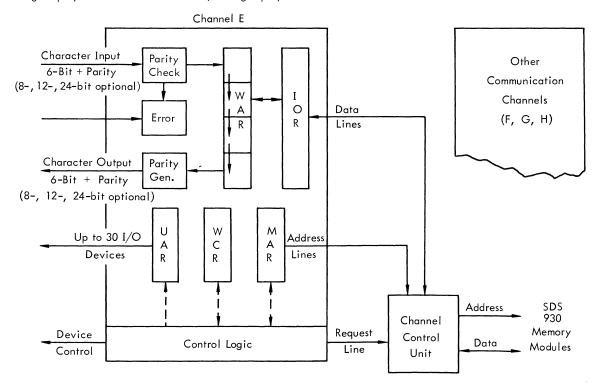

- Up to four I/O communication channels (with optional interlacing capability), time-multiplexed with computer operation, providing input/output rates of up to one word per 3.5 microseconds

- An optional Direct Memory Access System that allows input/output transfer to occur simultaneously with computer memory access, providing input/output rates of up to one word per 1.75 microseconds

- One to four Direct Access Communication Channels that incorporate the Direct Memory Access System

- Data Multiplex Channel that uses direct memory access connection and accepts/transmits information from external devices, or subchannels, which may operate simultaneously; thus, externally controlled and sequenced equipment may perform input/output buffering and control operations rather than the computer.

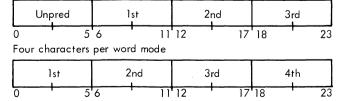

- Time-Multiplexed Input/Output Channels operate upon either words or characters. A 6-bit character is the standard character size; 6- and 12-bit characters, or 6-, 12-, and 24-bit characters can be specified as desired. Direct Access Channels operate upon words and characters. These channels accept 6-, 8-, 12-, and 24-bit characters. The number of characters per word is specified by the external device.

- Input/output with Scatter-Read and Gather-Write facility

- Standard input/output

Time-Multiplexed Communication Channel (without interlace)

Control Console

Optional input/output devices

Automatic typewriter

Photoelectric paper-tape reader and paper-tape punch, and spooler mounted on cart

MAGPAK Magnetic Tape System

Magnetic-tape units (IBM-compatible; binary and BCD)

Punched-card equipment

Line printers, graph plotters

Typewriter with electromechanical paper-tape reader and punch, auxiliary disc files

\* W-Buffer Standard; W Channel optional

Figure 1-1. SDS 930 Computer Configuration

Communications equipment, teletype consoles, display oscilloscopes

A/D converters, digital multiplexer equipment, and other special system equipment

- FORTRAN II and symbolic assembler as part of complete software package

- All-silicon semiconductors

- Operating temperature range: 10° to 40°C

- Dimensions: 124 inches x 25-1/2 inches x 65 inches

- Power: 3 kva

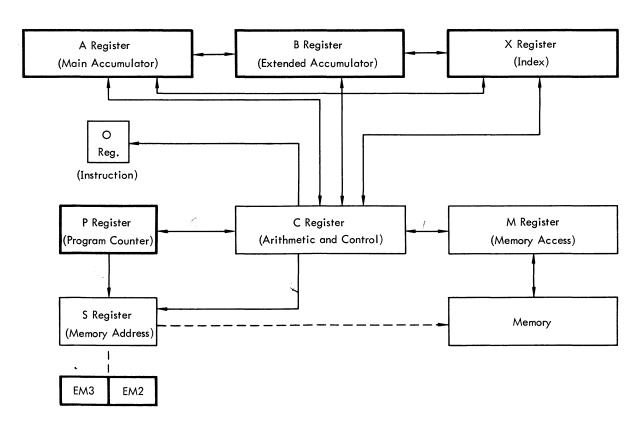

#### SDS 930 REGISTERS

The 930 Central Processor contains the following arithmetic and control registers. They are full-word, 24-bit registers except as noted.

AVAILABLE TO THE PROGRAMMER (see Fig. 1-2, dark lines)

The A Register is the main accumulator of the computer. The B Register is an extension of the A Register. The B Register contains the less significant portion of double-length numbers.

The Index Register, X, used in address modification, is a full-word register. Indexing operations occur only with the least significant 14 bits.

The P Register is a 14-bit register that contains the memory address of the current instruction. Unless modified by the program, the contents of P increase by one at the completion of each instruction.

The Memory Extension Registers, EM3 and EM2, are 3-bit registers that specify the portion of extended memory being used.

NOT AVAILABLE TO THE PROGRAMMER (see Fig. 1–2, light lines)

The S Register is a 14-bit register that contains the address of the memory location to be accessed for instructions or data. The address is augmented by one of the Memory Extension Registers.

The C Register is an arithmetic and control register used in multiply, divide, and other operations. All instructions come from memory to the C Register before decoding. Address modification and parity generation/detection take place in the C Register.

The O Register is a 6-bit register that contains the instruction code of the instruction being executed.

The M Register is a 24-bit register that holds each word as it comes from memory. Recopying of a word into memory takes place from the M Register.

Figure 1-2. Basic Register Flow Diagram

#### SDS 930 MEMORY

Core memory is expandable from 4,096 to 32,768 words. Word length is 24 bits plus parity. The address field in the instruction format is 14 bits long, allowing direct access of up to 16,384 words. The Memory Extension System provides direct access to the total 32,768 words.

Memory is available in 4,096-, 8,192-, and 16,384-word banks.

As an optional feature, if a power loss is detected, the computer may be interrupted and the transient, programmable registers stored to provide complete fail-safe capability. With this option, power failure causes no loss of information.

Even parity is automatically generated or checked during each read/write cycle. A control panel switch may be set to halt the computer automatically in case of parity error detection.

The memory is cyclic, or "wrap-around", for each 16,384 words being addressed. An attempt to access from a location whose address is greater than that available results in an access of all zeros. An attempt to store into such a location results in a "no-op" operation, with the next instruction in sequence being executed.

#### MEMORY EXTENSION SYSTEM

The Memory Extension System, containing two memory extension registers, allows addressing of memories greater than 16,384 words. The program loads either or both of the Extend Memory Registers and activates them as desired. Each register contains 3 bits, or one octal digit, that can become the most significant, or fifth, digit of any operand address.

The program uses the first extension register, EM3, by calling for an address with a 1, 1 in the most and next most significant address bits, respectively (a "3" for the most significant octal digit). The program calls for EM2, the second extension register, by setting the same two address bits to 1,0 (a "2" for the most significant octal digit). Via memory extension instructions, the program can set each of the registers to a desired "5th digit" and can test the current setting of each register. Once set, the contents of either register remain set until changed by program or by pressing the START button.

The program always addresses the first 8,192 words of core, 00000-17777, directly without regard to the Extend Memory Registers. Whenever the operator initializes the computer (presses START), the computer presets a 3 in EM3 and a 2 in EM2. This allows the programmer to address the first 16,384 words of core, 00000-37777, without being concerned with the extension system.

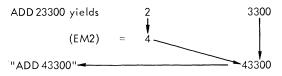

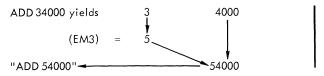

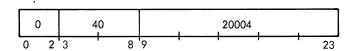

Example 1. By previously setting EM2 to 4, the program adds the contents of location 43300 to the A Register by executing ADD 23300. The "2" calls for register EM2:

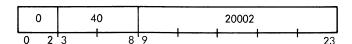

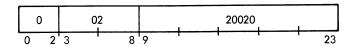

Example 2. EM3 setting is 5; EM2 setting is 7:

When  $(EM3) \neq 3$ , the computer lights the EM3 light on the control panel. When  $(EM2) \neq 2$ , the computer lights the EM2 light on the control panel. When executing the MARK PLACE AND BRANCH (BRM) instruction, the computer records the contents of EM3, EM2, and the Overflow Indicator in the mark location. BRM stores overflow in bit 0 of the mark; it stores the contents of EM3 in bits 3 through 5 and the contents of EM2 in bits 6 through 8. Bits 1 and 2 are unpredictable; bit 9 is zero.

#### Memory Write Lock-Out Feature (Optional)

Permanent memory protection for selected areas of memory in the SDS 930 Computer is provided by a memory lock-out feature, which is controlled either manually by switches or by the program with a lock-out register, protects the contents of memory from inadvertent destruction by operating programs.

The entire memory is divided into 2048 word blocks. This first block, from 0000 to 2047, is further divided into four subblocks of 512 words each. Each of these blocks can be individually protected by turning on the appropriate switch with the manual-controlled option or placing a one in the appropriate position of the lock-out register with the program-controlled option.

Read operations are always allowed, but if a program or I/O channel attempts to store or write into a protected block of memory, an internal interrupt occurs to octal location 35. The memory cell referenced is not altered. Therefore, not only is memory protected, but also the supervisory program is notified that an attempt to write into an interlocked area has occurred.

#### **MEMORY WORD FORMATS**

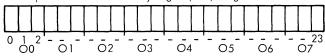

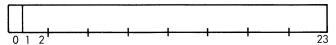

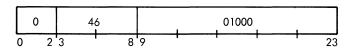

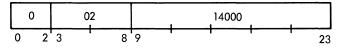

A computer word is 24 binary digits (bits) long.

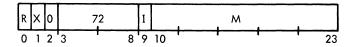

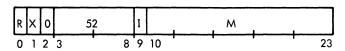

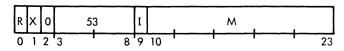

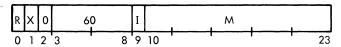

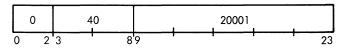

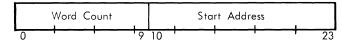

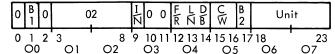

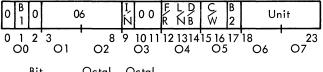

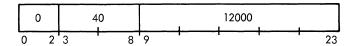

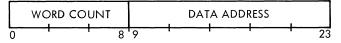

The format above numbers the bits from the left, or most significant end of the word, to the right, or least significant end of the word. This numbering format is the basis of references to bit positions or bit numbers. Octal notation most easily describes the contents of the 24 bits of a word. Thus, one octal digit, 0 through 7, represents three binary digits. For example, the octal number, 01234567, represents its binary equivalent, 000 001 010 011 100 101 110 111.

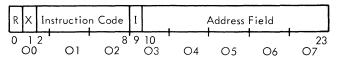

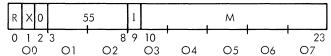

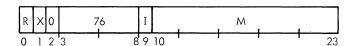

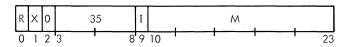

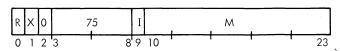

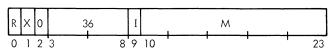

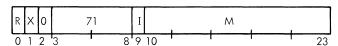

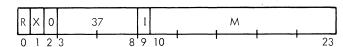

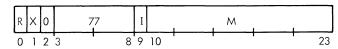

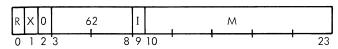

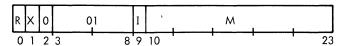

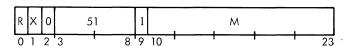

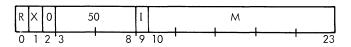

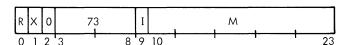

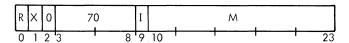

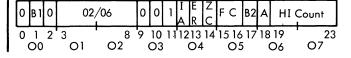

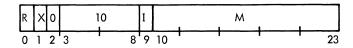

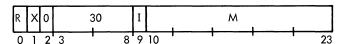

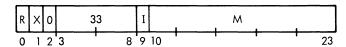

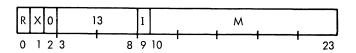

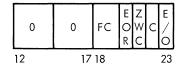

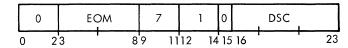

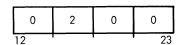

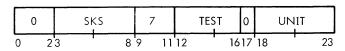

The computer instruction word format is:

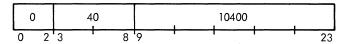

Bit position 0 contains the Relative Address Bit. Standard loading programs use this bit; central processor decoding logic does not use or sense this bit. A 1-bit (octal value of 4) in this position causes some standard loading programs to add the assigned location of the instruction to the address field contents prior to actual storage into the assigned location.

Bit position 1 (octal value of 2) contains the Index Register Bit.

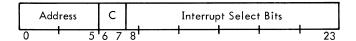

Bit positions 2 through 8 contain the Instruction Code Field which determines the operation to be performed. The Programmed Operator facility uses bit position 2 (octal value of 1); it is part of the "Tag" Field (bit positions 0 - 2).

Bit position 9 (octal value of 4) contains the Indirect Address Bit.

Bit position 10 (octal value of 2) contains the Memory Extension Bit that controls addressing above location 8,191. A 1-bit in this position activates the memory extension logic.

Bit positions •10 through 23 contain the Address Field which usually represents the location of the operand called for by the instruction code.

The following examples use standard assembler format in expressing instructions. This format is:

#### where:

LDA is a representative mnemonic instruction code, 1000 is a representative address that is written decimally, and T is a 1-digit octal integer that represents the Tag Field.

To express indirect addressing (that is, a "one" in the Indirect Address position), the programmer prefixes an asterisk to the address field:

The interpretation of the Tag Field (bit positions 0 - 2) integer, T, when required, is composed of the sum of the octal values of its constituents; it is written as follows:

| Tag Field Integer T | Interpretation                                           |  |

|---------------------|----------------------------------------------------------|--|

| 0 (or blank)        | No Relative Address, No Index,<br>No Programmed Operator |  |

| 1                   | Programmed Operator                                      |  |

| 2                   | Index                                                    |  |

| 3                   | Programmed Operator and Index                            |  |

| 4                   | Relative Address                                         |  |

| 5                   | Programmed Operator and Relative Address                 |  |

| 6                   | Both Relative Address and Index                          |  |

| 7                   | Programmed Operator, Index, and Relative Address         |  |

Tag Fields of 1,3,5,7 are usually replaced by a specific Programmed Operator mnemonic along with Tag Fields of 0,2,4,6, respectively.

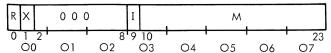

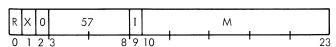

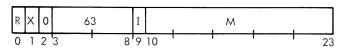

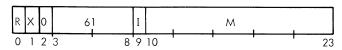

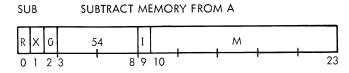

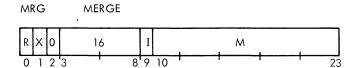

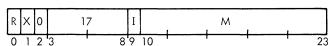

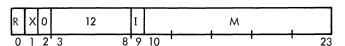

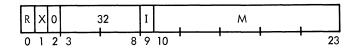

In the explanation of specific instructions, the format used for the instruction word is:

where R, X, and I are as defined previously, 000 represents the instruction, and M represents a generalized memory address.

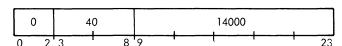

#### FIXED-POINT FORMAT

Fixed-point data words have the format:

Numbers held in this format are 8-digit, octal numbers, with the sign incorporated as the "leading bit" in the most significant octal digit. Bit position 0 is the sign bit, with negative numbers having a "1" in bit position 0 and positive numbers having a "0" in bit position 0.

The memory holds fixed-point numbers as 23-bit fractions with an assumed binary point to the left of bit position one. Numbers held in one word have the equivalent precision of over six decimal digits. The range of values of the fixed-point format is from minus one to slightly less than plus one. Scaling is used in handling numbers during computation.

Programmers sometime consider fixed-point numbers to be integers, with the binary point to the right of bit position 23. The range of integer values is from  $-2^{23}$  to  $+2^{23}-1$ .

The memory holds negative, fixed-point numbers in two's complement form; the computer operates on these numbers arithmetically in a two's complement number system. See Appendix A-10 for a discussion of two's complement arithmetic.

#### FLOATING-POINT FORMAT

SDS offers standard programmed operator packages for performing double and single-precision floating-point arithmetic. The following paragraphs explain the standard floating-point number formats.

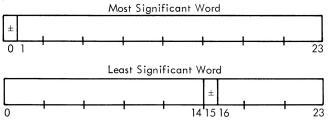

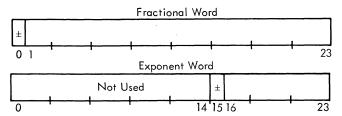

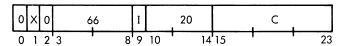

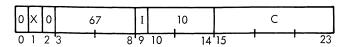

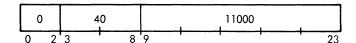

#### Double-Precision Floating-Point Format

The fractional portion of a double-precision, floating-point number is a 39-bit, proper fraction, with the leading bit being the sign bit and the assumed binary point just to the left of the most significant magnitude bit (bit 1 of the upper word). The floating-point exponent is a 9-bit integer, with the leading bit being the sign. The standard routines operate on both fraction and exponent in two's complement form. If F represents the contents of the fractional field and E represents the contents of the exponent field, the number has the form F x  $2^{E}$ .

Double-precision, floating-point numbers have over 11 decimal digits of precision and a decimally equivalent exponent range of  $10^{-77}$  to  $10^{+77}$ .

Standard Programmed Operators assume that the more significant word is in the A Register, or stored in memory location M+1, and that the less significant word is in the B Register, or stored in memory location M.

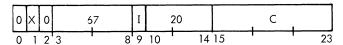

#### Single-Precision Floating-Point Format

The fractional portion of a single-precision, floating-point number is a 24-bit proper fraction, with the leading bit being the sign and the assumed binary point just to the left of the most significant magnitude bit. The floating-point exponent is a 9-bit integer with a leading sign bit. The standard routines operate on both fraction and exponent in two's complement form.

Single-precision, floating-point numbers have over six decimal digits of precision and a decimally equivalent exponent range of  $10^{-77}$  to  $10^{+77}$ .

Standard Programmed Operators assume that the fractional word is in A, or stored in memory location M+1, and that the exponent word is in B, or stored in memory location M. When entering a standard Programmed Operator routine, bits 0-14 of the exponent word are ignored.

#### SPECIAL CHARACTERISTICS

Certain computer features simplify programming and provide significant economies in memory and in program running time.

#### ADDRESS MODIFICATION

Indexing and indirect addressing, used singly or in combination, perform address modification. In both indexing and indirect addressing, the computer performs address modification after bringing the instruction from memory but before executing it. The instruction remains in memory in its original form. The results of indexing and/or indirect addressing form the "effective address".

#### INDEXING

The computer contains an Index Register for address modification. The use of this register to modify the address in an instruction does not increase instruction execution time.

If the content of the Index Bit in an instruction is a "one", the computer adds the contents of bits 10 through 23 of the X Register to the contents of the Address Field of the instruction prior to execution. This addition does not keep any overflow or carry beyond the fourteenth address bit.

The instruction set provides instructions for modifying and testing the X Register, and for transferring information between the X and B Registers, the X and A Registers, and the X Register and memory.

#### INDIRECT ADDRESSING

The Indirect Address Bit is in bit position 9 of the instruction. This bit determines whether the computer uses indirect addressing with the instruction being executed.

A zero in the Indirect Address Bit causes the computer to use the contents of the Address Field (bit positions 10 - 23 in the instruction) as the 5-digit, octal address requested by the instruction. A one in the Index Bit causes the computer to add the contents of the Index Register to this address to form the effective address.

A one in the Indirect Address Bit causes the computer to decode the contents of the effective address, accessed as described above, as if it were an instruction without an instruction code; that is, the address logic reinitiates address decoding, using the word in the effective location (the memory cell whose address is the effective address). This is an iterative process and provides multi-level indirect addressing. Indirect addressing adds one cycle time to instruction execution time for each level of addressing. The programmer can use indexing to modify indirect addressing at every level.

#### EXAMPLES: INDEXING AND INDIRECT ADDRESSING

The octal instruction code for LOAD A REGISTER (LDA), used in the examples, is 76.

| Location | Contents    | Effect                              |

|----------|-------------|-------------------------------------|

| Х        | 00000001    |                                     |

| 1000     | 00001001    |                                     |

| 1001     | 00041002    |                                     |

| 1002     | 00001003    |                                     |

| 1003     | 00000002    |                                     |

| 2000     | 0 76 01000  | (1000) = 00001001 -> A              |

| 2001     | 2, 76 01000 | (1000 + 1) = (1001) = 00041002 -> A |

| 2002     | 0 76 41000  | ((1000)) = (1001) = 00041002 -> A   |

| 2003     | 2 76 41000  | ((1000 + 1)) = ((1001)) = (41002) = |

|          |             | ((1002)) = (1003) = 00000002 -> A   |

#### Nomenclature

When discussing properties of the various instructions, including the indirect addressing facility, several terms describe specific locations or addresses.

The term "effective memory location" describes the location in memory from which the final operand is taken at the conclusion of all indirect addressing and indexing. This term is sometimes shortened to "effective location." It is the location whose address is the effective address.

The term "effective operand" means the contents of the effective memory location.

#### PROGRAMMED OPERATORS

Programmed Operators (called POP) permit the calling of subroutines with a single instruction of the same form as built-in machine instructions. The computer decodes the codes  $100_8 - 177_8$  as special instructions and transfers to a subroutine uniquely determined by the code. The computer records the address of the POP instruction at location 00000 together with an indirect address bit so that the program continuity may be maintained. By indirect addressing which refers to location 00000, which in turn refers to the POP instruction, the subroutine can gain access to the effective address of the operand associated with the POP instruction.

Programmed Operator subroutines are assigned three-letter, mnemonic designations in the same manner as built-in, machine instructions described in Section II. A program can use up to 64 Programmed Operators at any one time; however, since Programmed Operators are programmer-specified, the programmer can select alternate sets or sub-sets of the 64 Programmed Operators from program to program or from section to section of the same program. The total number of Programmed Operators is without limit; but it is inconvenient to use more than 64 in one program. Other computers in the SDS 900 Series maintain symbolic homogeneity through use of Programmed Operators. Mnemonic designations are identical in all computers. For example, while the designation "FLA" (for Floating ADD) may refer to a built-in, machine instruction in one computer, it refers to a Programmed Operator subroutine in another. This technique preserves the one-to-one instruction relationship; programs written for one 900 Series Computer can run on any other computer in the series.

A more detailed discussion and a list of standard SDS Programmed Operator routines are in Appendix A-17.

#### **OVERFLOW**

The Overflow Indicator in the computer permits the detection of erroneous arithmetic operations that occur during the execution of a program. The Overflow Indicator turns on if any of the following occur:

A sum or difference resulting from an addition or subtraction that cannot be contained within the A Register.

Multiplication of N by N where N is 40000000, the largest negative number that can be represented in an SDS 930 word. The A and B Registers cannot contain this product.

A division operation where the absolute value of the numerator is equal to (positive result) or larger than the absolute value of the denominator. The A Register cannot contain this quotient.

A left-shift operation that shifts a bit of absolute magnitude equal to one beyond position 1 of the A Register.

The instruction set (see Section II) contains instructions to reset, or test and reset the state of the Overflow Indicator.

The only instruction whose execution is altered by the state of the Overflow Indicator is OVERFLOW TEST (OVT), which skips if overflow is reset. Thus, the state of the Overflow Indicator can be ignored if desired. This is unlike some machines in which overflow causes a trap or halt.

To determine whether a particular instruction causes overflow, turn off the Overflow Indicator before executing the instruction. An instruction that may be used to turn on overflow is BRR. The instruction A BRR A, 4 "branches" to the next location and turns on the Overflow Indicator.

If the Overflow Indicator is on, it remains on until the appropriate instruction turns it off.

The execution of Programmed Operator, closed and interrupt subroutines automatically preserves the status of the Overflow Indicator. In the execution of a Programmed Operator instruction, the computer automatically places the status of the Overflow Indicator in bit position 0 of location 00000 and resets the Overflow Indicator. The instruction, MARK PLACE AND BRANCH (BRM), places the status of the Overflow Indicator in bit position 0 of the effective memory location and does not disturb the Overflow Indicator.

The instruction, RETURN BRANCH (BRR), automatically merges the contents of the Overflow Indicator with the contents of bit position 0 of the effective memory location and places the result in the Overflow Indicator. Section II contains a description of the above branch instructions.

#### SUBROUTINE EXECUTION

The SDS 930 Computer provides three distinct methods of sub-routine execution:

Normal closed subroutine where the input parameters are specified in appropriate registers such as the A Register

Interrupt subroutine that is entered as the result of an interrupt

Programmed Operator subroutine.

A program enters a normal closed subroutine via a MARK PLACE AND BRANCH (BRM) instruction; BRM automatically stores the contents of the Program Counter (P) Register and the status of EM3, EM2, and Overflow Indicator in the branch-to location. P Register value is the address of the BRM instruction. A RETURN BRANCH (BRR) instruction accomplishes the return to the main program; the BRR adds one to the stored P Register value and transfers control to that location. See Section II, Branch Group, for a description of the branch instructions.

Interrupt subroutines are closed subroutines that are initiated by the detection of program-controlling interrupts that automatically cause the specific interrupt subroutine to be entered. A BRM instruction enters an interrupt subroutine; the BRM automatically stores the contents of the P Register, EM3, EM2, and Overflow Indicator in the branch-to location. The value stored from the P Register is the address of the instruction to which program control should return after the interrupt is serviced by the interrupt subroutine. A BRANCH UNCONDITION-ALLY (BRU) instruction with indirect addressing returns control to the main program at the completion of the subroutine. BRU also clears the interrupt from the active state. Note that this differs from the normal closed subroutine return that uses the BRR (stored P value +  $1 \longrightarrow P$ ). The point in an execution cycle at which the interrupt routine-entering BRM executes has already caused the proper incrementing to occur.

## II. MACHINE INSTRUCTIONS

#### INTRODUCTION

This section describes SDS 930 instructions; the instructions are in functional groups. Lists of instructions in functional, numerical, and alphabetical order are in Appendices A-20, A-25, and A-29, respectively.

The following statements apply to the instruction descriptions:

All instruction times are in memory cycles, where each cycle is 1.75 microseconds, and include accessing the instruction and all required operands.

Parentheses denote "contents of." For example, "(A)" denotes "contents of the A Register."

Indexing and Indirect Addressing apply to all instructions except as noted. Indexing does not change the instruction execution time. Each level of indirect addressing requires one additional memory cycle.

The interrupt system can interrupt the program sequence at the end of any instruction except as noted.

Each instruction description specifies the registers affected.

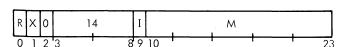

With the description of each instruction is a diagram representing the format of the instruction. Preceding this diagram is the mnemonic code that identifies the instruction and the name of the instruction.

#### **EXAMPLE:**

The letter M represents the address part of the instruction. Some instructions have octal numbers in the address field. These instructions do not refer to memory.

## LOAD/STORE INSTRUCTIONS

LDA LOAD A

LDA loads the contents of the effective memory location into the A Register.

Registers Affected: A

Timing: 2

STA STORE A

STA stores the contents of the A Register in the effective memory location.

Registers Affected: M

Timing: 3

LDB LOAD B

LDB loads the contents of the effective memory location into the B Register.

Registers Affected: B

Timing: 2

STB STORE B

STB stores the contents of the B Register in the effective memory location.

Registers Affected: M

Timing: 3

LDX LOAD INDEX

LDX loads the entire 24-bit contents of the effective memory location into the Index Register.

Registers Affected: X

Timing: 2

STX STORE INDEX

STX stores the entire 24-bit contents of the Index Register in the effective memory location.

Registers Affected: M

Timing: 3

EAX COPY EFFECTIVE ADDRESS INTO INDEX REGISTER

EAX copies the address of the effective memory location into the Index Register.

The addressing process for this instruction operates as in a Load A instruction, except that instead of obtaining the contents of the effective memory location, the effective memory address acts as the operand. This addressing process is sometimes called "immediate addressing." For example, if execution of this instruction occurs with a zero indirect address bit and a zero

in the index field, then the actual bit configuration in the address field of EAX copies into the Index Register.

The ten most significant bits of the Index Register are unaffected.

Registers Affected: X<sub>10-23</sub>

Timing: 2

XMA EXCHANG

EXCHANGE MEMORY AND A

XMA loads the contents of the effective memory location into the A Register and stores the contents of the A Register in the effective memory location.

Registers Affected: A, M

Timing: 3

#### **ARITHMETIC INSTRUCTIONS**

ADD

ADD MEMORY TO A

This instruction adds the contents of the effective memory location to the A Register and places the result in A.

After execution, bit position 0 of the Index (X) Register contains the carry from bit position 0 of the 24-bit adder. Therefore, the programmer should be careful when attempting to hold a full word quantity in X while performing an addition.

If both numbers are of the same sign but the sign of the result is opposite, overflow has occurred and the computer has set the Overflow Indicator.

Registers Affected: A, X<sub>0</sub>, Overflow Indicator

Timing: 2

ADC

ADD WITH CARRY

This instruction performs multi-precision addition. Using the instruction, ADD M TO A (55), the program adds the lower halves of the numbers first. ADD automatically retains the carry in the sign position of the X Register. The program then adds the two upper halves, using ADC. ADC is the same as ADD M TO A (55), except that it adds the carry bit previously generated into the low-order position.

After execution, bit position 0 of the Index (X) Register contains the carry from bit position 0 of the 24-bit adder. Therefore, the programmer should be careful when attempting to hold a full word quantity in X while performing an add with carry.

The computer automatically clears the Overflow Indicator prior to execution of this instruction since overflow resulting from the addition of the lower half of the multi-precision numbers is not meaningful.

If both numbers of the upper half are of the same sign but the sign of the result is opposite, an overflow has occurred and the computer sets the Overflow Indicator.

Registers Affected: A, X<sub>0</sub>, Overflow Indicator

Timing: 2

#### **EXAMPLE:**

Assume the A and B Registers contain a double-precision number to which the double-precision number, 15034166 12300000, in Locations 1021 and 1020 is added. The less significant half appears in 1020.

The sign position of B and the sign position of the less significant half (1020) are not considered signs but are binary digits. Thus, a double-precision number in AB consists of a sign ( $A_0$ ) and 47 binary digits ( $A_1$  -  $A_{23}$ ,  $B_0$  -  $B_{23}$ ). The number is in two s complement form.

#### The program is:

| Location  | Instruction | <u>A</u> | <u>B</u> | Carry |

|-----------|-------------|----------|----------|-------|

| (Prior to | Execution)  | 20314624 | 71510426 | _     |

| 2100      | XAB         | 71510426 | 20314624 | -     |

| 2101      | ADD 1020    | 04010426 | 20314624 | 1     |

| 2102      | XAB         | 20314624 | 04010426 | 1     |

| 2103      | ADC 1021    | 35351013 | 04010426 | 0     |

NOTE: Since the process is self-propagating, this instruction is used in performing additions of any precision. See the instruction, EXCHANGE A AND B (XAB), one of the Register Change Instructions, this section, for an explanation of its operation.

ADM ADD A TO MEMORY

ADM adds the contents of the A Register to the effective memory location and stores the result in the same location.

If both numbers are of the same sign but the sign of the result is opposite, an overflow occurs and the computer sets the Overflow Indicator. The contents of the A Register do not change.

Registers Affected: M, Overflow Indicator

Timing: 3

MIN MEMORY INCREMENT

MIN increases the contents of the effective memory location by one, and places the resulting sum in the same location. The contents of the A Register do not change.

CARAY

Overflow occurs with this instruction only when the contents of M are 37777777 before execution. In this case, 40000000 is the result in M.

Registers Affected: M, Overflow Indicator

Timing: 3

SUB subtracts the contents of the effective memory location from the A Register and places the result in the A Register.

After execution, bit position 0 of the Index (X) Register contains the carry from bit position 0 of the 24-bit adder. Therefore, the programmer should be careful when attempting to hold a full word quantity in X while performing a subtraction.

If both numbers are of the same sign after the subtrahend has been complemented for addition but the sign of the result is opposite, an overflow has occurred and the computer sets the Overflow Indicator.

Registers Affected: A, X<sub>0</sub>, Overflow Indicator

Timing: 2

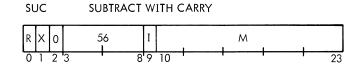

This instruction performs multiple precision subtractions. The program uses the instruction, SUBTRACT M FROM A (54), to subtract the lower half of the numbers first; this automatically retains the carry in the sign position of the X Register. This instruction (SUC) then subtracts the two upper halves. SUC is the same as SUBTRACT M FROM A (54), except for the retention of the carry bit previously generated in the sign position of the X Register.

After execution, bit position 0 of the Index (X) Register contains the carry from bit position 0 of the 24-bit adder. Therefore, the programmer should be careful when attempting to hold a full word quantity in X while executing SUC.

The Overflow Indicator automatically clears prior to execution of this instruction since overflow resulting from the subtraction of the lower half of the numbers is not meaningful.

If both numbers of the upper half of the subtraction are of the same sign after the computer complements the subtrahend for addition but the sign of the result is opposite, overflow occurs and the computer sets the Overflow Indicator.

#### **EXAMPLE:**

Assume that Registers A and B and memory location M contain a triple-precision number from which the triple-precision number in location L  $\pm$  2, L  $\pm$  1, and L is subtracted. The octal numbers 36142070 31567000 10000001 and 14236213 46120000 100000000 are in the following locations:

| <u>A</u>   | <u>B</u>   | <u>M</u> |

|------------|------------|----------|

| 36142070   | 31567000   | 10000001 |

| <u>L+2</u> | <u>L+1</u> | <u>L</u> |

| 14236213   | 46120000   | 10000000 |

The sign of one triple-precision number is in  $A_0$ , while its 71 binary digits are in  $A_{1-23}$ ,  $B_{0-23}$ , and  $M_{0-23}$ . The sign of the other number is in  $L_0$ , and its 71 digits are in  $L_{1-23}$ ,  $L^{+1}_{0-23}$ , and  $L^{+2}_{0-23}$ .

#### Execution:

| Location | Instruction | <u>A</u> | <u>B</u> . | Carry |

|----------|-------------|----------|------------|-------|

| 2100     | XMA M       | 10000001 | 31567000   | _     |

| 2101     | SUB L       | 00000001 | 31567000   | 0     |

| 2102     | XMA M       | 36142070 | 31567000   | 0     |

| 2103     | XAB         | 31567000 | 36142070   | 0     |

| 2104     | SUC L+1     | 63447000 | 36142070   | 1     |

| 2105     | XAB         | 36142070 | 63447000   | 1     |

| 2106     | SUC L+2     | 21704655 | 63447000   | 0     |

Answer: 21703654 63447000 00000001

NOTE: Since the process is self-propagating, this instruction performs subtractions of any precision. See EXCHANGE A AND B (XAB), under Register Change Instructions, this section, for explanation of its operation.

Registers Affected: A, X<sub>0</sub>, Overflow Indicator Timing: 2

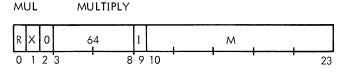

This instruction multiplies the contents of the A Register by the contents of the effective memory location and places the product in the A and B Registers with the more significant portion in A. The sign of the product is in  $A_0$ ; the bit in  $B_0$  is part of the product, not treated as a sign bit. Since the product contains at most 46 significant bits, the content of  $B_{23}$  is not significant and is zero.

The original contents of B do not affect the operation of the MULTIPLY instruction and are destroyed. If the contents of both the multiplier and multiplicand have the value 400000008, overflow occurs and the computer sets the Overflow Indicator.

Registers Affected: A, B, Overflow Indicator Timing: 4

EXAMPLE: Multiplication of 3 by 3

| After Execution | Double | B | Memory | Double | Doubl

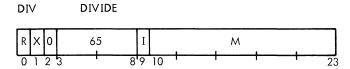

This instruction divides the contents of the A and B Registers, treated as a double-precision number, by the contents of the effective memory location and places the quotient in the A Register, with the remainder in the B Register.

No overflow occurs if  $-1 \le \frac{(A,B)}{M} \le 1$  (if the contents of A and B divided by the contents of the effective location are greater than or equal to minus one but strictly less than plus one). If the quotient exceeds these boundaries, overflow occurs and the computer sets the Overflow Indicator. In this latter case, the results are not arithmetically correct. See Appendix A-19 for a further description of division.

Registers Affected: A, B, Overflow Indicator

Timing: 10

#### **EXAMPLE:**

Division of 7 scaled at binary 46 by 3 at binary 23 is:

|                  | <u>A</u> | <u>B</u> | Memory   |

|------------------|----------|----------|----------|

| Before Execution | 00000000 | 00000016 | 00000003 |

| After Execution  | 00000002 | 00000001 | 00000003 |

#### **LOGICAL INSTRUCTIONS**

ETR EXTRACT

ETR performs a logical "AND" between corresponding bits of the A Register and the effective memory location and places the result in A. This instruction performs the operation bit by corresponding bit according to the following:

| <u>A</u> | M   | Result in A |

|----------|-----|-------------|

| 0        | 0   | 0           |

| 0        | 1   | 0           |

| 1        | 0   | 0           |

| 1        | 1 . | 1           |

Registers Affected: A

Timing: 2

#### **EXAMPLE:**

|                  | <u>A</u> | W        |

|------------------|----------|----------|

| Before Execution | 64231567 | 00777600 |

| After Execution  | 00231400 | 00777600 |

MRG performs a logical "Inclusive OR" between corresponding bits of the A Register and the effective memory location and places the result in A. This instruction performs the operation bit by corresponding bit, as follows:

| <u>A</u> | W | Result in A |

|----------|---|-------------|

| 0        | 0 | 0           |

| 0        | 1 | 1           |

| 1        | 0 | 1           |

| 1        | 1 | 1           |

Registers Affected: A

Timing: 2

#### **EXAMPLE:**

|                  | <u>A</u> | <u>M</u> |

|------------------|----------|----------|

| Before Execution | 06446254 | 02340712 |

| After Execution  | 06746756 | 02340712 |

EOR EXCLUSIVE OR

EOR performs a logical "Exclusive OR" between corresponding bits of the A Register and the effective memory location and places the result in A. This instruction performs the operation bit by corresponding bit, as follows:

| <u>A</u> | W   | Result in A |

|----------|-----|-------------|

| 0        | 0   | 0           |

| 0        | 1 . | 1           |

| 1        | 0   | 1           |

| 1        | 1   | 0           |

Registers Affected: A

Timing: 2

#### **EXAMPLE:**

|                  | <u>A</u> | M        |

|------------------|----------|----------|

| Before Execution | 34165031 | 70077021 |

| After Execution  | 44112010 | 70077021 |

The proper memory word configuration logically inverts selected bit positions of the A Register. If all "ones" appear in the memory word, a one's complement of A results.

#### **EXAMPLE:**

|                  | <u>A</u> | M       |

|------------------|----------|---------|

| Before Execution | 10357211 | 7777777 |

| After Execution  | 67420566 | 7777777 |

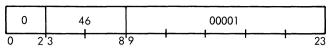

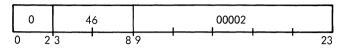

#### REGISTER CHANGE INSTRUCTIONS

The facility to operate on and exchange data between the A, B, and Index Registers is available within the set of microinstructions in the Register Change Group.

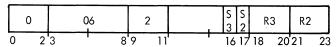

All instructions in the group use the same operation code, 46. Bit positions 14 through 23 of the address field specify the function to be performed by each micro-instruction. The programmer may specify combinations of address bits to perform simultaneous operations.

If the selected bits copy two registers into a third during one operation, a merge of the former two registers into the latter results.

If the selected control bits copy into a register and clear that same register, the clear has no effect.

The function of each address bit is:

| Instruction Bit | Octal Position | Octal Value | <u>Function</u>  |

|-----------------|----------------|-------------|------------------|

| 1               | 00             | 2           | Clear X          |

| 23              |                | 1           | Clear A          |

| 22              | 07             | 2           | Clear B          |

| 21              |                | 4           | Copy (A) into B  |

| 20              |                | 1           | Copy (B) into A  |

| 19              | O6             | 2           | Copy (B) into X  |

| 18              |                | 4           | Copy (X) into B  |

| 1 <i>7</i>      |                | 1           | Bits 15-23 only* |

| 16              | O5             | 2           | Copy (X) into A  |

| 15              |                | 4           | Copy (A) into X  |

| 14              | O4             | 1           | Copy -(A) into A |

<sup>\*</sup>See STORE EXPONENT (4600122) for special functions of this hit

#### **EXAMPLE:**

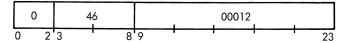

The following instruction copies (A) into B and clears the A Register:

0 46 00005

Both functions occur simultaneously, that is, within the one cycle time of the instruction.

Indirect addressing and indexing do not apply to these instructions.

These instructions require one machine cycle regardless of the number of functions performed. As an aid to the programmer, the most useful combinations have mnemonic designations assigned to them that are recognized by standard SDS programming systems.

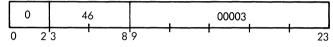

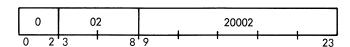

#### CLA CLEAR A

CLA clears the contents of the A Register to zero.

Registers Affected: A

Timing: 1

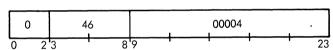

#### CLB CLEAR B

CLB clears the contents of the B Register to zero.

Registers Affected: B

Timing: 1

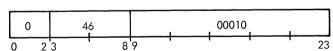

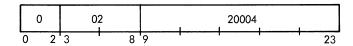

#### CLR CLEAR AB

CLR clears the contents of both the A and B Registers to zero.

Registers Affected: A, B

Timing: 1

#### CAB COPY A INTO B

CAB copies the contents of the A Register into the B Register.

Registers Affected: B

Timing: 1

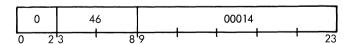

#### CBA COPY B INTO A

CBA copies contents of the B Register into the A Register.

Registers Affected: A

Timing: 1

#### XAB EXCHANGE A AND B

XAB copies the contents of the A Register into the B Register and, simultaneously, copies the contents of the B Register into the A Register.

Registers Affected: A, B

Timing: 1

BAC

COPY B INTO A, CLEAR B

BAC copies the contents of the B Register into the A Register and, simultaneously, clears the B Register to zero.

Registers Affected: A, B

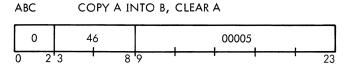

Timing: 1

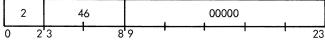

ABC copies the contents of the A Register into the B Register and, simultaneously, clears the A Register to zero.

Registers Affected: A, B

Timing: 1

CLX CLEAR INDEX REGISTER

The contents of the Index Register are set to zero.

Registers Affected: X

Timing: 1

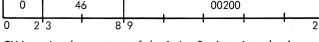

O 46 00200

CXA copies the contents of the Index Register into the A Register.

Registers Affected: A

Timing: 1

CAX COPY A INTO INDEX

CAX copies the contents of the A Register into the Index Register.

Registers Affected: X

Timing: 1

XXA EXCHANGE INDEX AND A

XXA copies the contents of the Index Register into the A Register and, simultaneously, copies the contents of the A Register into the Index Register.

Registers Affected: A, X

Timing: 1

CBX COPY B INTO INDEX

CBX copies the contents of the B Register into the Index Register.

Registers Affected: X

Timing: 1

CXB COPY INDEX INTO B

CXB copies the contents of the Index Register into the B Register.

Registers Affected: B

Timing: 1

XXB EXCHANGE INDEX AND B

XXB copies the contents of the Index Register into the B Register and, simultaneously, copies the contents of the B Register into the Index Register.

Registers Affected: B, X

Timing: 1

STE STORE EXPONENT

STE copies the least significant nine bits of the B Register into the Index Register, extends bit 15 of the Index Register (the sign of the exponent) into bit 0, and then clears the nine least significant bits of B.

EXAMPLE:

Before Execution

64152713

--

After Execution

64152000

77777713

Note: This instruction assists in the manipulation of floating-point, double-precision numbers, where the fraction is stored in the high order 39 bits and the exponent in the low order nine bits of the combined AB Register. (See Floating-Point Operations, this section.)

Registers Affected: B, X

Timing: 1

#### LDE LOAD EXPONENT

LDE copies the least significant nine bits of the Index Register into the least significant nine bits of the B Register and clears the nine least significant bits of B prior to the transfer.

#### **EXAMPLE:**

|                  | <u>B</u> | <u>Index</u> |

|------------------|----------|--------------|

| Before Execution | 34765712 | 00000151     |

| After Execution  | 34765151 | 00000151     |

Note:

This instruction assists in the manipulation of floating-point, double-precision numbers, where the fraction is stored in the most significant 39 bits and the exponent in the least significant nine bits.

Registers Affected: B

Timing: 1

#### XEE EXCHANGE EXPONENTS

XEE exchanges the least significant nine bits of the B Register and the Index Register. The exchange loses no information. The new bit 15 of the Index Register (the sign of the exponent) then extends into bit 0.

#### **EXAMPLE:**

|                  | <u>B</u> | <u>Index</u> |

|------------------|----------|--------------|

| Before Execution | 67142355 | 77777133     |

| After Execution  | 67142133 | 00000355     |

Note:

This instruction assists in the manipulation of floating-point, double-precision numbers, where the fraction is stored in the most significant 39 bits and the exponent in the least significant nine bits.

Registers Affected: B, X

Timing: 1

#### CNA COPY NEGATIVE INTO A

CNA copies the two's complement of the contents of the A Register into the A Register.

Registers Affected: A

Timing: 1

#### **BRANCH INSTRUCTIONS**

Branch instructions conditionally or unconditionally change the course of the program by altering the contents of the program counter. The programmer should note that these instructions branch to locations determined by the effective address; this means that the branch can operate with all levels of indirect and indexed addressing.

#### BRU BRANCH UNCONDITIONALLY

BRU takes the next instruction from the location determined by the effective address.

A BRU instruction with an Indirect Address bit equal to "one" clears the highest priority interrupt level then active in addition to branching to the effective location.

Registers Affected: P

Timing: 1

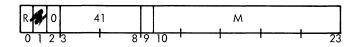

#### BRX INCREMENT INDEX & BRANCH

BRX increments the contents of the entire Index Register by one. If the resultant Index Register value contains a "1" in bit position 9 of the index, the computer transfers control to the effective location. If not, it takes the next instruction in sequence.

If a BRX instruction is indexed, any transfer of control is to the effective address determined by the value of the index immediately prior to the execution of BRX. The test for transfer is on the incremented value of the Index Register, just as if the BRX instruction were not indexed.

The most significant bits of the Index Register (bits 0-8) have no effect on the execution of the instruction, but may be affected by it.

If a branch occurs, an interrupt cannot occur following the execution of this instruction.

#### **EXAMPLE:**

| Location          | Instructi               | ion          | X Register |

|-------------------|-------------------------|--------------|------------|

| 0777              | STA 15                  | 500          | 77777776   |

| 1000              | BRX 10                  | 006          | 7777777    |

| 1001<br> <br>1006 | LDA 20<br> <br>  BRX 10 | 000<br> <br> | 00000000   |

| 1007              |                         | 100          | 0000000    |

The execution of these instructions is in the following order as given by their locations:

Registers Affected: X

Timing: 1, if branch

2, if no branch

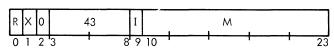

BRM MARK PLACE AND BRANCH

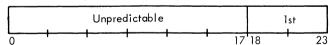

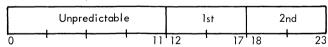

BRM stores the contents of the P Register (the address of the BRM instruction itself) in the effective memory location and transfers control to the effective memory location plus one. BRM also stores the status of the Overflow Indicator in bit 0 of the effective location and EM3 and EM2 in bits 3–5 and 6–8, respectively. The contents of bits 1–2 of the effective location are unpredictable. The content of bit 9 is zero. EXAMPLE:

| L | ocation  | Instruction | EM3                   | <u>EM2</u>       |               |

|---|----------|-------------|-----------------------|------------------|---------------|

| ( | 01517    | BRM 522     | 3                     | 2                |               |

|   |          |             | Overflow<br>Indicator | Location<br>0522 | P<br>Register |

|   | Before B | Execution   | 1 (on)                |                  | 01517         |

|   | After Ex | kecution    | l (on)                | 43201517         | 00523         |

Note: Use this instruction to enter subroutines where a return to the main program is desired after the subroutine has been completed. Use RETURN BRANCH (51) to return to the main program.

Registers Affected: M

Timing: 2

BRR RETURN BRANCH

BRR copies the contents of the effective memory location into an internal register and increments the contents by one. The instruction then stores the least significant 14 bits in the P Register. It also performs a logical OR between bit 0 and the Overflow Indicator; and places the result in the Overflow Indicator. There is no change in the contents of the effective memory location.

#### **EXAMPLE:**

| Location | Contents |

|----------|----------|

| 2100     | BRR 2000 |

| 2000     | 00003220 |

If the computer executes the instruction in location 2100, it takes the next instruction from location 3221. Location 2000 still contains 00003220.

Note: Use BRR to return to the main program after completion of a subroutine in conjunction with MARK PLACE AND BRANCH (43).

The Memory Extension registers are unaffected by BRR.

Registers Affected: Overflow Indicator Timing: 2

#### TEST AND SKIP INSTRUCTIONS

SKE SKIP IF A EQUALS MEMORY

SKE compares the contents of the A Register with the contents of the effective memory location. If the contents of A equal the contents of the effective location, the computer skips the next instruction in sequence and executes the following instruction. If the contents of A do not equal the contents of the effective location, the computer executes the next instruction in sequence. SKE alters neither A nor memory.

Registers Affected: None

Timing: 2, if no skip 3, if skip

SKG SKIP IF A GREATER THAN MEMORY

SKG algebraically compares the contents of the A Register with the contents of the effective memory location. If the contents of A are greater than the contents of the effective location, the computer skips the next instruction in sequence and executes the following instruction. If the contents of A are less than or equal to the contents of the effective location, the computer executes the next instruction in sequence. SKG alters neither A nor memory.

Registers Affected: None

Timing: 2, if no skip 3, if skip

SKM SKIP IF A EQUALS MEMORY ON B MASK

SKM compares selected bits of the contents of the A Register with the corresponding bits in the contents of the effective memory location. If the selected bits in A are identical to the selected bits in the contents of the effective memory location, the computer skips the next instruction in sequence and executes the following instruction. If the selected bits in the contents of the A Register are not identical to the contents of the effective location, the computer executes the next instruction in sequence.

The programmer selects the bits in A to be compared by placing ones in the corresponding bit positions of the B Register and zeros in the remaining bit positions of B.

SKM considers the contents of A,B, and the effective location to be unsigned, 24-bit, non-numeric quantities, and does not alter them.

#### **EXAMPLE:**

| <u>A</u> | <u>B</u> | Memory   |

|----------|----------|----------|

| 00043007 | 00177000 | 57643240 |

Since SKM compares bit positions 8-14 only (as determined by B), and (A) = (M) in these positions, a skip occurs. Note that if (B) = 0, a skip occurs regardless of (A) and (M). Note also that if (B) = 77777777, instruction SKM functions identically like instruction SKE.

Registers Affected: None

Timing: 2, if no skip

3, if skip

#### SKA SKIP IF A AND MEMORY DO NOT COMPARE ONES

SKA compares the contents of the A Register, bit by bit, with the contents of the effective memory location. If the contents of the A Register and the contents of the effective location do not have any one pair of ones in corresponding bit positions, the computer skips the next instruction in sequence and executes the following instruction. If the contents of the A Register and the contents of the effective location do have at least one pair of 1-bits in corresponding bit positions, the computer executes the next instruction in sequence.

The instruction logically ANDS corresponding bits in A and Memory, based on the following table:

| <u>A</u> | Memory | Result |

|----------|--------|--------|

| 0        | 0      | 0      |

| 0        | 1      | 0      |

| 1        | 0      | 0      |

| 1        | 1      | ı      |

If the result produces a "1" in any bit position, a skip does not occur.

Note: Different configurations of the memory word result in a wide variety of conditional instructions for use by the programmer. Some representative configurations are:

| Memory Configuration | Instruction           |  |  |

|----------------------|-----------------------|--|--|

| 4000000              | Skip if A is Positive |  |  |

| 7777777              | Skip if $A = 0$       |  |  |

| 0000001              | Skip if A is Even     |  |  |

#### Contents of A Register

| 40000000 | Skip if Memory is Positive |

|----------|----------------------------|

| 77777777 | Skip if Memory = 0         |

| 00000001 | Skip if Memory is Even     |

Registers Affected: None

Timing: 2, if no skip 3, if skip

#### SKB SKIP IF B AND MEMORY DO NOT COMPARE ONES

This instruction functions identically like SKA but operates on the B Register.

Registers Affected: None

Timing: 2, if no skip 3, if skip

SKN SKIP IF MEMORY NEGATIVE

If the contents of the effective memory location are negative, i.e., if  $(M_0) = 1$ , the computer skips the next instruction in sequence and executes the following instruction. If the contents of the effective location are positive or zero, the computer executes the next instruction in sequence.

Registers Affected: None

Timing: 2, if no skip

3, if skip

Timing: 3

SKR REDUCE MEMORY, SKIP IF NEGATIVE

SKR reduces the contents of the effective memory location by one, places the result in the same location, and then tests for negative. If the contents of the effective memory location are then negative, the computer skips the next instruction in sequence and executes the following instruction. If the contents of the effective location are positive or zero, the computer executes the next instruction in sequence.

An overflow occurs if the initial contents of memory are 4000000. The result in memory in this case is 37777777.

Registers Affected: M, Overflow Indicator

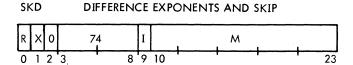

SKD subtracts the contents of bits 15 through 23 of the effective memory location from bits 15 through 23 of the B Register. It then stores the absolute magnitude of the difference in bits 15 through 23 of the X Register and destroys the contents of bits 0 through 14 of the X Register. If the 9-bit contents of the effective location are less than or equal to the 9-bit contents of the B Register, the computer executes the next instruction in sequence. If not, the computer skips the next instruction in sequence and executes the following instruction.

Registers Affected: X

Timing: 2, if no skip

3, if skip

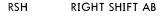

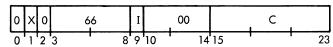

#### SHIFT INSTRUCTIONS

The shift instructions operate on the contents of the A and B Registers and offer a complete facility for right and left shifting, cycling, and normalizing the contents of these two registers. The A and B Registers, in combination, form a double-length register whose double-length contents can be shifted, cycled, or normalized. This double-length register is named "AB."

When the contents of the AB Register shift right, bits from bit position 23 of the A Register shift into bit position 0 of the B Register. When the AB Register shifts left, bits from bit position 0 of the B Register shift into bit position 23 of the A Register.

The 48-bit contents of the AB Register may be cycled using the shift instructions. When the contents of the AB Register cycle, the bits that shift from one end of the one register copy into the other end of the other register.

These instructions use the instruction code to determine the direction of shift (66 = right; 67 = left); bits 10-11 (octal position 3) of the instruction address determine the method of shifting as follows:

| Bits 10, 11 | <u>Octal Value</u> | <u>Function</u>       |

|-------------|--------------------|-----------------------|

| 00          | 0                  | AB Shift              |

| 10          | 2                  | AB Cycle              |

| 01          | 1                  | Normalize (Left only) |

Indirect addressing is permissible with these instructions, bits 10 and 11 of the effective address determining the method of shifting.

Since the type of shift and number of shifts are determined by bits 10 through 23 of the effective address, indirect addressing and/or indexing drastically alter the action specified in a shift instruction. When procuring the effective location for a shift instruction,

14-bit indexing is performed with all indirectly addressed operands, and

9-bit indexing is performed with all directly addressed operands.

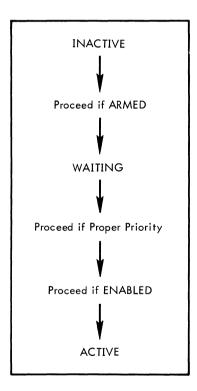

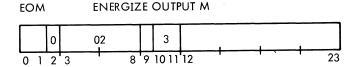

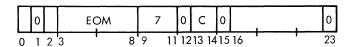

That is, indexing with a direct address can affect only the 9-bit shift count.