# **KA670 CPU Module Technical Manual**

Order Number EK-KA670-TM-001

digital equipment corporation maynard, massachusetts

#### First Edition, April 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1990

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| DEC       | MicroVAX     | RV20           |

|-----------|--------------|----------------|

| DECmate   | PDP          | ThinWire       |

| DECnet    | P/OS         | TQK50          |

| DECUS     | Professional | ULTRIX         |

| DECwriter | Q-bus        | UNIBUS         |

| DEQNA     | Q22-bus      | VAX            |

| DIBOL     | Rainbow      | VAXstation     |

| DSSI      | RRD50        | VMS            |

| LPV11-SA  | RSTS         | VT             |

| MASSBUS   | RSX          | Work Processor |

| MicroPDP  | RT           |                |

|           |              | digital        |

|           |              |                |

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

# **Contents**

| Abo | out Th                                  | nis Manual                                    | xxi                   |

|-----|-----------------------------------------|-----------------------------------------------|-----------------------|

| Ove | erviev                                  | w and Installation                            |                       |

| 1   | Over                                    | view                                          |                       |

|     | 1.1<br>1.1.1                            | KA670 CPU Module Module Components            | 3<br>4                |

|     | 1.2<br>1.2.1<br>1.2.2<br>1.2.3          | Central Processing Subsystem                  | 6<br>6<br>7<br>7      |

|     | 1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4 | System Support Subsystem                      | 7<br>7<br>8<br>8<br>8 |

|     | 1.4<br>1.4.1<br>1.4.2<br>1.4.3          | I/O Subsystem                                 | 8<br>8<br>9<br>9      |

|     | 1.5<br>1.5.1                            | Memory Support Subsystem                      | 9<br>9                |

|     | 1.6<br>1.7                              | MS670 Memory Module                           | 10<br>11              |

| 2   | Insta                                   | allation and Configuration                    |                       |

|     | 2.1                                     | Installing the KA670 and MS670 Memory Modules | 13                    |

|     | 2.2                                     | Module Configuration and Naming               | 14                    |

|     | 2.3<br>2.3.1<br>2.3.2                   | Mass Storage Configuration                    | 15<br>15<br>16        |

|    | 2.3.3<br>2.3.3.1 | Accessing RF-series Firmware in VMS, Through DUP      | 17<br>18 |

|----|------------------|-------------------------------------------------------|----------|

|    | 2.4 I            | OSSI Cabling, Device Identity, and Bus Termination    | 18       |

|    | 2.5 H            | KA670 Connectors                                      | 18       |

| Αt | chitect          | ure                                                   |          |

| 3  | Centr            | al Processor and Floating Point Unit                  |          |

|    | 3.1              | Central Processor                                     | 21       |

|    | 3.1.1            | Processor State                                       | 21       |

|    | 3.1.1.1          | General-Purpose Registers                             | 21       |

|    | 3.1.1.2          | Processor Status Longword                             | 22       |

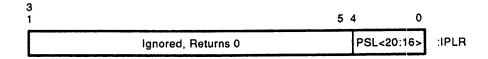

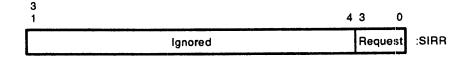

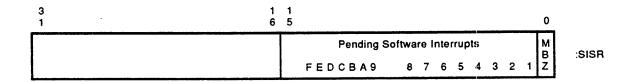

|    | 3.1.1.3          | Internal Processor Registers                          | 23       |

|    | 3.1.2            | Process Structure                                     | 29       |

|    | 3.1.3            | Data Types                                            | 30       |

|    | 3.1.4            | Instruction Set                                       | 30       |

|    | 3.1.5            | Memory Management                                     | 31       |

|    | 3.1.5.1          | Translation Buffer                                    | 31       |

|    | 3.1.5.2          | Memory Management Control Registers                   | 32       |

|    | 3.1.6            | Interrupts and Exceptions                             | 33       |

|    | 3.1.6.1          | Interrupts                                            | 34       |

|    | 3.1.6.2          | Exceptions                                            | 36       |

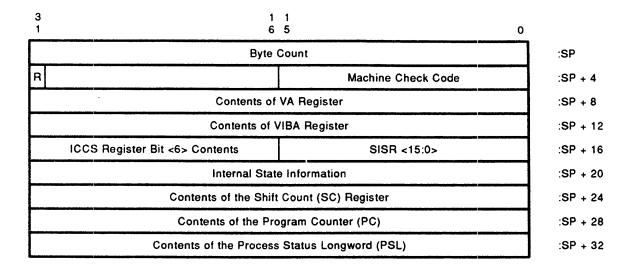

|    | 3.1.6.3          | Information Saved on a Machine Check Exception        | 38       |

|    | 3.1.6.4          | Machine Check Error Register (MCESR) IPR 38           | 43       |

|    | 3.1.6.5          | System Control Block (SCB)                            | 43       |

|    | 3.1.6.6          | The Hardware Halt Procedure                           | 46       |

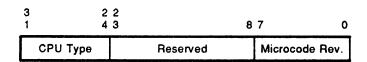

|    | 3.1.7            | System Identification                                 | 48       |

|    | 3.1.7.1          | System Identification Register                        | 48       |

|    | 3.1.7.2          | System Identification Extension Register (20040004)   | 49       |

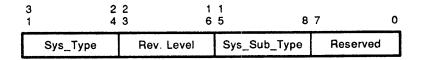

|    | 3.1.8            | Accelerator Control and Status Register (ACCS) IPR 40 | 49       |

|    | 3.1.9            | CPU References                                        | 50       |

|    | 3.1.9.1          | Instruction-Stream Read References                    | 51       |

|    | 3.1.9.2          | Data-Stream Read References                           | 51       |

|    | 3.1.9.3          | Write References                                      | 51       |

|    | 3.2              | KA670 Floating Point Accelerator                      | 52       |

|    | 3.2.1            | Floating Point Accelerator Data Types                 | 52       |

|    | 3.2.2            | Floating Point Accelerator Instructions               | 52       |

|    | 3.2.3            | Operand and Result Transfer                           | 52       |

|    | 3.2.4            | Power-Up State                                        | 53       |

|    |                  |                                                       |          |

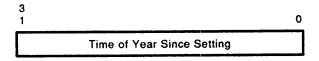

|   | 5.2.1   | Time-of-Year Clock (TODR)—EPR 27                   | 115 |

|---|---------|----------------------------------------------------|-----|

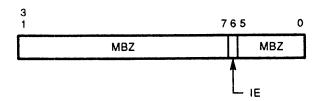

|   | 5.2.2   | Interval Timer (ICCS)—EPR 24                       | 116 |

|   | 5.2.3   | Programmable Timers                                | 116 |

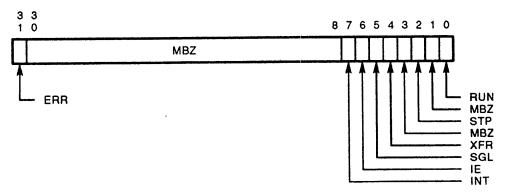

|   | 5.2.3.1 | Timer Control Registers (TCR0 and TCR1)            | 117 |

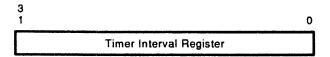

|   | 5.2.3.2 | Timer Interval Registers (TIR0 and TIR1)           | 118 |

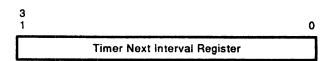

|   | 5.2.3.3 | Timer Next Interval Registers (TNIR0 and TNIR1)    | 118 |

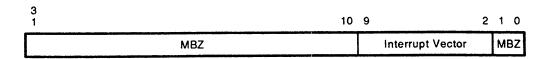

|   | 5.2.3.4 | Timer Interrupt Vector Registers (TIVR0 and TIVR1) | 118 |

|   | 5.3 K   | XA670 Bus Overview                                 | 119 |

|   | 5.3.1   | RDAL Bus                                           | 119 |

|   | 5.3.2   | The CP Bus                                         | 120 |

|   | 5.3.2.1 | The CCLOCK Chip                                    | 120 |

|   | 5.3.2.2 | CP Bus Arbiter                                     | 120 |

|   | 5.3.3   | GMI Bus                                            | 120 |

| _ |         |                                                    |     |

| 6 | KA670   | 0 Boot and Diagnostic Facility                     |     |

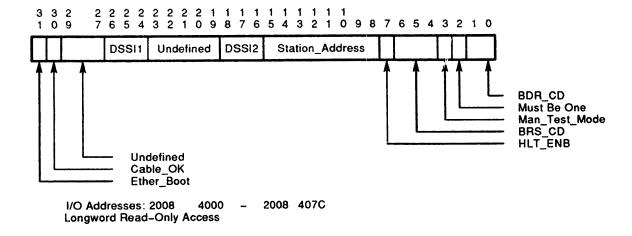

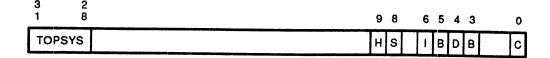

|   | 6.1 B   | oot and Diagnostic Register (BDR)                  | 121 |

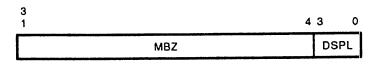

|   | 6.2 D   | Piagnostic LED Register (DLEDR)                    | 123 |

|   | 6.3 E   | PROM Memory                                        | 124 |

|   | 6.3.1   | EPROM Address Space                                | 124 |

|   | 6.3.2   | KA670 Resident Firmware Operation                  | 125 |

|   | 6.3.2.1 | Power-Up Modes                                     | 125 |

|   | 6.4 B   | attery Backed-Up RAM                               | 125 |

|   | 6.5 K   | A670 Initialization                                | 126 |

|   | 6.5.1   | Power-Up Initialization                            | 126 |

|   | 6.5.2   | Hardware Reset                                     | 126 |

|   | 6.5.3   | I/O Bus Initialization                             | 126 |

|   | 6.5.3.1 | I/O Bus Reset Register (IPR 55)                    | 126 |

|   | 6.5.4   | Processor Initialization                           | 126 |

|   | 6.5.4.1 | Configuring the Local I/O Page                     | 127 |

|   | 6.5.5   | SSC Base Address Register (SSCBR)                  | 127 |

|   | 6.5.6   | BDR Address Decode Match Register (BDMTR)          | 127 |

|   | 6.5.7   | BDR Address Decode Mask Register (BDMKR)           | 128 |

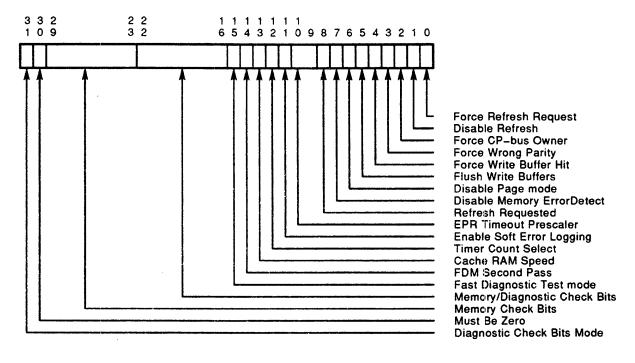

|   | 6.5.8   | SSC Configuration Register (SSCCR)                 | 128 |

|   | 6.6 Cl  | P Bus Timeout Control Register (CBTCR)             | 130 |

|   |         |                                                    |     |

| 7 | Interfa | ice Subsystems                                     |     |

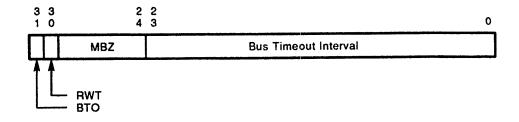

|   | 7.1 K   | A670 Q22-bus Interface                             | 132 |

|   | 7.1.1   | Q22-bus to Main Memory Address Translation         | 133 |

|   | 7.1.1.1 | Q22-bus Map Registers (QMR)                        | 134 |

|   | 7.1.1.2 | Accessing the Q22-bus Map Registers                | 135 |

|   | 7.1.1.3 | The Q22-bus Map Cache                              | 136 |

|   | 7.1.2   | CP to Q22-bus Address Translation                  | 137 |

| 7.1.3    | Interprocessor Communications Facility           | 137 |

|----------|--------------------------------------------------|-----|

| 7.1.3.1  | Interprocessor Communication Register (IPCR)     | 138 |

| 7.1.3.2  | Interprocessor Doorbell Interrupts               | 139 |

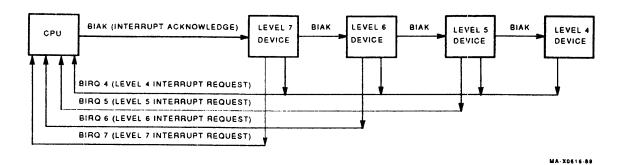

| 7.1.4    | Q22-bus Interrupt Handling                       | 139 |

| 7.1.5    | Configuring the Q22-bus Map                      | 139 |

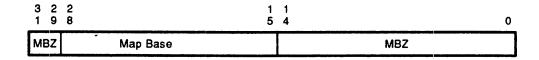

| 7.1.5.1  | Q22-bus Map Base Address Register (QBMBR)        | 140 |

| 7.1.6    | System Configuration Register (SCR)              | 140 |

| 7.1.7    | Error-Reporting Registers                        | 141 |

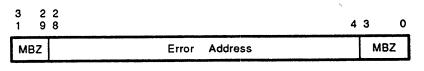

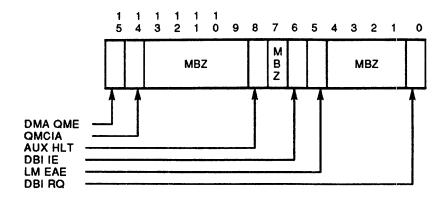

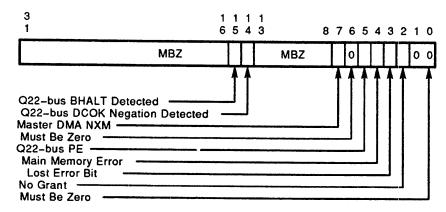

| 7.1.7.1  | DMA System Error Register (DSER)                 | 142 |

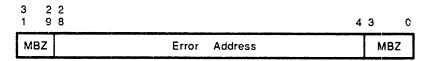

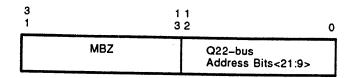

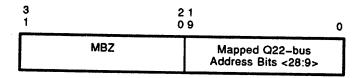

| 7.1.7.2  | Q22-bus Error Address Register (QBEAR)           | 143 |

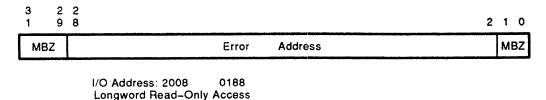

| 7.1.7.3  | DMA Error Address Register (DBEAR)               | 144 |

| 7.1.8    | Error Handling                                   | 145 |

| 7.2 H    | KA670 Network Interface                          | 146 |

| 7.2.1    | Ethernet Overview                                | 146 |

| 7.2.2    | NI Station Address ROM (NISA ROM)                | 147 |

| 7.3 P    | rogramming the Ethernet Controller Chip (SGEC)   | 148 |

| 7.3.1    | Programming Overview                             | 148 |

| 7.3.2    | Command and Status Registers                     | 149 |

| 7.3.3    | Host Access to NICSRs                            | 149 |

| 7.3.3.1  | Physical NICSRs                                  | 149 |

| 7.3.3.2  | Virtual NICSRs                                   | 149 |

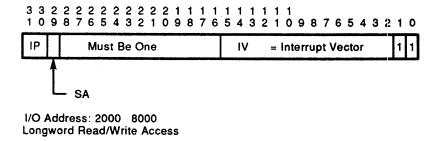

| 7.3.4    | Vector Address, IPL, Sync/Asynch (NICSR0)        | 150 |

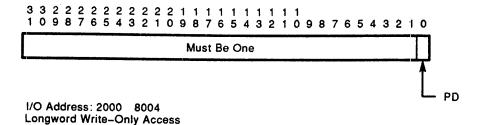

| 7.3.5    | Transmit Polling Demand (NICSR1)                 | 151 |

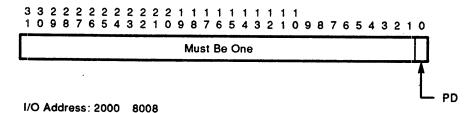

| 7.3.6    | Receive Polling Demand (NICSR2)                  | 152 |

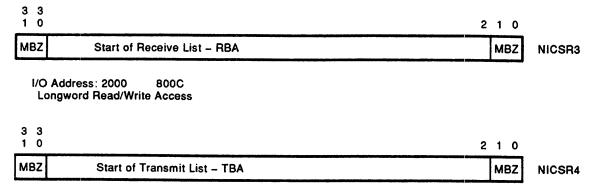

| 7.3.7    | Descriptor List Addresses (NICSR3, NICSR4)       | 153 |

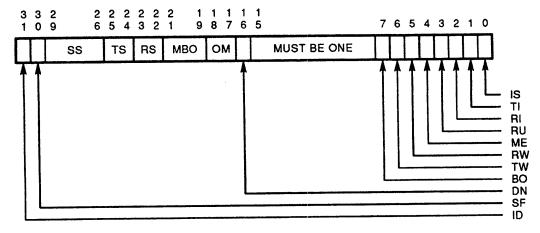

| 7.3.8    | Status Register (NICSR5)                         | 155 |

| 7.3.8.1  | NICSR5 Status Report                             | 159 |

| 7.3.9    | Command and Mode Register (NICSR6)               | 160 |

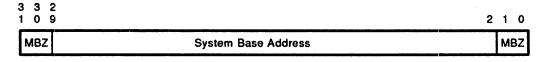

| 7.3.10   | System Base Register (NICSR7)                    | 166 |

| 7.3.11   | Reserved Register (NICSR8)                       | 167 |

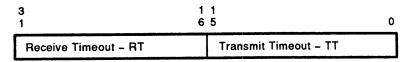

| 7.3.12   | Watchdog Timers (NICSR9)                         | 167 |

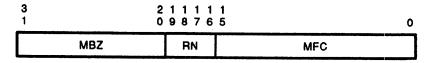

| 7.3.13   | Revision Number and Missed-Frame Count (NICSR10) | 168 |

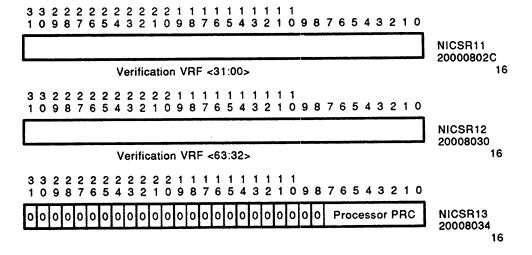

| 7.3.14   | Boot Message (NICSR11, 12, 13)                   | 169 |

| 7.3.15   | Diagnostic Registers (NICSR14,15)                | 170 |

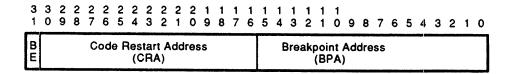

| 7.3.15.1 | -                                                | 170 |

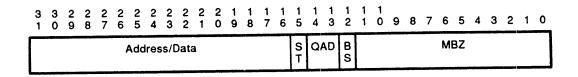

| 7.3.15.2 |                                                  | 171 |

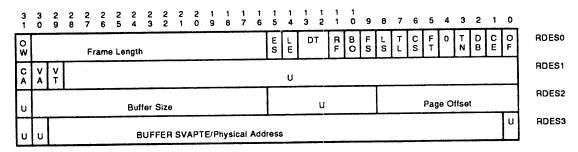

| 7.3.16   | Descriptors and Buffers—Format                   | 172 |

| 7.3.17   | Receive Descriptors                              | 173 |

| 7.3.17.1 |                                                  | 173 |

| 7.3.17.2 |                                                  | 178 |

| 7.3.17.3 |                                                  | 176 |

| 7.3.17.4 |                                                  | 177 |

| 7217     | Receive Descriptor Status Validity               | 17' |

|   | 7.3.18 Transmit Descriptors                                | 178        |

|---|------------------------------------------------------------|------------|

|   | 7.3.18.1 TDES0 Word                                        | 178        |

|   | 7.3.18.2 TDES1 Word                                        | 180        |

|   | 7.3.18.3 TDES2 Word                                        | 181        |

|   | 7.3.18.4 TDES3 word                                        | 182        |

|   | 7.3.18.5 Transmit Descriptor Status Validity               | 182        |

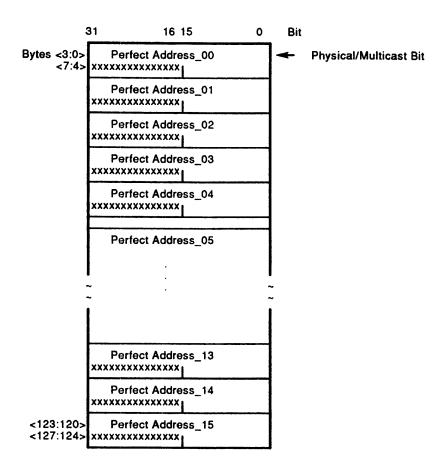

|   | 7.3.19 Setup Frame                                         | 183        |

|   | 7.3.19.1 First Setup Frame                                 | 183        |

|   | 7.3.19.2 Subsequent Setup Frame                            | 183        |

|   | 7.3.19.3 Setup Frame Descriptor                            | 184        |

|   | 7.3.19.4 Perfect Filtering Setup Frame Buffer              | 185        |

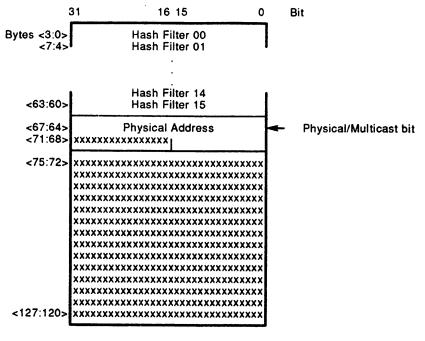

|   | 7.3.19.5 Imperfect Filtering Setup Frame Buffer            | 187        |

|   | 7.3.20 Hardware and Software Reset                         | 191        |

|   | 7.3.21 Interrupts                                          | 192        |

|   | 7.3.22 Startup Procedure                                   | 192        |

|   | 7.3.23 Reception Process                                   | 193        |

|   | 7.3.24 Transmission Process                                | 194        |

|   | 7.3.25 Loopback Operations                                 | 196        |

|   | 7.3.26 Support for DNA CSMA/CD Counters and Events         | 197        |

|   |                                                            |            |

|   | ======================================                     | 198        |

|   | 55-15 5 TOTAL                                              | 199        |

|   |                                                            | 201        |

|   | 1100.000.000.000.000.000.000.000.000.00                    | 203        |

|   |                                                            | 203        |

|   | 7.4.3.2 SHAC-Specific Registers                            | 211        |

| 8 | KA670 Error Hondling                                       |            |

| U | KA670 Error Handling                                       |            |

|   | 8.1 Error Handling—SCB Entry Points                        | 214        |

|   | 8.1.1 Error Categories for SCB Entry Points                | 215        |

|   | 8.1.2 Macrocode Error Handling and Recovery                | 216        |

|   | 8.1.2.1 Error State Collection                             | 217        |

|   | 8.1.2.2 Error Analysis                                     | 217        |

|   | 8.1.2.3 Error Recovery                                     | 218        |

|   | 8.1.2.4 Special Considerations for Cache and Memory Errors | 218        |

|   | 8.1.2.5 Error Retry                                        | 220        |

|   | 8.2 Console Halt and Halt Interrupt                        | 220        |

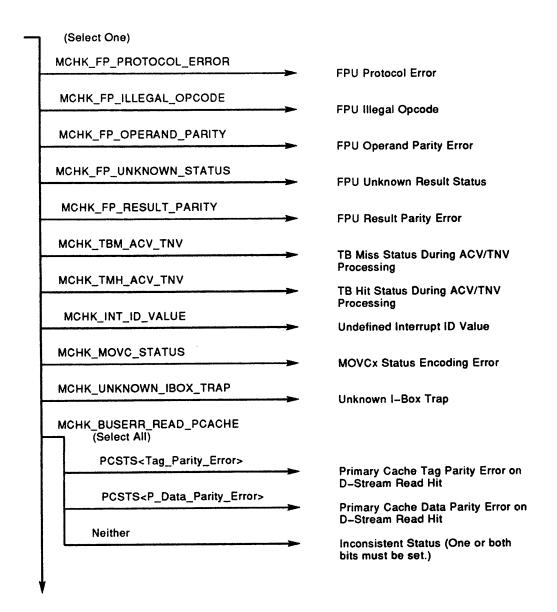

|   | 8.3 Machine Check Exception                                | 221        |

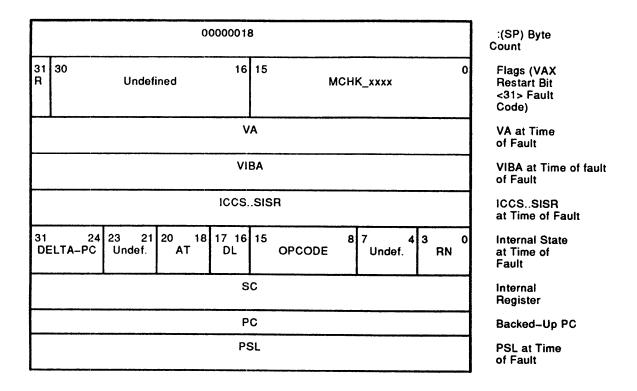

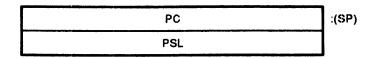

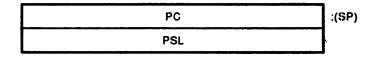

|   | 8.3.1 Machine Check Stack Frame                            | 221        |

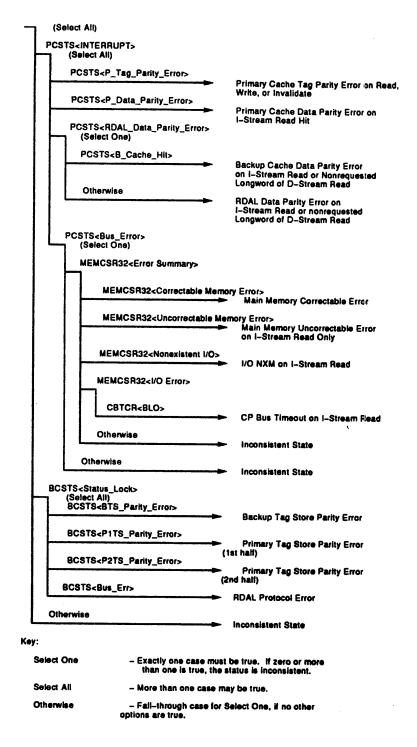

|   | 8.3.2 Machine Check Parse Tree                             |            |

|   | 8.3.3 MCHK_FP_PROTOCOL_ERROR                               | 224        |

|   | 8.3.4 MCHK_FP_ILLEGAL_OPCODE                               | 227        |

|   | 8.3.5 MCHK_FP_OPERAND_PARITY                               | 228        |

|   | 8.3.6 MCHK_FP_UNKNOWN_STATUS                               | 228        |

|   | 8.3.7 MCHK_FP_RESULT_PARITY.                               | 229        |

|   | 8.3.8 MCHK_TBM_ACV_TNV                                     | 229<br>229 |

|   | *** = **==****************************                     | 7.74       |

| 8.3.9 MCHK_TBH_ACV_TNV                                         | 229         |

|----------------------------------------------------------------|-------------|

| 8.3.10 MCHK_INT_ID_VALUE                                       | 230         |

| 8.3.11 MCHK_MOVC_STATUS                                        | 230         |

| 8.3.12 MCHK_UNKNOWN_IBOX_TRAP                                  | 230         |

| 8.3.13 MCHK_BUSERR_READ_PCACHE                                 | 230         |

| 8.3.13.1 Primary Cache Tag Parity Error on D-Stream Read Hit   | 231         |

| 8.3.13.2 Primary Cache Data Parity Error on D-Stream Read Hit  | 231         |

| 8.3.14 MCHK_BUSERR_READ_DAL                                    | 231         |

| 8.3.14.1 Data Parity Error on D-Stream Read                    | 231         |

| 8.3.14.2 Bus Error on D-Stream Read                            | 232         |

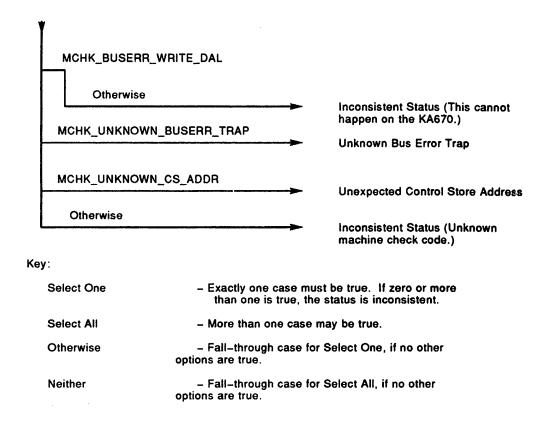

| 8.3.15 MCHK_BUSERR_WRITE_DAL                                   | 233         |

| 8.3.16 MCHK_UNKNOWN_BUSERR_TRAP                                | 233         |

| 8.3.17 MCHK_UNKNOWN_CS_ADDR                                    | <b>23</b> 3 |

| 8.4 Power-Fail Interrupt                                       | 234         |

| 8.5 Hard Error Interrupts                                      | 234         |

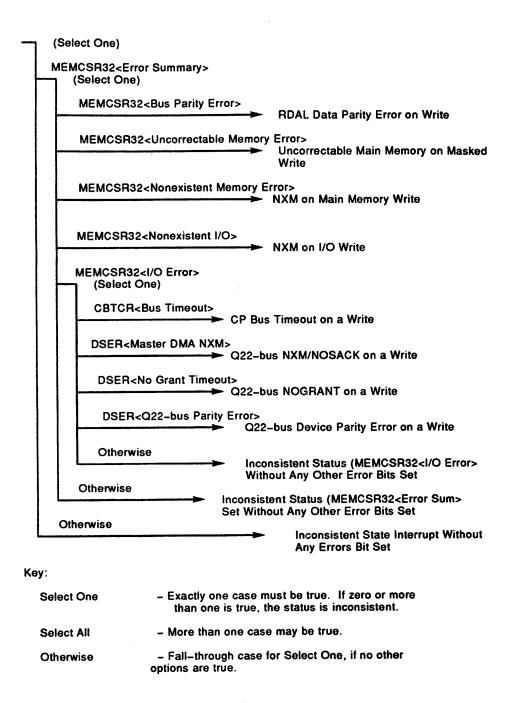

| 8.5.1 Parse Tree for a Hard Error Intercupt                    | 234         |

| 8.5.2 RDAL Data Parity Error on Memory Write                   | 236         |

| 8.5.3 Uncorrectable Main Memory Error on Masked Write          | 236         |

| 8.5.4 Main Memory Nonexistent Write                            | 236         |

| 8.5.5 I/O Nonexistent Write                                    | 236         |

| 8.5.6 CP Bus Timeout on a Write                                | 236         |

| 8.5.7 Q22-bus NXM/NOSACK on a Write                            | 237         |

| 8.5.8 Q22-bus NOGRANT on a Write                               | 237         |

| 8.5.9 Q22-bus Device Parity Error on a Write                   | 237         |

| 8.6 Soft Error Interrupts                                      | 237         |

| 8.6.1 Parse Tree for Soft Error Interrupts                     | 237         |

| 8.6.2 Cache or Memory Errors                                   | 239         |

| 8.6.2.1 Primary Cache Errors                                   | 239         |

| 8.6.2.2 RDAL Data Parity Errors                                | 239         |

| 8.6.2.3 Bus Error on I-Stream Read                             | 240         |

| 8.6.3 Cache Fill Errors on the Nonrequested Quadword of a Read | 240         |

| 8.6.4 C-Chip Errors                                            | 240         |

| 8.6.4.1 C-Chip Backup Tag Store Parity Error                   | 241         |

| 8.6.4.2 C-Chip Primary Tag Store Parity Error                  | 241         |

| 8.6.4.3 C-Chip Bus Protocol Error                              | 241         |

| 8.7 Kernel Stack Not Valid Exception                           | 241         |

| 8.8 Errors Without Notification                                | 242         |

| 8.8.1 Parity Generation and Detection Philosophy               | 242         |

| 8.8.2 Microcode-Detected Error Summary                         | 242         |

| 8.8.3 Errors Detected by Self-Tests                            | 243         |

# **Firmware**

| 9 | Firmwa | re |

|---|--------|----|

|---|--------|----|

| 9.1 Firmware Capabilities                     | 248        |

|-----------------------------------------------|------------|

| 9.2 Firmware Overview                         | 248        |

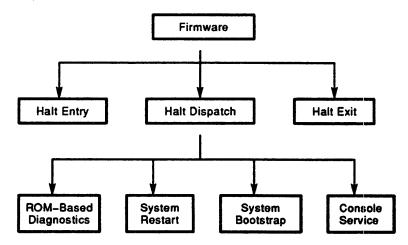

| 9.3 Halt Entry, Exit, and Dispatch            | 249        |

| 9.3.1 Halt Entry—Saving Processor State       | 249        |

| 9.3.2 Halt Dispatch                           | 250        |

| 9.3.2.1 External Halts                        | 251        |

| 9.3.3 Halt Exit—Restoring the Processor State | 252        |

| 9.4 Power-Up                                  | 252        |

| 9.4.1 Identifying the Console Device          | 252        |

| 9.4.1.1 Mode Switch Set to Test               | 253        |

| 9.4.1.2 Mode Switch Set to Query              | 253        |

| 9.4.1.3 Mode Switch Set to Normal             | 254        |

| 9.4.2 LED Codes                               | 255        |

| 9.5 Operating System Bootstrap                | 256        |

| 9.5.1 Preparing for the Bootstrap             | 256        |

| 9.5.1.1 Boot Devices                          | 258        |

| 9.5.1.2 Boot Flags                            | 260        |

| 9.5.2 Primary Bootstrap, Virtual Memory Boot  | 260        |

| 9.5.3 Device-Dependent Bootstrap Procedures   | 263        |

| 9.5.3.1 Disk and Tape Bootstrap Procedure     | 263        |

| 9.5.3.2 PROM Bootstrap Procedure              | 264        |

| 20000 ap 1 occurre                            | 264        |

| 9.6 Operating System Restart                  | 265        |

| 9.6.1 Locating the Restart Parameter Block    | 266        |

| 9.7 Console Service                           | 266        |

| 9.7.1 Console Control Characters              | 267        |

| 9.7.2 Console Command Syntax                  | 268        |

| 9.7.3 Console Command Keywords                | <b>268</b> |

| 9.7.4 Console Command Qualifiers              | 270        |

| o mana radicos opecineis                      | 270        |

| registers and memory                          | 274        |

| 9.8 Console Commands                          | 274        |

| BOOT                                          | 275        |

| CONTINUE                                      | 277        |

|                                               | 279        |

|                                               | 280        |

| FIND                                          | 282        |

| $\mathbf{H}\mathbf{A}\mathbf{I}\mathbf{T}$    | 285        |

| uri d                                         | 286        |

|                                               |            |

|   | INITIALIZE                                        | 289         |

|---|---------------------------------------------------|-------------|

|   | MOVE                                              | 291         |

|   | NEXT                                              | 293         |

|   | REPEAT                                            | 295         |

|   | SEARCH                                            | 296         |

|   | SET                                               | 299         |

|   | SHOW                                              | 303         |

|   | START                                             | 307<br>308  |

|   | TEST                                              | 311         |

|   | UNJAM                                             | 312         |

|   | X                                                 | 314         |

|   | 1                                                 | 315         |

|   | 9.8.1 Command Summary                             | 318         |

|   | 9.9 Diagnostics                                   | 319         |

|   | 9.9.1 Error Reporting                             | 320         |

|   | 9.9.2 Diagnostic Interdependencies                | 520         |

|   |                                                   |             |

| Α | Q22-bus Specification                             |             |

|   | A.1 Introduction                                  | 321         |

|   | A.1.1 Master/Slave Relationship                   | 322         |

|   | A.2 Q22-bus Signal Assignments                    | 322         |

|   | A.3 Data Transfer Bus Cycles                      | <b>32</b> 5 |

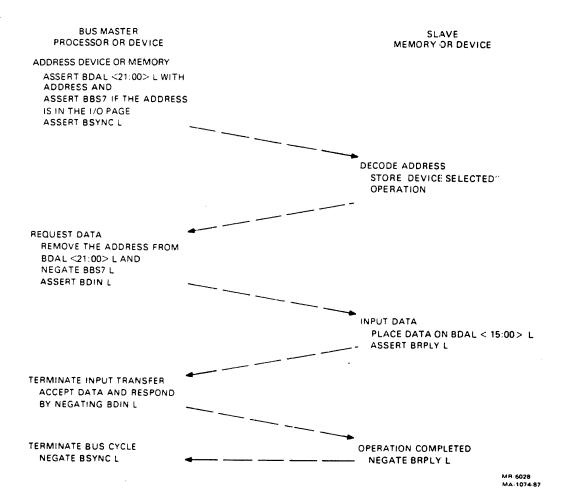

|   | A.3.1 Bus Cycle Protocol                          | 326         |

|   | A.3.2 Device Addressing                           | 327         |

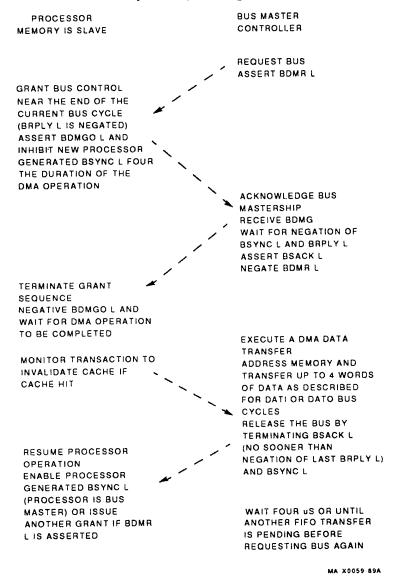

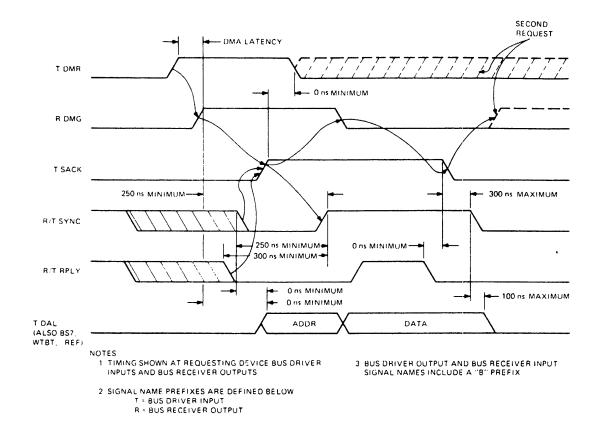

|   | A.4 Direct Memory Access                          | 334         |

|   | A.4.1 DMA Protocol                                | 334         |

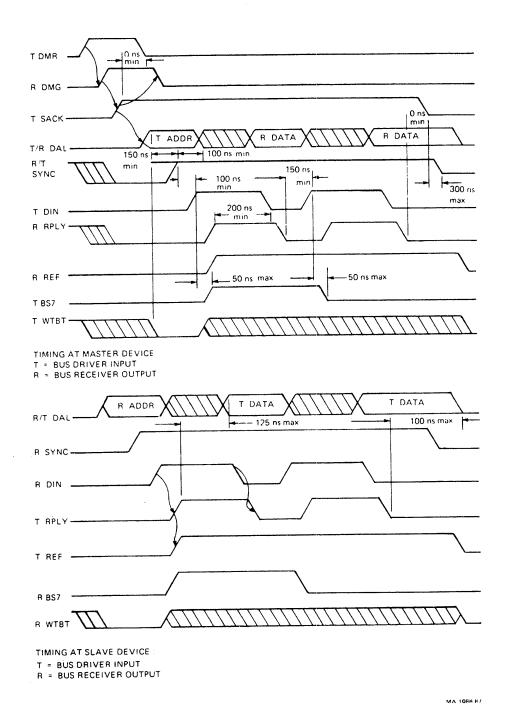

|   | A.4.2 Block Mode DMA                              | 336         |

|   | A.4.2.1 DATBI Bus Cycle                           | 338         |

|   | A.4.2.2 DATBO Bus Cycle                           | 340<br>341  |

|   | A.4.3 DMA Guidelines                              | _           |

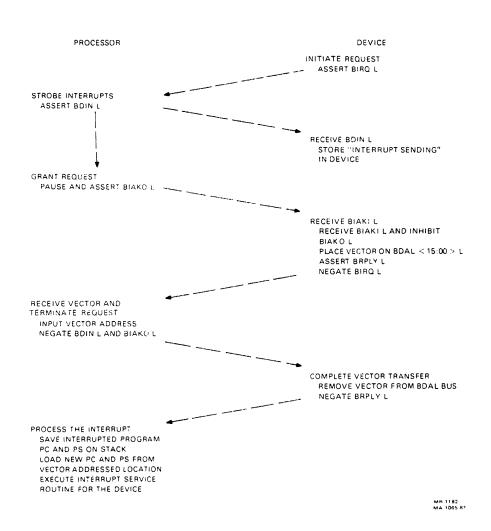

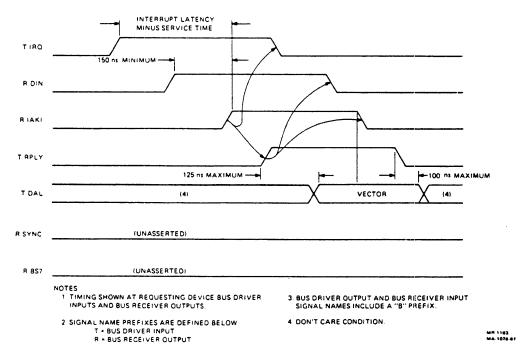

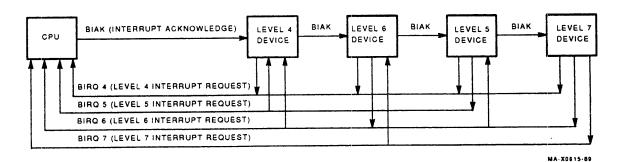

|   | A.5 Interrupts                                    | 341         |

|   | A.5.1 Device Priority                             | 342<br>342  |

|   | A.5.2 Interrupt Protocol                          | 342<br>345  |

|   | A.5.3 Q22-bus Four-Level Interrupt Configurations |             |

|   | A.6 Control Functions                             | 346         |

|   | A.6.1 Halt                                        | 346<br>346  |

|   | A.6.2 Initialization                              | 346         |

|   | A.6.3 Power Status                                |             |

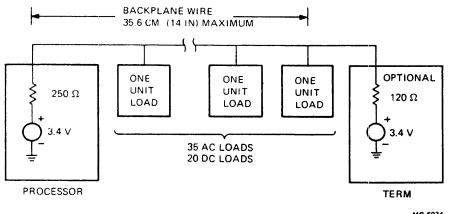

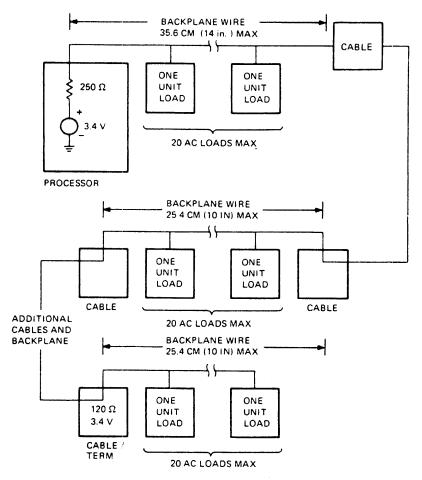

|   | A.7 Q22-bus Electrical Characteristics            | 346         |

|   | A.7.1 Signal Level Specifications                 | 347<br>347  |

|   | A.7.2 Load Definition                             |             |

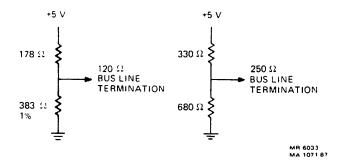

|   | A.7.3 120-Ohm Q22-bus                             |             |

|   | A.7.4 Bus Drivers                                 |             |

|   | A.7.5 Bus Receivers                               | 3 10        |

|   | A.7.6 Bus Termination  A.7.7 Bus Interconnecting Wiring  A.7.7.1 Backplane Wiring  A.7.7.2 Intrabackplane Bus Wiring  A.7.7.3 Power and Ground | 348<br>349<br>349<br>349<br>349 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   | A.8 System Configurations                                                                                                                      | 350<br>353                      |

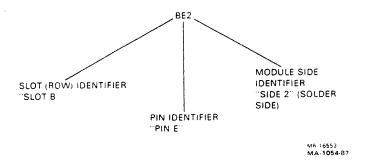

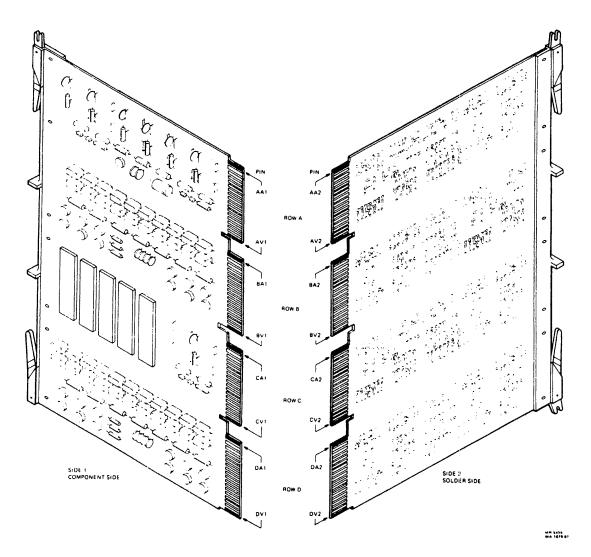

|   | A.9 Module Contact Finger Identification                                                                                                       | 353                             |

| В | Specifications                                                                                                                                 |                                 |

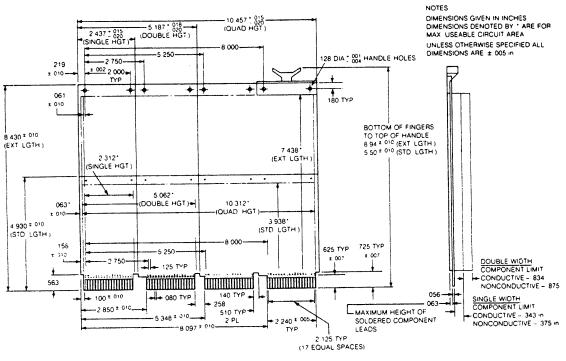

|   | B.1 Dimensions                                                                                                                                 | 361<br>361                      |

|   | B.2 DC Power Consumption                                                                                                                       | 364                             |

|   | B.3 Bus Loads                                                                                                                                  | 365                             |

|   | B.4 Battery Backup Specifications                                                                                                              | 365                             |

|   | B.5 Operating Conditions                                                                                                                       | 365                             |

|   | B.6 Nonoperating Conditions (Less Than 60 Days)                                                                                                | 365                             |

|   | B.7 Nonoperating Conditions (Greater than 60 Days)                                                                                             | 366                             |

| С | Address Assignments                                                                                                                            |                                 |

|   | C.1 KA670 General Local Address Space Map                                                                                                      | 367                             |

|   | C.2 KA670 Detailed Local Address Space Map                                                                                                     | 368                             |

|   | C.3 External, Internal Processor Registers                                                                                                     | 371                             |

|   | C.4 Global Q22-bus Address Space Map                                                                                                           | 372                             |

| D | VAX Instruction Set                                                                                                                            |                                 |

|   | D.1 Syntax                                                                                                                                     | 373                             |

| E | Machine State on Power-Up                                                                                                                      |                                 |

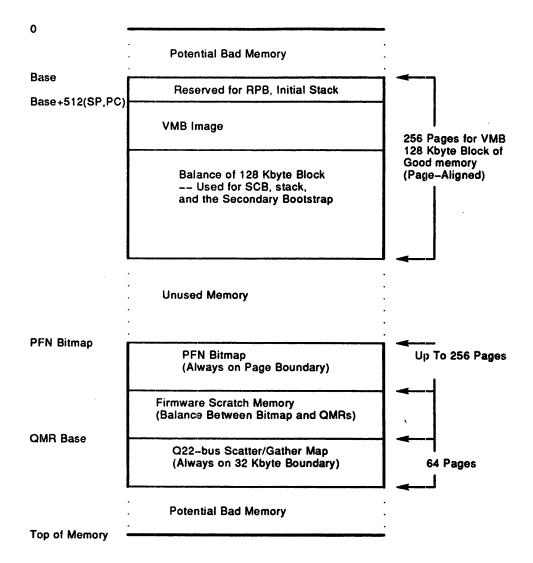

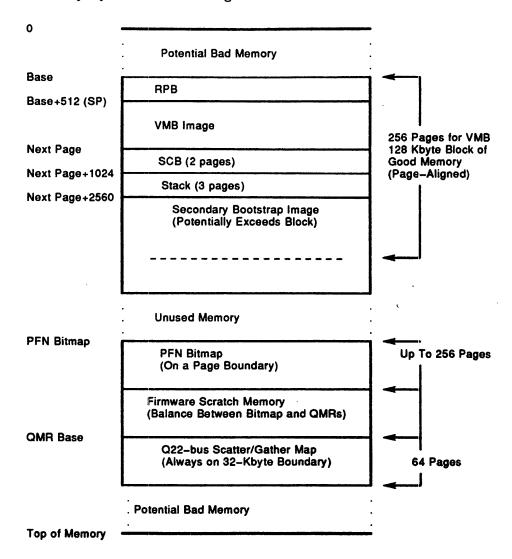

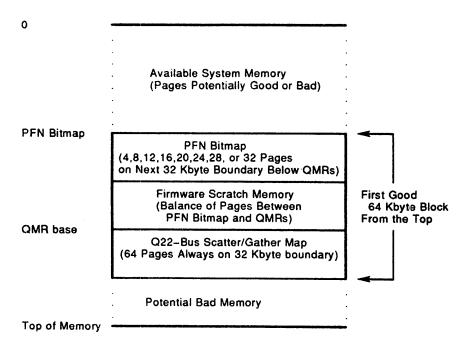

|   | E.1 Main Memory Layout and State                                                                                                               | 384                             |

|   | E.1.1 Reserved Main Memory                                                                                                                     | 385                             |

|   | E.1.1.1 Page Frame Number (PFN) Bitmap                                                                                                         | 385                             |

|   | E.1.1.2 Scatter/Gather Map E.1.1.3 Firmware Scratch Memory                                                                                     | 385<br>386                      |

|   | E.1.2 Contents of Main Memory                                                                                                                  | 386                             |

|   | E.2 Memory Controller Registers                                                                                                                | 386                             |

|   | E.2.1 Primary (On-Chip) Cache                                                                                                                  | 386                             |

|   | E.2.2 Translation Buffer                                                                                                                       | 386                             |

|   | E.2.3 Halt-Protected Space                                                                                                                     | 386                             |

| F | Maintenance Operation Protocol (MOP) Support |              |

|---|----------------------------------------------|--------------|

|   | F.1 Network Listening 3                      | 387          |

|   | F.2 MOP Counters 3                           | 392          |

| G | ROM Partitioning                             |              |

|   | G.1 Firmware EPROM Layout 3                  | 396          |

|   | G.1.1 Call-Back Entry Points                 | 397          |

|   | G.1.1.1 CP\$GETCHAR_R4                       | 397          |

|   | G.1.1.2 Of White _ O O 1 _ 1. O 22 _ 2011    | 3 <b>9</b> 8 |

|   | G.1:1.0 O1 \$10012 _ 11 11 1                 | 398          |

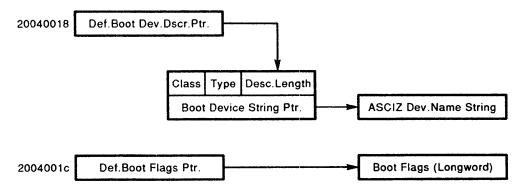

|   | G.1.2 Boot Information Pointers              | 399          |

| Н | RAM Partitioning                             |              |

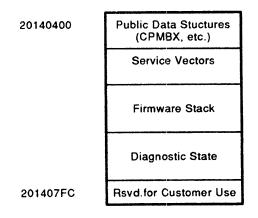

|   | H.1 SSC RAM Layout                           | 401          |

|   |                                              | 401          |

|   |                                              | 402          |

|   | 11.1.0 Primwate Deack                        | 403          |

|   | 11.1.4 Diagnostic State                      | 403          |

|   | H.1.5 User Area                              | 403          |

| ı | Data Structures                              |              |

|   | I.1 Halt Dispatch State Machine              | 404          |

|   | I.2 Restart Parameter Block(RPB)             | 407          |

|   | I.3 VMB Argument List                        | 409          |

| J | Error Messages                               |              |

|   | J.1 Halt Code Messages                       | 411          |

|   |                                              | 413          |

|   | J.3 Console Error Messages                   | 414          |

|   |                                              |              |

# Glossary

Index

| Exampl  | es                                                                                   |            |

|---------|--------------------------------------------------------------------------------------|------------|

| 2–1     |                                                                                      | 16         |

| 2–2     |                                                                                      | 17         |

| 7-1     |                                                                                      | 87         |

| 7–2     |                                                                                      | .88        |

| 7–3     |                                                                                      | .89        |

| 9–1     |                                                                                      | 19         |

| Figures |                                                                                      |            |

| 1-1     | KA670 CPU Module                                                                     | 3          |

| 1–2     | KA670 CPU Module Block Diagram                                                       | 4          |

| 1–3     | KA670 CPU Module Component Side                                                      | 5          |

| 1-4     |                                                                                      | 10         |

| 1–5     |                                                                                      | 11         |

| 2-1     |                                                                                      | 14         |

| 3-1     | <b>.</b>                                                                             | 21         |

| 3–2     |                                                                                      | 22         |

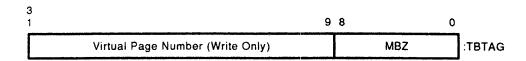

| 3–3     | Translation Buffer Tag (TBTAG)—(IPR 47 <sub>10</sub> 2F <sub>16</sub> )              | 33         |

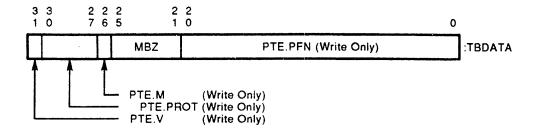

| 3-4     | Translation Buffer Data (TBDATA)—(IPR 59 <sub>10</sub> 3B <sub>16</sub> )            | 33         |

| 35      |                                                                                      | 36         |

| 3–6     | Software Interrupt Request Register (SIRR)— (IPL 20 <sub>10</sub> 14 <sub>16</sub> ) | 36         |

| 3–7     | Software Interrupt Summary Register (SISR)— (IPL 21 <sub>10</sub> 15 <sub>16</sub> ) | 36         |

| 3-8     | Information Saved on a Machine Check Exception                                       | 38         |

| 3–9     | Machine Check Error Register (MCESR)— (IPR 38 <sub>10</sub> 26 <sub>16</sub> )       | 43         |

| 3-10    | System Control Block Base Register (SCBB)— (IPL 17 <sub>10</sub> 11 <sub>16</sub> )  | 43         |

| 3–11    | Console Saved PC (SAVPC)— (IPR 42 <sub>10</sub> 2A <sub>16</sub> )                   | 46         |

| 3–12    | Console Saved PSL (SAVPSL)— (IPR 43 <sub>10</sub> 2B <sub>16</sub> )                 | 46         |

| 3–13    | System Identification Register (SID)— (IPR 62 <sub>10</sub> 3E <sub>16</sub> )       | <b>4</b> 8 |

| 3–14    | System Type Register (SYS_TYPE)                                                      | 49         |

| 3–15    | (12 To 10) mo 10)                                                                    | 49         |

| 4-1     |                                                                                      | 55         |

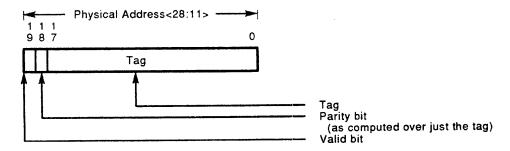

| 4-2     | Primary Cache Tag Entry                                                              | <b>5</b> 5 |

| 4-3     | Primary Cache Data Entry                                                             | 56         |

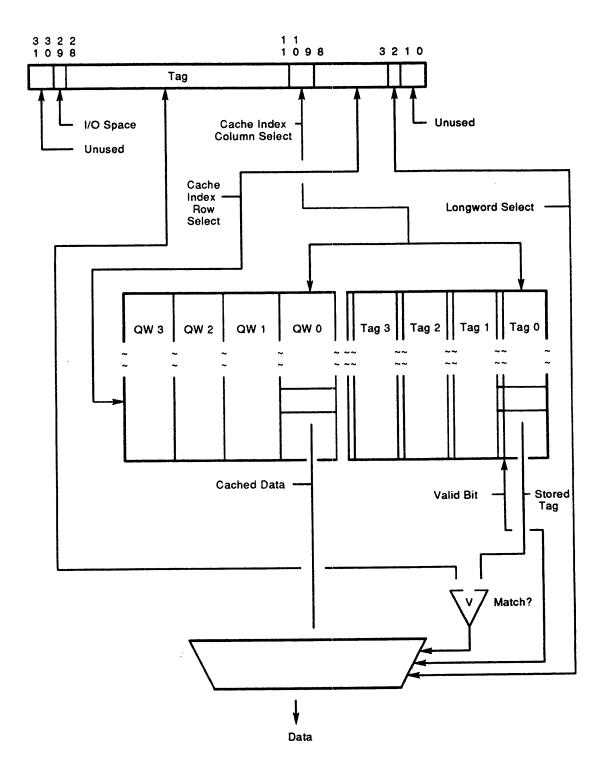

| 4-4     | Primary Cache Physical Address Translation                                           | 57         |

| 4–5     |                                                                                      | 59         |

| 4–6     | -                                                                                    | 63         |

| 4-7     | -                                                                                    | 64         |

| 4–8     |                                                                                      | 64         |

| 4-9     |                                                                                      | 67         |

| 4-10    |                                                                                      | 68         |

| 4–11    |                                                                                      | 69         |

| 4–12    |                                                                                      | 70         |

| 4-13    |                                                                                      | 72         |

|         |                                                                                      | 73         |

| 4–15    | VAX Physical Address in C-Chip's Primary Tag Store Addressing (EPR                   |            |

| 4-16 | Data Bus Format to Access the Primary Tag Store (C-Chip Copy)                            | 74         |

|------|------------------------------------------------------------------------------------------|------------|

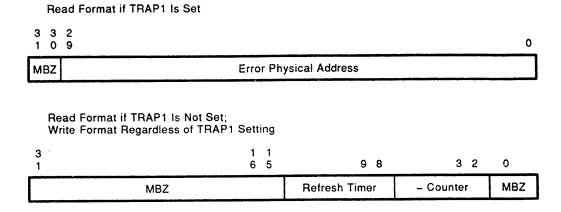

| 4-17 | C-Chip Refresh Register (BCRFR)—(EPR 116 <sub>10</sub> 74 <sub>16</sub> )                | <b>7</b> 5 |

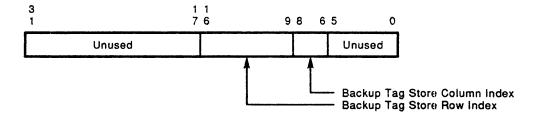

| 418  | Backup Cache Index Register as Used for Backup Cache Tag Store                           | 76         |

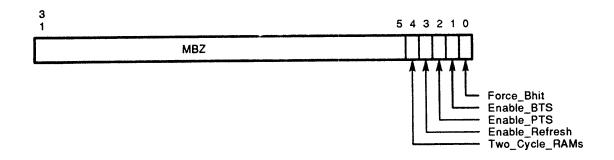

| 419  | Backup Cache Index Register as Used for Primary Cache Tag Store                          | 77         |

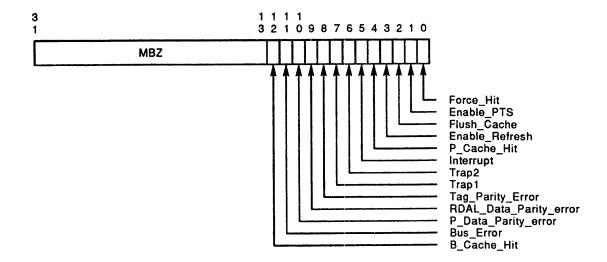

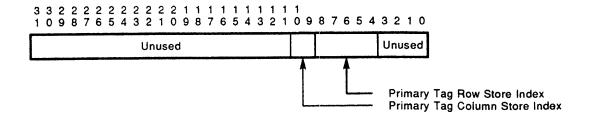

| 4-20 | Backup Cache Status Register (BCSTS)— (EPR 118 <sub>10</sub> 76 <sub>16</sub> )          | 78         |

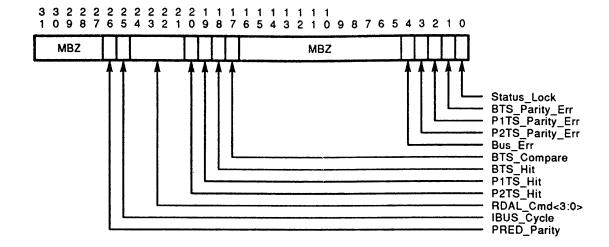

| 4-21 | Backup Cache Control Register (BCCTL)— (EPR 119 <sub>10</sub> 77 <sub>16</sub> )         | 81         |

| 4-22 | Backup Cache C-Chip Error Address Register —(EPR 120 <sub>10</sub> 78 <sub>16</sub> )    | 84         |

| 4-23 | Backup Cache Flush Backup Tag Store Register —(EPR 121 <sub>10</sub> 79 <sub>16</sub> )  | 85         |

| 4-24 | Backup Cache Flush Primary Tag Store Register —(EPR 122 <sub>10</sub> 7A <sub>16</sub> ) | 86         |

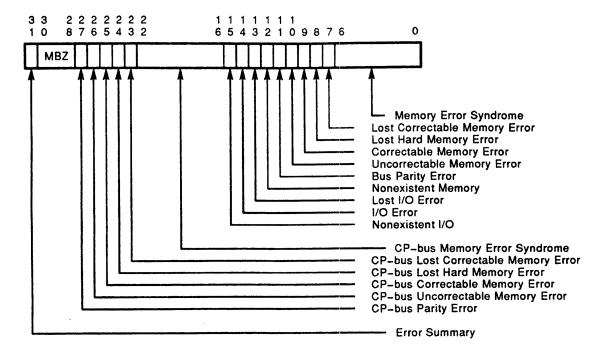

| 4-25 | G-Chip System Error Status Register (MEMCSR32)                                           | 89         |

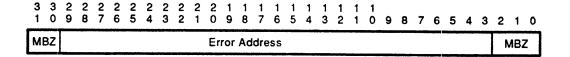

| 4-26 | G-chip Memory Error Address Register (MEMCSR33)                                          | 92         |

| 4-27 | G-Chip I/O Error Address Register (MEMCSR 34)                                            | 93         |

| 4-28 | CP bus Error Address Register (MEMCSR 35)                                                | 93         |

| 429  | G-Chip Mode Control and Diagnostic Status Register (MEMCSR 36)                           | 94         |

| 4-30 | 32-Bit Modified Hamming Code                                                             | 102        |

| 5-1  | Console Receiver Control/Status Register— (IPR 32 <sub>10</sub> 20 <sub>16</sub> )       | 111        |

| 5-2  | Console Receiver Data Buffer – (IPR 33 <sub>10</sub> 21 <sub>16</sub> )                  | 111        |

| 5–3  | Console Transmitter Control/Status Register—(IPR 34 <sub>10</sub> 22 <sub>16</sub> )     | 113        |

| 5-4  | Console Transmitter Data Buffer— (IPR 35 <sub>10</sub> 23 <sub>16</sub> )                | 114        |

| 5–5  | Time-of-Year Clock (TODR) - (EPR 27 <sub>10</sub> 1B <sub>16</sub> )                     | 115        |

| 56   | Interval Timer (ICCS) – (EPR 24 <sub>10</sub> 18 <sub>16</sub> )                         | 116        |

| 5-7  | Timer Control Registers (TCR0 and TCR1)                                                  | 117        |

| 5–8  | Timer Interval Registers (TIR0 and TIR1)                                                 | 118        |

| 5–9  | Timer Next Interval Registers (TNIR0 and TNIR1)                                          | 118        |

| 5-10 | Timer Interrupt Vector Registers (TIVR0 and TIVR1)                                       | 119        |

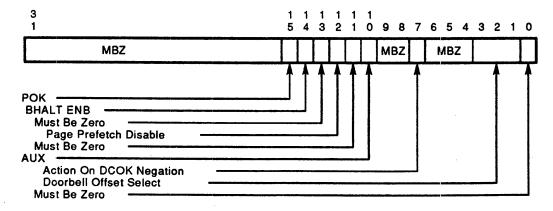

| 6–1  | Boot and Diagnostic Register (BDR)                                                       | 121        |

| 6–2  | Diagnostic LED Register (DLEDR)                                                          | 124        |

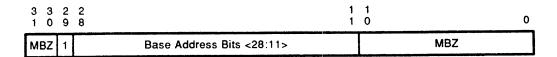

| 6-3  | SSC Base Address Register (SSCBR)                                                        | 127        |

| 6-4  | BDR Address Decode Match Register (BDMTR)                                                | 128        |

| 6–5  | BDR Address Decode Mask Register (BDMKR)                                                 | 128        |

| 66   | SSC Configuration Register (SSCCR)                                                       | 128        |

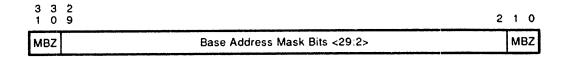

| 6-7  | CP Bus Timeout Control Register (CBTCR)                                                  | 131        |

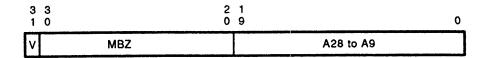

| 7-1  | Q22-bus Address Translation                                                              | 133        |

| 7–2  | Q22-bus Map Register Format                                                              | 135        |

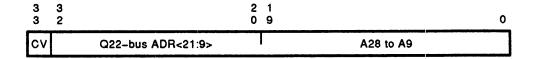

| 7–3  | Q22-bus Map Cache Entry Format                                                           | 136        |

| 7–4  | Interprocessor Communication Register (IPCR)                                             | 138        |

| 7–5  | Q22-bus Map Base Address Register (QBMBR)                                                | 140        |

| 7–6  | System Configuration Register (SCR)                                                      | 140        |

| 7–7  | DMA System Error Register (DSER)                                                         | 142        |

| 7–8  | Q22-bus Error Address Register (QBEAR)                                                   | 144        |

| 7–9  | DMA Error Address Register (DBEAR)                                                       | 144        |

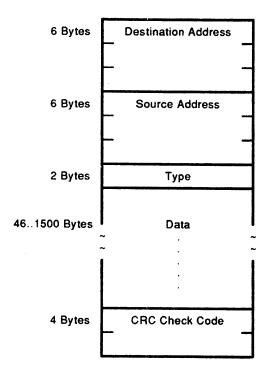

| 7–10 | Ethernet Packet Format                                                                   | 146        |

| 7–11 | Vector Address, IPL, Sync/Asynch (NICSR0)                                                | 150        |

| 7–12 | <u> </u>                                                                                 | 152        |

|      | NICSR2 Format                                                                            | 152        |

| 7 14 | Descriptor List Addresses Format                                                         | 154        |

| 7–15       | NICSR5 Format                                        | 155         |

|------------|------------------------------------------------------|-------------|

| 7–16       | NICSR6 Format                                        | 160         |

| 7-17       | NICSR7 Format                                        | 166         |

| 7–18       | NICSR9 Format                                        | 167         |

| 7–19       | NICSR10 Format                                       | 168         |

| 7–20       | Boot Message                                         | 169         |

| 7-21       | NICSR14 Format                                       | 170         |

| 7–22       | NICSR15 Format                                       | 171         |

| 7–23       | Receive Descriptor Format                            | 173         |

| 7–24       | Transmit Descriptor Format                           | 178         |

| 7–25       | Setup Frame Descriptor Format                        | 184         |

| 7-26       | Perfect Filtering Setup Frame Buffer Format          | 186         |

| 7–27       | Imperfect Filtering Setup Frame Format               | 188         |

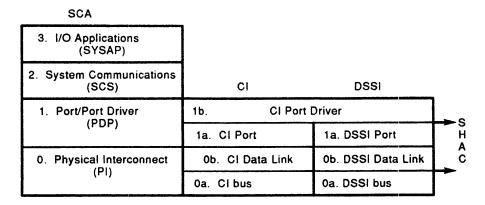

| 7-28       | Relationship of the DSSI to SCA and CI               | 200         |

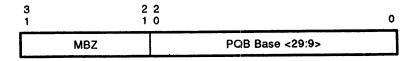

| 7–29       | Port Queue Block Base Register (PQBBR)               | 203         |

| 7–30       | Port Queue Block Base Register (PQBBR) After Reset   | 204         |

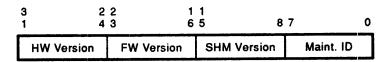

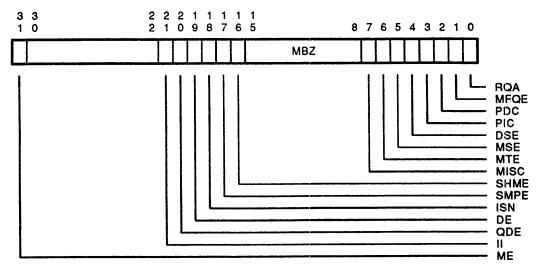

| 7-31       | Port Status Register (PSR) Bits                      | 205         |

| 7–32       | Port Error Status Register (PESR) Bits               | 207         |

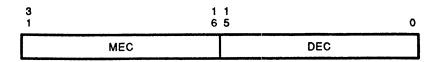

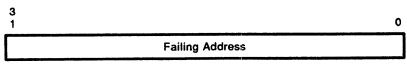

| 7–33       | Port Failing Address Register (PFAR)                 | 207         |

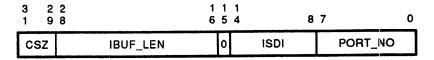

| 7–34       | Port Parameter Register (PPR)                        | 208         |

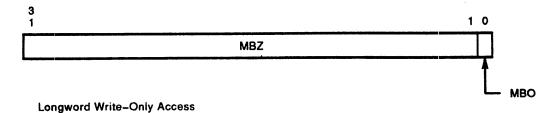

| 7–35       | Port Control Registers                               | 208         |

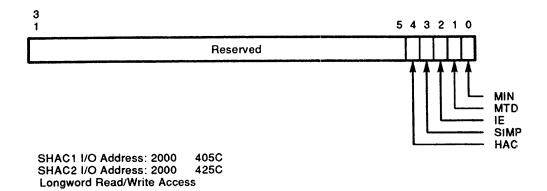

| 7–36       | Port Maintenance Control and Status Register (PMCSR) | 211         |

| 7-37       | SHAC Software Chip Reset (SSWCR)                     | 212         |

| 7-38       | SHAC Shared Host Memory Address (SSHMA)              | 212         |

| 8-1        | Stack Frame for Machine Check Exception              | 222         |

| 8-2        | Machine Check Parse Tree                             | 225         |

| 8–3        | Parse Tree for a Hard Error Interrupts               | 235         |

| 8-4        | Soft Error Interrupt Parse Tree                      | 238         |

| 9-1        | KA670 Firmware Structural Components                 | 248         |

| 9-2        | Language Selection Menu                              | <b>2</b> 54 |

| 9–3        | Normal Diagnostic Countdown                          | 255         |

| 9-4        | Abnormal Diagnostic Countdown                        | <b>25</b> 5 |

| 9-5        | Console Boot Display With No Default Boot Device     | <b>25</b> 5 |

| 96         | Memory Layout Before VMB Entry                       | 258         |

| 9–7        | VMB Boot Flags (/R5:)                                | 260         |

| 9–8        | Memory Layout at VMB Exit                            | <b>26</b> 2 |

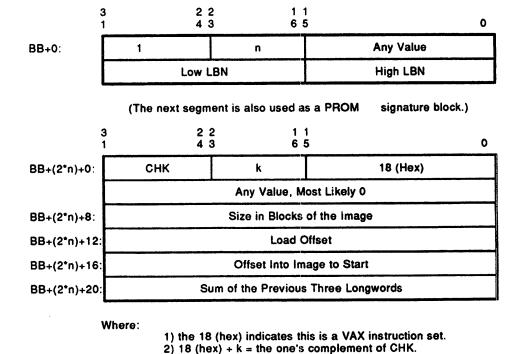

| 9-9        | Boot Block Format                                    | <b>26</b> 3 |

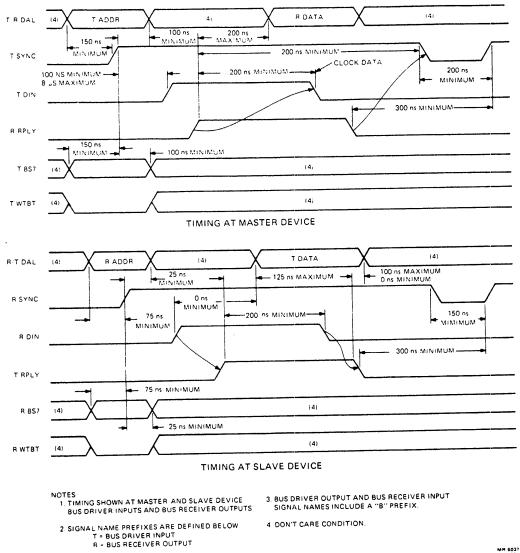

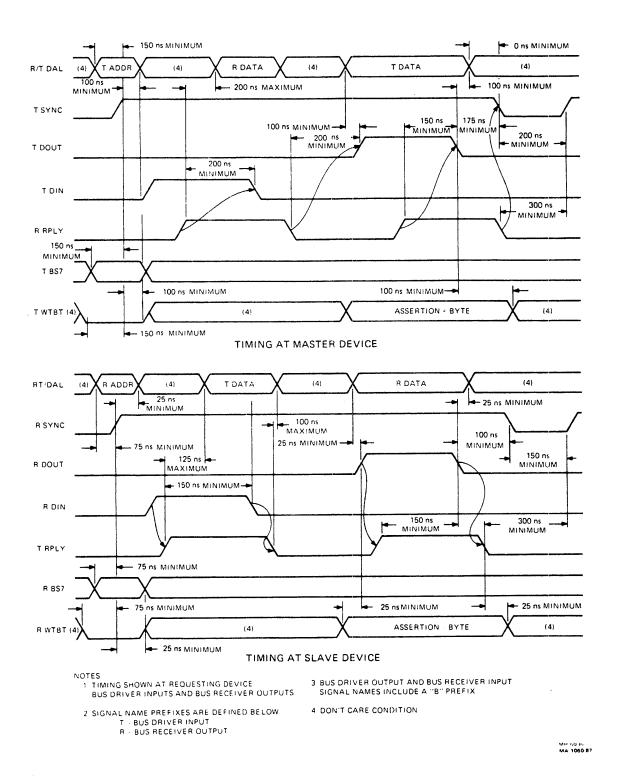

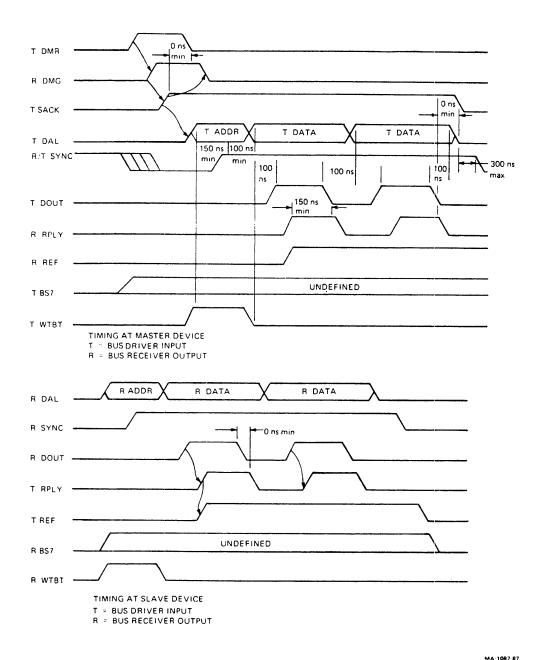

| A-1        | DATI Bus Cycle                                       | 328         |

| A-2        | DATI Bus Cycle Timing                                | 329         |

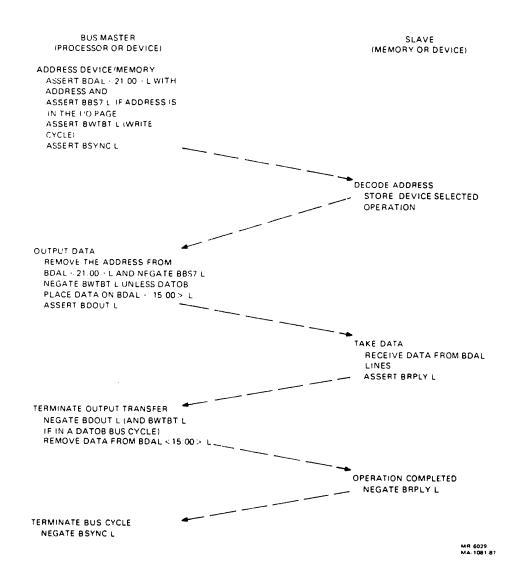

| A-3        | DATO or DATOB Bus Cycle                              | 330         |

| A-4        | DATO or DATOB Bus Cycle Timing                       | 331         |

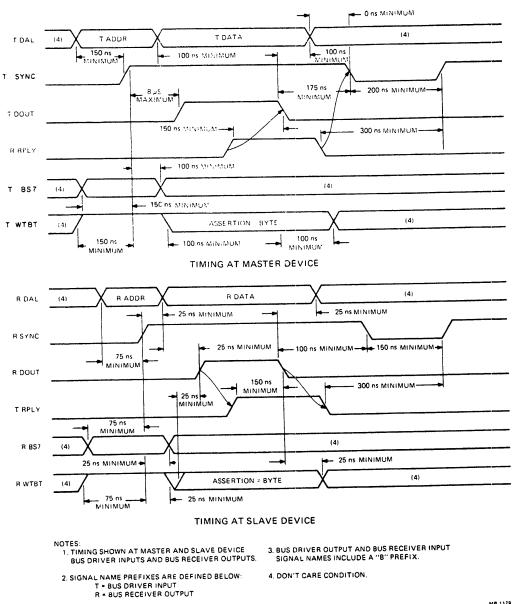

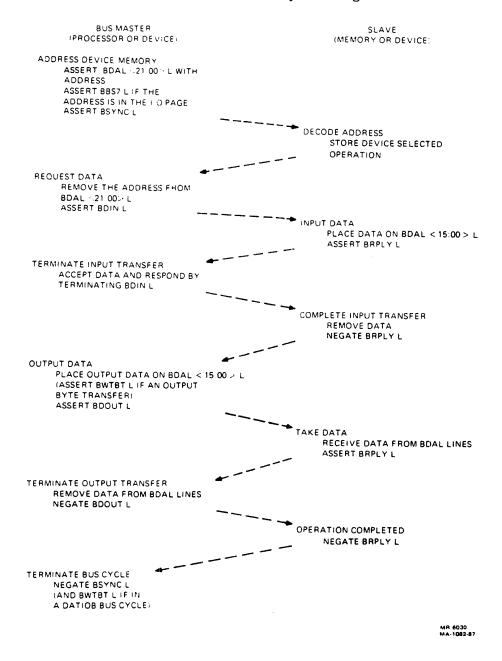

| A-5        | DATIO or DATIOB Bus Cycle                            | 332         |

| A-6        | DATIO or DATIOB Bus Cycle Timing                     | 333         |

| A-7        | DMA Protocol                                         | 335         |

| A8         | DMA Request/Grant Timing                             | 336         |

| <b>Δ_Q</b> | DATRI Rus Cycle Timing                               | 337         |

|     | A-10            | DATBO Bus Cycle Timing                                  | 338  |

|-----|-----------------|---------------------------------------------------------|------|

|     | A-11            | Interrupt Request/Acknowledge Sequence                  | 343  |

|     | A-12            | Interrupt Protocol Timing                               | 344  |

|     | A-13            | Position-Independent Configuration                      | 348  |

|     | A-14            | Position-Dependent Configuration                        | 346  |

|     | A-15            | Bus Line Terminations                                   | 348  |

|     | A-16            | Single-Backplane Configuration                          | 350  |

|     | A-17            | Multiple Backplane Configuration                        | 352  |

|     | A-18            | Typical Pin Identification System                       | 353  |

|     | A-19            | Quad-Height Module Contact Finger Identification        | 354  |

|     | A-20            | Typical Q22-bus Module Dimensions                       | 358  |

|     | E-1             | Memory Layout After Power-Up Diagnostics                | 384  |

|     | G-1             | KA670 EPROM Layout                                      | 396  |

|     | H-1             | KA670 SSC BBU RAM Layout                                | 401  |

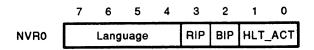

|     | H-2             | NVR0 (20140400): Console Program Mailbox (CPMBX)        | 402  |

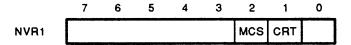

|     | H-3             | NVR1 (20140401)                                         | 402  |

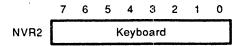

|     | H-4             | NVR2 (20140402)                                         | 403  |

|     |                 |                                                         |      |

| Tab | les             |                                                         |      |

|     | 1               | Conventions                                             |      |

|     | 3–1             |                                                         | xxii |

|     | 3-2             | General-Purpose Register Descriptions                   | 22   |

|     | 3-3             | Internal Process Register Descriptions                  | 23   |

|     | 3-4             | KA670 Internal Processor Registers                      | 24   |

|     | 3 <del></del> 5 | Category 2 Internal Processor Registers                 | 28   |

|     | 3–6             | Category 2 Internal Processor Registers                 | 29   |

|     | 30<br>37        | Interrupt Priority Levels                               | 34   |

|     | 3–8             | Exception Classes                                       | 37   |

|     | 3–9             | Floating Point Errors                                   | 39   |

|     |                 | Memory Management Errors                                | 39   |

|     | 3-10            | Interrupt Errors                                        | 40   |

|     |                 | Microcode Errors                                        | 40   |

|     |                 | Read Errors                                             | 41   |

|     |                 | Write Errors                                            | 41   |

|     |                 | RDAL Bus Errors                                         | 41   |

|     |                 | Internal State Information Field                        | 42   |

|     |                 | The System Control Block Format                         | 43   |

|     |                 | CPU State After a Halt                                  | 46   |

|     |                 | HALT Codes                                              | 47   |

|     |                 | System Identification Register (SID)                    | 48   |

|     |                 | System Type Register (SYS_TYPE)                         | 49   |

|     |                 | Accelerator Control and Status Register Bit Definitions | 50   |

|     |                 | Primary Cache Internal Processor Registers              | 58   |

|     |                 | Primary Cache Status Register                           | 59   |

|     |                 | Backup Cache External/Internal Processor Registers      | 71   |

|     |                 | Backup Cache Backup Tag Store Register Bits             | 72   |

|     | 4-5             | Tag Store Subblock Numbers                              | 73   |

Contents xvii

| 46   | Primary Tag Store Register Bits                          | 75  |

|------|----------------------------------------------------------|-----|

| 4-7  | C-Chip Refresh Register Bits                             | 76  |

| 4–8  | Backup Cache Index Register as used for Backup Cache Tag | 76  |

| 4-9  | Backup Cache Index Register as Used for Primary Cache    | 77  |

| 4-10 | Backup Cache Status Register Bits                        | 78  |

| 4-11 | Status Bits Loaded in BCSTS During C-Chip Transactions   | 80  |

| 4–12 | Backup Cache Control Register Bits                       | 81  |

| 4-13 | Reenabling a Turned-Off Tag Store                        | 84  |

| 4–14 | Backup Cache C-Chip Error Address Register Bits          | 85  |

| 4–15 | G-Chip Registers                                         | 88  |

| 4–16 | G-Chip System Error Status Register Bits                 | 89  |

| 4-17 | Memory Error Address Register Bits                       | 92  |

| 4-18 | G-Chip I/0 Error Address Register Bits                   | 93  |

| 4-19 | CP Bus Error Address Register Bits                       | 93  |

| 4-20 | G-Chip Mode Control and Diagnostic Status Register Bits  | 95  |

| 4-21 | Syndrome Examples                                        | 102 |

| 4-22 | GMI Port Priority                                        | 104 |

| 4-23 | System Requirements for Buffered Writes and Invalidates  | 107 |

| 5–1  | Console Registers                                        | 110 |

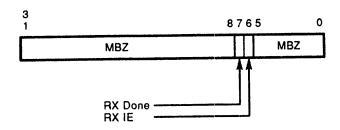

| 5-2  | Console Receiver Control/Status Register Bits            | 111 |

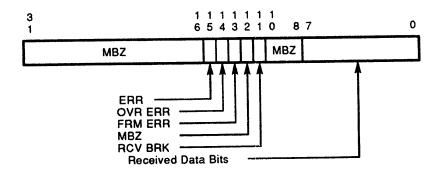

| 5–3  | Console Receiver Data Buffer Bits                        | 112 |

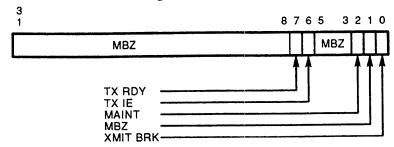

| 5-4  | Console Transmitter Data Buffer                          | 113 |

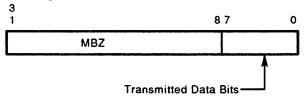

| 5-5  | Console Transmitter Data Buffer Bits                     | 114 |

| 56   | Baud Rate Selection                                      | 115 |

| 5–7  | Interval Timer Bits                                      | 116 |

| 5–8  | Timer Control Register Bits                              | 117 |

| 6–1  | Boot and Diagnostic Register Bits                        | 122 |

| 6–2  | Diagnostic LED Register Bits                             | 124 |

| 63   | Power-Up Modes                                           | 125 |

| 6-4  | SSC Configuration Register Bits                          | 129 |

| 6–5  | CP Bus Timeout Control Register Bits                     | 131 |

| 7-1  | Q22-bus Map Register Addresses                           | 134 |

| 7-2  | Q22-bus Map Register Bits                                | 135 |

| 7–3  | Q22-bus Map Cache Entry Bit Description                  | 137 |

| 7–4  | Interprocessor Communication Register Bits               | 138 |

| 7–5  | System Configuration Register Bits                       | 141 |

| 7–6  | DMA System Error Register Bits                           | 142 |

| 7–7  | Bit Access Modes                                         | 149 |

| 7–8  | NICSR0 Bits                                              | 151 |

| 7–9  | NICSR1 Bits                                              | 152 |

| 7–10 | NICSR2 Bits                                              | 153 |

| 7–11 | Descriptor List Address Bits                             | 154 |

| 7–12 | NICSR5 Bits                                              | 155 |

| 7–14 | NICSR6 Bits                                              | 160 |

| 7–15 | NICSR7 Bits                                              | 166 |

| 7–16 | NICSR9 Bits                                              | 167 |

|      |                                                          |     |

| 7–17        | NICSR10 Bits                                              | 169 |

|-------------|-----------------------------------------------------------|-----|

| 7–18        | NICSR11,12,13 Bits                                        | 170 |

| 7–19        | NICSR14 Bits                                              | 170 |

| 7–20        | NICSR15 Bits                                              | 171 |

| 7–21        | RDES0 Bits                                                | 173 |

| 7–22        | RDES1 Bits                                                | 176 |

| 7–23        | RDES2 Bits                                                | 176 |

| 7–24        | RDES3 Bits                                                | 177 |

| 7–25        | Receive Descriptor Status Validity                        | 177 |

| 7–26        | TDES0 Bits                                                | 178 |

| 7–27        | TDES1 Bits                                                | 180 |

| 7–28        | TDES2 Bits                                                | 182 |

| 7–29        | TDES3 Bits                                                | 182 |

| 7–30        | Transmit Descriptor Status Validity                       | 183 |

| 7–31        | Setup Frame Descriptor Bits                               | 184 |

| 7–32        | NICSR Field Values After Reset                            | 191 |

| 7-33        | Reception Process State Transitions                       | 194 |

| 7-34        | Transmission Process State Transitions                    | 195 |

| 7–35        | CSMA/CD Counters                                          | 197 |

| 7–36        | Port Queue Block Base Address Register (PQBBR) Bits       | 204 |

| 7-37        | Port Queue BLock Base Address Register Bits               | 204 |

| 7–38        | Port Status Register Bits                                 | 205 |

| 7–39        | Port Error Status Register (PESR) Bits                    | 207 |

| 7-40        | Port Parameter Register (PPR) Bits                        | 208 |

| 7-41        | Port Maintenance Control and Status Register (PMCSR) Bits | 211 |

| 8-1         | CPU Internally Generated SCB Entry Points                 | 214 |

| 8–2         | Error Summary Based on SCB Entry Points                   | 215 |

| 8–3         | Console Halt Codes                                        | 220 |

| 8-4         | Interrupt State Format                                    | 222 |

| 8–5         | AT (Address-Type) Codes                                   | 223 |

| 86          | Data Length (DL) Codes                                    | 223 |

| 8–7         | Machine Check Fault Codes                                 | 224 |

| 8–8         | MCHK_FP_PROTOCOL_ERROR                                    | 227 |

| 8-9         | MCHK_FP_OPERAND_PARITY                                    | 228 |

| 9–1         | Halt Action Summary                                       | 250 |

| 9–2         | LED Codes                                                 | 256 |

| 9-3         | KA670 Supported Boot Devices                              | 259 |

| 9 <u>-4</u> | Command, Parameter, and Qualifier Keywords                | 269 |

| 9–5         | Console Symbolic Addresses                                | 270 |

| 9–6         | Console Command Summary                                   | 315 |

| 97          | -                                                         | 317 |

|             | Console Qualifier Summary                                 |     |

| A-1         | Data and Address Signal Assignments                       | 322 |

| A-2         | Control Signal Assignments                                | 323 |

| A-3         | Power and Ground Signal Assignments                       | 324 |

| A-4         | Spare Signal Assignments                                  | 325 |

| A-5         | Data Transfer Operations                                  | 325 |

### xx Contents

| A6           | Bus Signals for Data Transfers                  | 326 |

|--------------|-------------------------------------------------|-----|

| A-7          | Bus Pin Identifiers                             | 355 |

| B-1          | KA670 Console Connector (J2) Pinout             | 361 |

| D-1          | Integer Arithmetic and Logical Instructions     | 374 |

| D-2          | Address Instructions                            | 377 |

| D-3          | Variable Length Bit Field Instructions          | 377 |

| D-4          | Control Instructions                            | 377 |

| D-5          | Procedure Call Instructions                     | 378 |

| D-6          | Miscellaneous Instructions                      | 378 |

| D-7          | Queue Instructions                              | 379 |

| D-8          | Operating System Support Instructions           | 379 |

| D-9          | Floating Point Instructions                     | 380 |

| D-10         | Microcode-Assisted Emulated Instructions        | 382 |

| F-1          | KA670 Network Maintenance Operations Summary    | 388 |

| F-2          | Supported MOP Messages                          | 389 |

| F-3          | Ethernet & IEEE 802.3 Packet Headers            | 391 |

| F-4          | MOP Multicast Addresses and Protocol Specifiers | 391 |

| F-5          | MOP Counter Block                               | 392 |

| I-1          | Firmware State Transition Table                 | 405 |

| I-2          | Restart Parameter Block Fields                  | 407 |

| I <b>–</b> 3 | VMB Argument List                               | 410 |

| J-1          | HALT Messages                                   | 412 |

| J-2          | VMB Error Messages                              | 413 |

| J-3          | Console Error Messages                          | 414 |

|              |                                                 |     |

# **About This Manual**

The KA670 CPU Module Technical Manual documents the functional, physical, and environmental characteristics of the KA670 CPU module. The manual also includes information on the MS670 memory expansion modules.

There are two versions of the KA670 CPU module, KA670-AA and KA670-BA. This manual covers both versions. The KA670-BA CPU module is designed for use with workstations and servers. The KA670-BA is functionally equivalent to the KA670-AA, except that it does not support multiuser VMS and ULTRIX operating system licenses.

#### **Audience**

This manual is intended for a design engineer or applications programmer who is familiar with Digital's extended LSI-11 bus (Q22-bus) and the VAX instruction set. This manual should be used along with the VAX Architecture Reference Manual as a programmer's reference to the module.

# Organization

The manual is divided into three parts.

#### Overview and Installation

- Chapter 1, "Overview," introduces the KA670 CPU module, the MS670 memory module, and the H3604 console module, including module features and specifications.

- Chapter 2, "Installation and Configuration," describes the procedures for installing and configuring the CPU, memory, and console modules in the Q22-bus backplanes and system enclosures.

#### **Architecture**

- Chapter 3, "Central Processor and Floating Point Unit," describes the functions of the central processing unit (P-chip) and the floating point unit (F-chip).

- Chapter 4, "Cache and Main Memory," describes the operation of the KA670 CPU module's cache memory as well as the feature of main memory.

- Chapter 5, "The Console Line, TOY Clock, and Bus System," describes the console serial line and the time-of-year clock. The chapter also provides an overview of the KA670 bus system.

- Chapter 6, "KA670 Boot and Diagnostic Facility," describes the boot and diagnostic registers, EPROM memory, battery backed-up RAM and hardware initialization.

- Chapter 7, "Interface Subsystems," describes the interfaces the KA670 CPU module uses for the Q22-bus, Ethernet, and mass storage bus.

Chapter 8, "KA670 Error Handling," describes unexpected KA670 system error exceptions and interrupts, from the macrocoder's point of view.

#### Firmware

• Chapter 9, "Firmware," describes the entry dispatch code, boot diagnostics, device booting sequence, console program, and console commands.

#### **Appendices**

- Appendix A, "Q22-bus Specification," describes the low-end member of Digital's bus family. All of Digital's microcomputers, such as the MicroVAX 3500, MicroVAX 3600, and MicroPDP-11, use the Q22-bus.

- Appendix B, "Specifications," describes the physical, electrical, and environmental characteristics of the KA670 CPU module.

- Appendix C, "Address Assignments," provides a map of VAX memory space.

- Appendix D, "VAX Instruction Set," is a list of the VAX instructions, provided for reference only.

- Appendix E, "Machine State on Power-Up," describes the state of the KA670 after a

power-up halt.

- Appendix F, "Maintenance Operation Protocol (MOP) Support," describes the maintenance operation protocol (MOP) support features in the KA670 firmware.

- Appendix G, "ROM Partitioning," describes the public ROM partitioning and subroutine entry points that are guaranteed to be compatible over future versions of the KA670 firmware.

- Appendix H, "RAM Partitioning," describes how the KA670 firmware partitions the 1 kilobyte of battery backed-up RAM.

- Appendix I, "Data Structures," describes the global data structures used by the KA670 firmware.

- Appendix J, "Error Messages," provides a list of the expected responses to error conditions that may be encountered during various transactions on the KA670 module.

- The glossary defines many of the acronyms and new terms used in this manual.

#### **Conventions**

The following conventions are used in this manual:

Table 1 Conventions

| Convention                           | Meaning                                                                                                                                                                  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <x:y></x:y>                          | Represents a bit field, a set of lines, or a set of signals, ranging from x through y For example, R0 <7:4> Indicates bits 7 through 4 in a general-purpose register R0. |

| [x:y]                                | Represents a range of bits, from y through x.                                                                                                                            |

| 2014 0030                            | Eight-digit numbers in this document are hexadecimal longwords, typically representing VAX-32 bit addresses or data.                                                     |

| 456 <sub>10</sub> , 12 <sub>16</sub> | In sections where octal, decimal, and hexadecimal numbers may appear, the radix of a number is included to avoid confusion.                                              |

| Return                               | Keys or switches that are labeled on the equipment appear in a box.                                                                                                      |

| Ctrl C                               | For key sequences that begin with the Ctrl key, hold down Ctrl and press the second key.                                                                                 |

| Caution                              | Contains information to prevent damage to equipment.                                                                                                                     |

| Note                                 | Contains general information.                                                                                                                                            |

| variable                             | The names of variable command parameters and options appear in italics.                                                                                                  |

| {}                                   | Encloses a required part of a console command.                                                                                                                           |

| Ē                                    | Encloses an option to a console command.                                                                                                                                 |

| •••                                  | Represents a list command elements.                                                                                                                                      |

#### **Related Documents**

The following documents are related to the KA670 CPU:

KA670 CPU System Maintenance Manual EK-347AA-MG MicroVAX Maintenance Kit QZ-K19AA-GZ130 EB-26115-46 VAX Architecture Handbook EY-3459E-DB VAX Architecture Reference Manual

You can order these documents by phone or mail.

#### Continental USA and Puerto Rico

Call 800-258-1710 or mail to:

Digital Equipment Corporation P.O. Box CS2008 Nashua, NH 03061

#### New Hampshire, Alaska, and Hawaii

Call 1-603-884-6660.

#### Outside the USA and Puerto Rico Mail to:

Digital Equipment Corporation

Attn: Accessories and Supplies Business Manager c/o Local Subsidiary or Digital-Approved Distributor

# Overview and Installation

- Chapter 1, Overview

- Chapter 2, Installation and Configuration

This chapter describes the KA670 CPU module, MS670 memory module, and H3604 console module.

#### 1.1 KA670 CPU Module

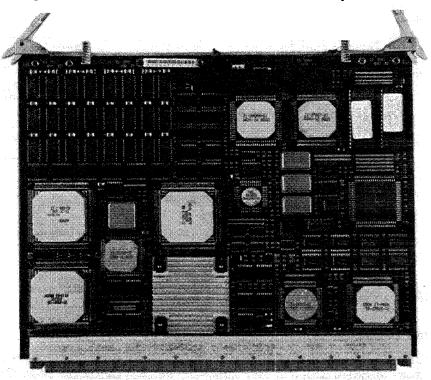

The KA670 (Figure 1-1) is a quad-height VAX processor module for the Q22-bus. The KA670 is designed for use in high-speed, real-time applications and in multiuser, multitasking environments. The KA670 uses a cache memory to maximize performance.

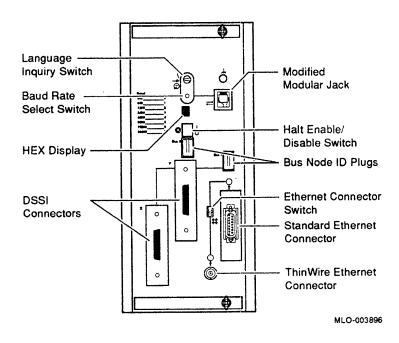

Figure 1-1 KA670 CPU Module

The KA670 is used in the MicroVAX 4000-300 system, which is housed in the BA440 enclosure. There are no jumpers or switches to configure. Fuses are located on the H3604 console module.

The KA670 can be configured only as an arbiter CPU on the Q22-bus, where it arbitrates bus mastership and fields bus interrupt requests and any on-board interrupt requests.

The KA670 uses a 100-pin ribbon cable to communicate with the H3604 CPU console module. The module contains configuration switches, Ethernet and DSSI connectors, and a LED display. Section 1.7 describes the H3604 module.

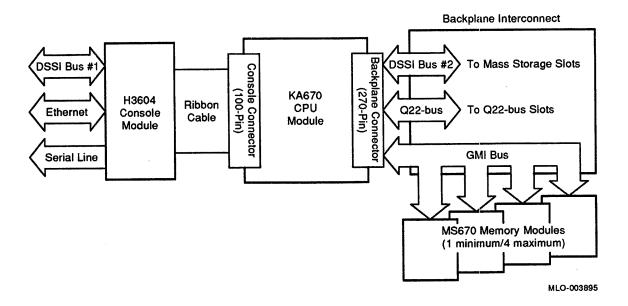

A single KA670 CPU module can support up to four MS670 memory modules. The KA670 and MS670 modules mount in dedicated backplane slots in the BA440 enclosure. The KA670 CPU module communicates with the MS670 memory modules across a memory interconnect located on a 270-pin backplane connector. The backplane connector also connects the subsystem with the Q22-bus and one DSSI bus. Together, the CPU and memory modules form a VAX subsystem that uses the DSSI bus to communicate with mass storage devices and the Q22-bus to communicate with I/O devices. Figure 1–2 is a block diagram of the subsystem major functions.

Figure 1–2 KA670 CPU Module Block Diagram

#### 1.1.1 Module Components

The KA670 CPU is a quad-height module that mounts in a dedicated CPU backplane slot. The MS670 memory modules mount in four dedicated memory backplane slots. The CPU module is fingerless and uses a 270-pin high-density, right-angle connector to connect to the backplane.

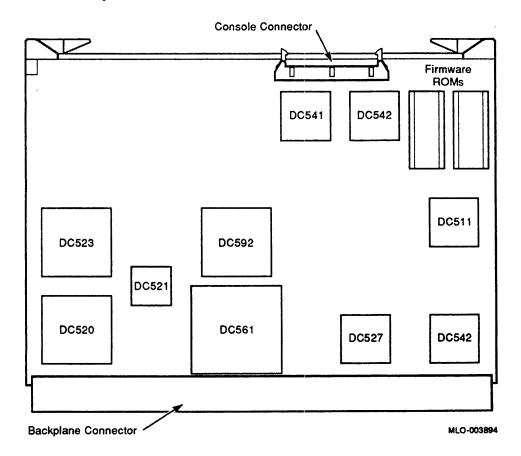

KA670 CPU module includes the following major hardware components. Figure 1-3 shows chip locations, using the chip identification numbers.

- DC520 (P-chip): VAX central processor with a 143 MHz clock

- DC523 (F-chip): Floating point accelerator

- DC592 (C-chip): Two-level cache and its bank of associated RAM chips

- DC561 (G-chip): Main memory controller

- DC521: Clock

- DC527 (CQBIC): Q22-bus interface

- DC541 (SGEC): Ethernet interface

- DC542 (SHAC): DSSI interface chips (2)

- DC511 (SSC): System support chip

- DC509: Clock

- Two firmware ROMs: 256 kilobytes (Each is 128 kilobytes by 8.)

- 100-pin connector to the H3604 console module

- 270-pin connector to the backplane carrying signals for the Q22-bus, the DSSI bus, and the memory interconnect

Figure 1-3 KA670 CPU Module Component Side

The KA670 CPU is designed for use in high-speed, real-time applications and in multiuser, multitasking environments. The KA670 CPU incorporates a two-level cache to maximize system performance. Estimated compute performance for the KA670-AA CPU is 8.0 times that of a VAX 11/780 system.

Functionally, the KA670-AA CPU module is divided into four major areas:

Central processing subsystem

- System support subsystem

- I/O subsystem

- Main memory controller

# 1.2 Central Processing Subsystem

The central processing subsystem contains a CPU chip, a floating point accelerator (FPA) chip, the cache RAMs, and a cache controller chip.

### 1.2.1 Central Processing Unit (P-Chip (DC520))

The CPU chip is the heart of the KA670 module. The CPU executes the 181 instructions in the MicroVAX chip subset of the VAX instruction set. It is implemented by the CPU chip (REX520, DC520), which is in a 224-pin surface-mount package. The CPU chip achieves a 28 ns microcyle at an operating frequency of 143 Mhz. The processor also supports full VAX memory management with demand paging and a 4 gigabyte virtual address space.

The central processor supports the MicroVAX instruction set with the following string instructions:

- CMPC3

- CMPC5

- LOCC

- SCANC

- SKPC

- SPANC

The central processor provides the following subset of the VAX data types:

- Byte

- Word

- Longword

- Quadword

- Character string

- Variable-length bit field

- Absolute queues

- Self-relative queues

- F-floating

- G-floating

- D-floating

Support for the remaining VAX data types can be provided through macrocode emulation.

#### 1.2.2 Floating Point Accelerator (F-Chip (DC523))

The floating point accelerator is implemented by the F-chip, which executes the VAX f\_, d\_, and g\_ floating point instructions. The F-chip receives opcode information from the P-chip, and receives operands directly from memory or the P-chip. The result of the floating point is always returned to the P-chip.

The floating point accelerator executes 61 floating point instructions and 2 longwordlength integer multiply instructions in the VAX base instruction group. The F-chip is in a 224-pin surface mount package.

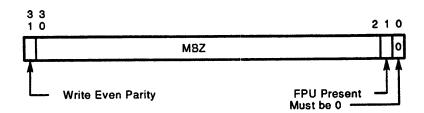

#### 1.2.3 The Cache

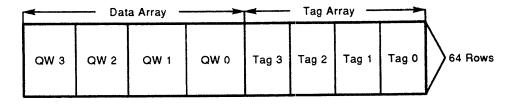

The KA670 processor module uses a two-level cache to maximize CPU performance. The first level is the primary cache, consisting of 2 kilobytes on the central processing chip (P-chip). The second level is the backup cache, consisting of 24 16K-by-4 static RAMs and a cache controller chip.

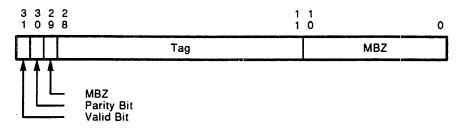

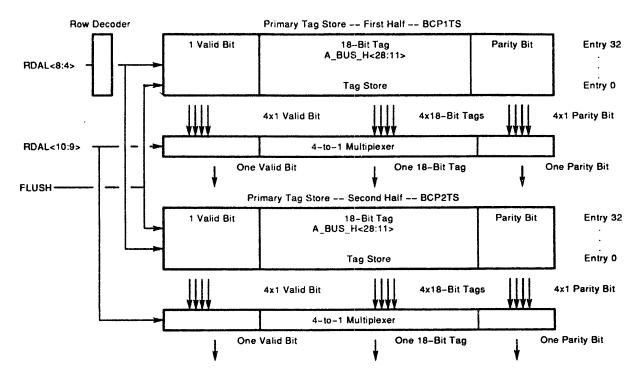

The cache controller chip is implemented with the backup cache chip, (C-chip, DC592), which is in a 224-pin surface mount package. The C-chip contains the tag store and the control logic for the backup cache RAMs, as well as a copy of the primary cache tag store to guarantee primary cache coherence between memory and processor. The chip also provides an additional bus interface for invalidate filtering, to improve performance.