KXJ11-CA User's Guide

Preliminary version 1.3

Copyright (C) 1986 by Digital Equipment Corporation

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may occur in this document.

### CONTENTS

| CHAPTER | 1                                                                                                                                    | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1.1<br>1.2<br>1.3<br>1.4<br>1.4.1<br>1.4.2<br>1.4.2.1<br>1.5<br>1.6<br>1.7                                                           | KXJ11-CA OPERATING MODES  Standalone Mode  IOP Mode  KXJ11-CA From Point Of View Of Arbiter  SOFTWARE ENVIRONMENT  KXJ11-CA SPECIFICATIONS  TERMINOLOGY USED IN THIS DOCUMENT                                                                                                                                                                                                                                                                                                            |

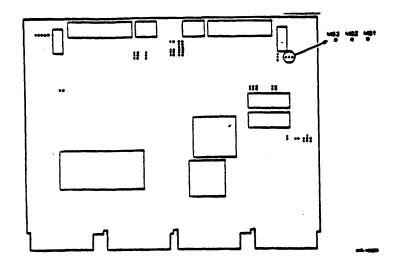

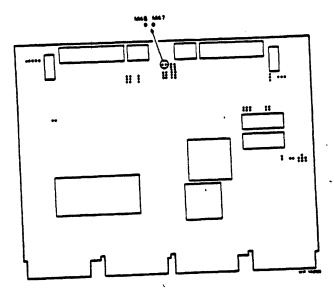

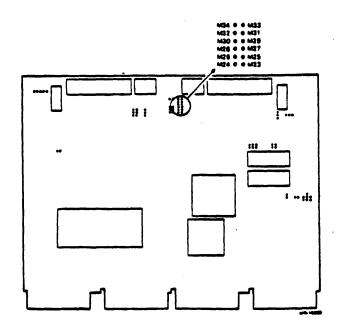

| CHAPTER | 2                                                                                                                                    | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

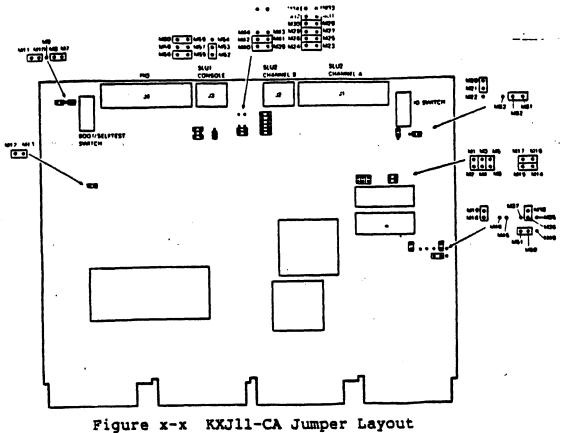

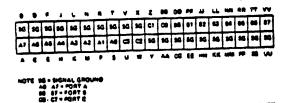

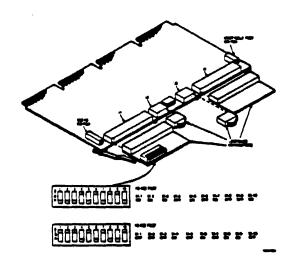

|         | 2.2.7<br>2.2.8<br>2.2.9<br>2.2.10<br>2.2.11<br>2.2.12<br>2.2.13<br>2.2.15<br>2.3<br>2.4.1<br>2.5.1<br>2.5.1<br>2.5.2<br>2.5.3<br>2.6 | SELECTING OPERATING FEATURES  Boot/Selftest Switch  Q-Bus Size  Q-Bus Base Address Selection  DMA Requests  BREAK Enable  HALT Option Selection  Power-Up Option Selection  PROM Addressing  SLU1 Baud Rate  SLU1 Transmitter  SLU1 Transmitter  SLU2 Channel A Receiver  SLU2 Channel B Transmitter  SLU2 Channel B Receiver  SLU2 Channel B Receiver  Real-Time Clock Interrupt  POWER SUPPLY CONSIDERATIONS  INSTALLING THE KXJ11-CA INTO A BACKPLANE  Edge Connector Pin Assignments |

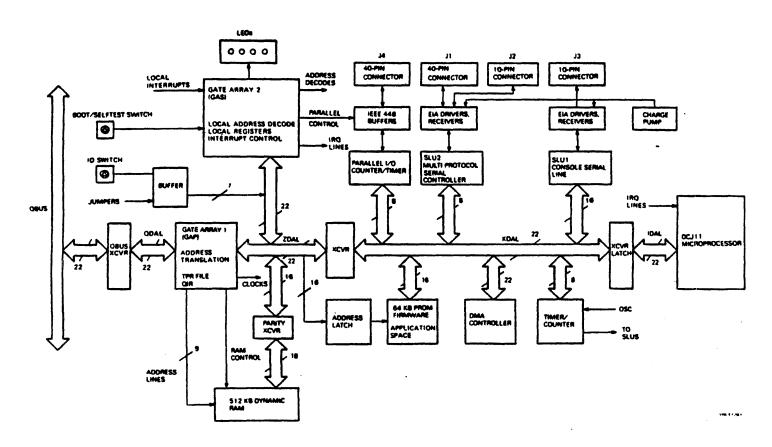

| CHAPTER | 3.1                                                                                                                                  | ARCHITECTURE  INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | 3.2.1                                                                                                                                | J-11 Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2.3    | Two Port Register (TPR) File                                                                                                             | . 3-3 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.2.3.1  | TPRO As A Control Register                                                                                                               | . 3-3 |

| 3.2.3.1. | 1 TPRO As A Control Register                                                                                                             | . 3-4 |

| 3.2.3.1. | 2 TPRO As A Test Register                                                                                                                | . 3-6 |

| 3.2.3.1. | 2 TPRO As A Test Register                                                                                                                | 3-10  |

| 3.2.3.2  | TPR1                                                                                                                                     | 3-11  |

| 3.2.3.3  |                                                                                                                                          | 3-13  |

| 3.2.3.4  | TPR2                                                                                                                                     | 3-13  |

| 3.4.3.4  | TPR3                                                                                                                                     | 3-13  |

| 3.2.3.5  | TPR4 Through TPR15                                                                                                                       | 3-14  |

| 3.2.4    | CPU ID Switch                                                                                                                            | 3-14  |

| 3.2.5    | DMA Controller                                                                                                                           | 3-14  |

| 3.2.6    | Wake-up Circuit                                                                                                                          | 3-15  |

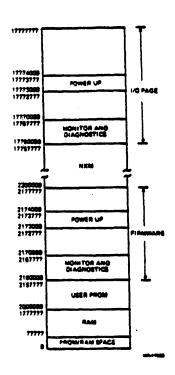

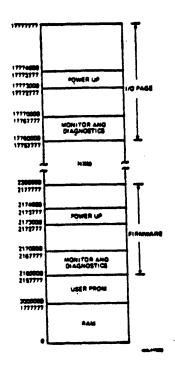

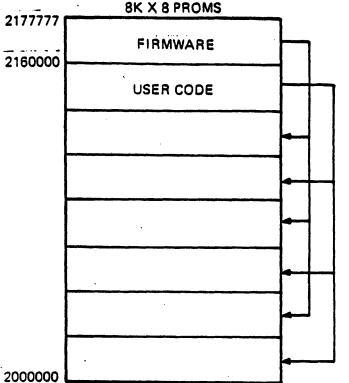

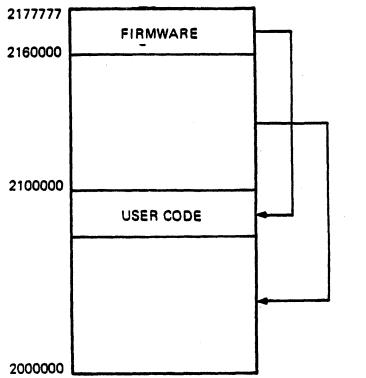

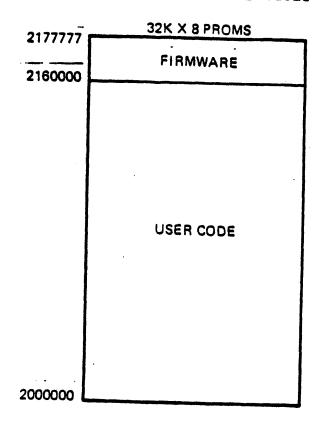

| 3.2.7    | PROM And Firmware Control                                                                                                                | 3-15  |

| 3.2.7.1  | Native Firmware Vs. User-Designed Firmware .                                                                                             | 3-17  |

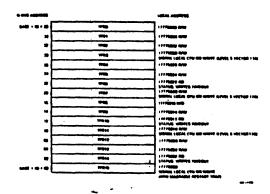

| 3.2.8    | KXJ11-CA Control And Status Registers                                                                                                    | 3-17  |

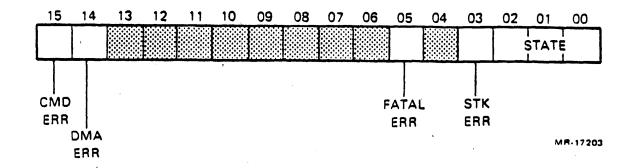

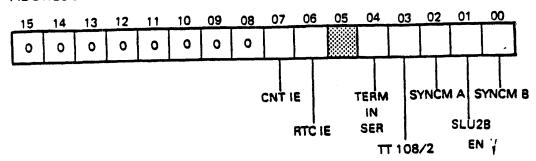

| 3.2.8.1  | KXJll Control/Status Register A (KXJCSRA)                                                                                                | 3-18  |

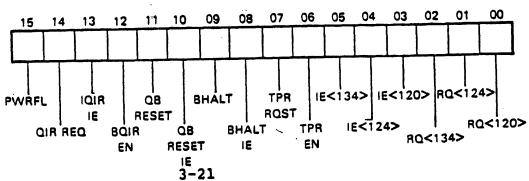

| 3.2.8.2  | KXJ11 Control/Status Register B (KXJCSRB)                                                                                                | 3-19  |

| 3.2.8.3  | <pre>KXJ11 Control/Status Register B (KXJCSRB) KXJ11 Control/Status Register C (KXJCSRC) KXJ11 Control/Status Register D (KXJCSRD)</pre> | 3-21  |

| 3.2.8.4  | KYIII Control/Status Pegister D (KYICSPD)                                                                                                | 3-21  |

| 3.2.8.5  | KXJ11 Control/Status Register E (KXJCSRE)                                                                                                | 3-24  |

|          | WYILL CONTROL/Status Register & (RAUCSRE)                                                                                                | 3-24  |

| 3.2.8.6  |                                                                                                                                          | 3-24  |

| 3.2.8.7  | KXJ11 Control/Status Register H (KXJCSRH)                                                                                                | 3-25  |

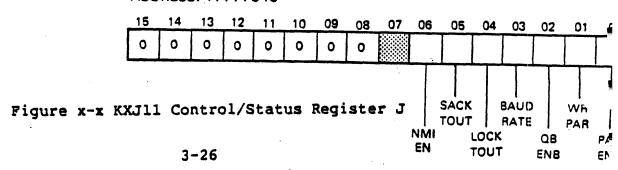

| 3.2.8.8  | KXJ11 Control/Status Register J. (KXJCSRJ)                                                                                               | 3-26  |

| 3.2.9    | Q-Bus Interrupt Register (QIR)                                                                                                           |       |

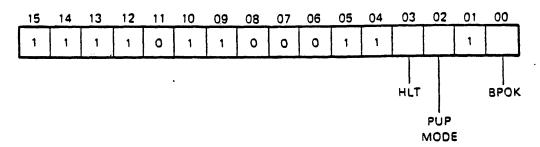

| 3.2.10   | Maintenance Register                                                                                                                     | 3-28  |

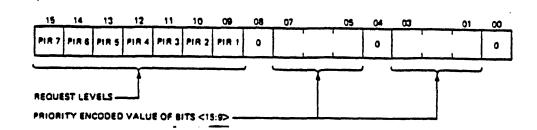

| 3.2.11   | Program Interrupt Request (PIRQ) Register                                                                                                | 3-29  |

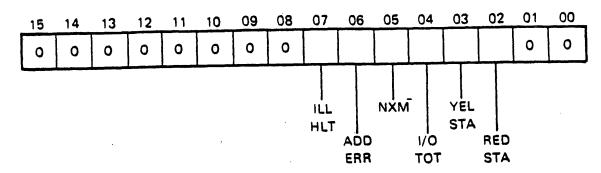

| 3.2.12   | CPU Error Register                                                                                                                       | 3-30  |

| 3.2.13   | Processor Status Word (PSW)                                                                                                              | 3-31  |

| 3.2.14   | Console Asynchronous Serial I/O                                                                                                          | 3-32  |

| 3.2.15   | Synchronous/Asynchronous Serial I/O                                                                                                      | 3-33  |

|          | Denotical t/O                                                                                                                            | 3-33  |

| 3.2.16   | Parallel I/O                                                                                                                             | 3-33  |

| 3.2.17   | -12V Charge Pump                                                                                                                         | 3-33  |

|          | Q-BUS INTERFACE                                                                                                                          | 3-33  |

| 3.4      | TWO-PORT REGISTERS AND COMMUNICATION WITH THE                                                                                            |       |

|          | ARBITER  KXJ11-CA INTERRUPTS  Interrupts From The Q-Bus To The KXJ11-CA                                                                  | 3-34  |

| 3.5      | KXJ11-CA INTERRUPTS                                                                                                                      | 3-34  |

| 3.5.1    | Interrupts From The Q-Bus To The KXJ11-CA                                                                                                | 3-35  |

| 3.5.2    | Interrupts From The KXJ11-CA To The Q-Bus                                                                                                | 3-35  |

| 3.5.3    | Local Interrupts From On-Board Devices                                                                                                   |       |

| 3.6      | SPECIAL INTERRUPT HANDLING                                                                                                               | 3-37  |

| 3.7      | KXJ11-CA RESETS                                                                                                                          | 3-38  |

| 3.7.1    | Software Reset                                                                                                                           | 3-38  |

|          | Software Reset                                                                                                                           | 3-39  |

| 3.7.2    |                                                                                                                                          | 3-41  |

|          |                                                                                                                                          |       |

| 3.8.1    |                                                                                                                                          | 3-41  |

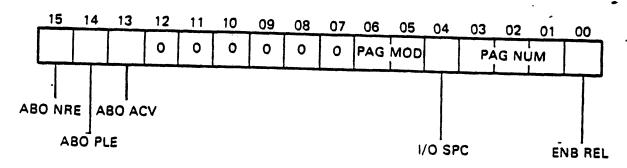

| 3.8.2    | Page Descriptor Registers (PDRs)                                                                                                         | 3-42  |

| 3.8.3    | Memory Management Register 0 (MMR0)                                                                                                      | 3-43  |

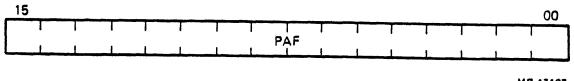

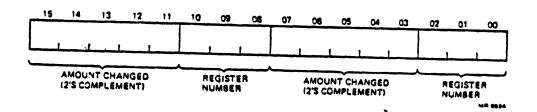

| 3.8.4    | Memory Management Register 1 (MMR1)                                                                                                      | 3-44  |

| 3.8.5    | Memory Management Register 2 (MMR2)                                                                                                      | 3-45  |

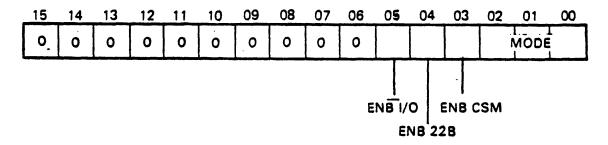

| 3.8.6    | Memory Management Register 2 (MMR2) Memory Management Register 3 (MMR3)                                                                  | 3-45  |

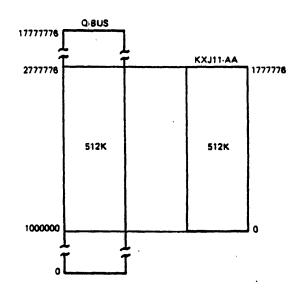

| 3.9      | SHARED MEMORY                                                                                                                            | 3-46  |

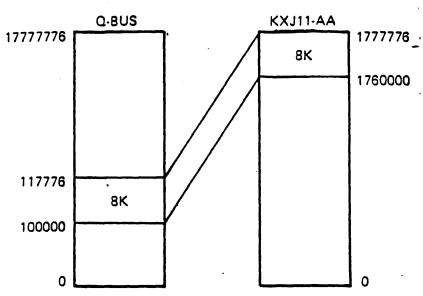

| 3.9.1    | Shared Memory Organization                                                                                                               | 3-47  |

|          | Defining One Block Of Shared Memory                                                                                                      | 3-47  |

| 3.9.2    |                                                                                                                                          | 3-48  |

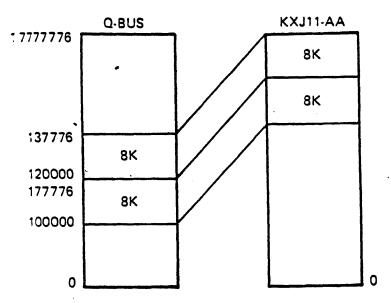

| 3.9.3    | Defining Two Blocks Of Shared Memory                                                                                                     |       |

| 3.9.4    | Defining 64 Blocks Of Shared Memory                                                                                                      | 2-20  |

|         | 3.9.6                                                                                                                                                                                                    | Enabling And Disabling Shared Memory 3-5 Shared Memory Considerations 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| CHAPTER | 4                                                                                                                                                                                                        | DMA TRANSFER CONTROLLER (DTC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

|         | 4.1                                                                                                                                                                                                      | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ì                                    |

|         | 4.2                                                                                                                                                                                                      | DTC CONSIDERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                    |

|         | 4.3                                                                                                                                                                                                      | DATA TRANSFER CONTROLLER (DTC) REGISTERS 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                                    |

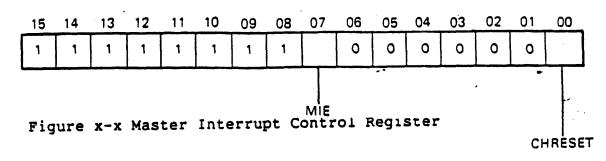

|         | 4.3.1                                                                                                                                                                                                    | DTC Global Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                    |

|         | 4.3.1.1                                                                                                                                                                                                  | Command Register 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                    |

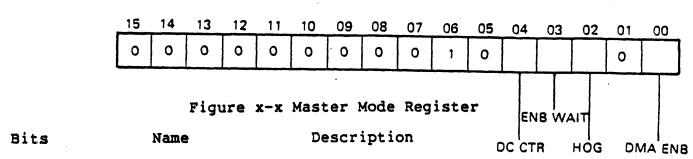

|         | 4.3.1.2                                                                                                                                                                                                  | Master Mode Register 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6                                    |

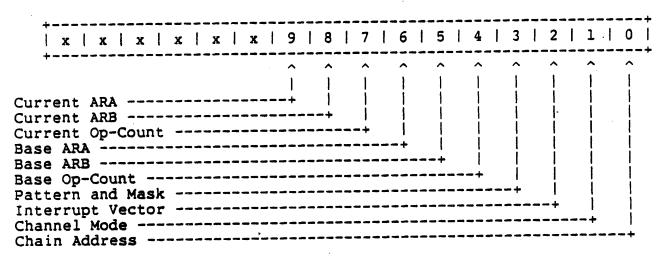

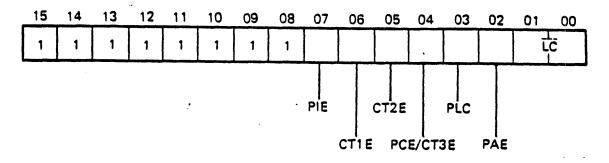

|         | 4.3.2                                                                                                                                                                                                    | DTC Channel Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                    |

|         | 4.3.2.1                                                                                                                                                                                                  | Current Address Registers A And B 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                    |

|         | 4.3.2.2                                                                                                                                                                                                  | Base Address Registers A And B 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                    |

|         | 4.3.2.3                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                    |

|         | 4.3.2.4                                                                                                                                                                                                  | Interrupt vector And Interrupt Save Register 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | O                                    |

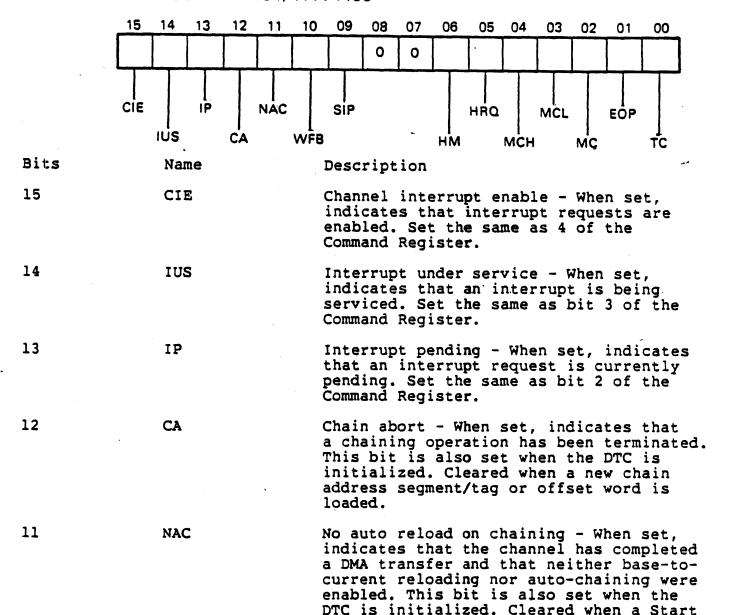

|         | 4.3.2.5                                                                                                                                                                                                  | Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                    |

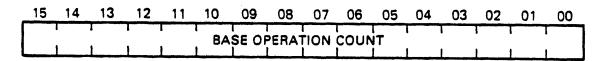

|         | 4.3.2.7                                                                                                                                                                                                  | Current And Base Operation Count Registers . 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                    |

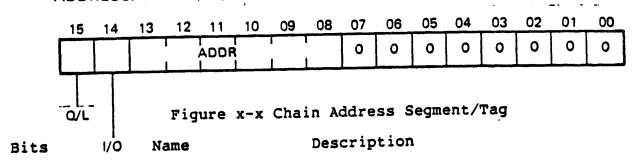

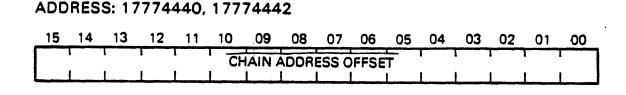

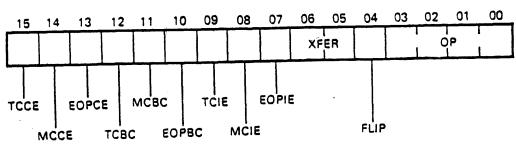

|         | 4.3.2.8                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                    |

|         |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                    |

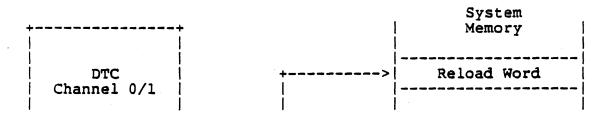

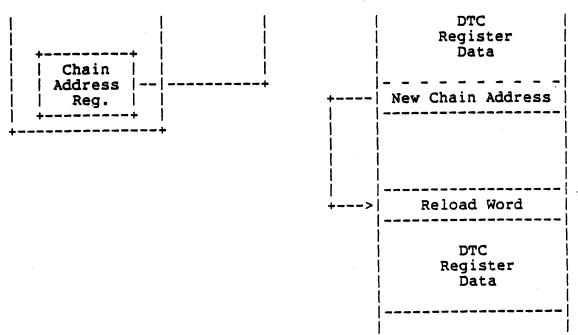

| •       | 4.4.1                                                                                                                                                                                                    | PROGRAMMING THE DTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                                    |

|         | 4 4 2                                                                                                                                                                                                    | Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                    |

|         | 4.4.3                                                                                                                                                                                                    | Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                    |

|         | 4.4.4                                                                                                                                                                                                    | Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                    |

| •       |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|         | _                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

| CHAPTER | 5                                                                                                                                                                                                        | PARALLEL I/O CONTROLLER (PIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

|         |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                    |

|         | 5.1<br>5.2                                                                                                                                                                                               | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                   |

|         | 5.1<br>5.2<br>5.2.1                                                                                                                                                                                      | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                   |