# 32-Bit Microprogrammable Products Am29C300/29300

1988 Data Book

Advanced Micro Devices

## **Advanced Micro Devices**

## Am29C300/29300 Data Book

## © 1988 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This manual neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088-3000 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

AMDASM, AmSYS, and IMOX are trademarks of Advanced Micro Devices, Incorporated.

UNIX is a trademark of Bell Laboratories.

VAX is a registered trademark of Digital Equipment Corporation.

Multibus is a registered trademark of Intel, Corporation.

IBM is a registered trademark of International Business Machines, Incorporated.

IBM-AT and IBM-PC are trademarks of International Business Machines, Incorporated.

SmartModel is a registered trademark of Logic Automation, Incorporated.

Symbolic Hardware Debugging is a trademark of Logic Automation, Incorporated.

QuickSim is a trademark of Mentor Graphics.

PAL is a registered trademark of Monolithic Memories, Incorporated.

AUTOSTEP, Meta-Disassembler, MetaStep, QuickLearn, STEP-40 SDT, and User-Defined Symbolics are trademarks of Step Engineering.

Thank you for your interest in the Am29C300/29300 family of microprogrammable products. This manual reflects our commitment to you to bring together all the essential ingredients for making your 32-bit system design as smooth and straightforward as possible.

This manual contains detailed product specifications, applications information, software support products and third-party vendors, instruction definitions, and the latest reliability information for both CMOS and bipolar technologies.

We have the quality, reliability and innovative products you need. Our worldwide hardware and software support teams of field applications engineers are ready to help you utilize our advanced microprogrammable products to complete your designs in a timely and cost-effective manner.

It is with sincere appreciation that we welcome you to the growing family of satisfied AMD customers. We look forward to serving your semiconductor needs and thank you for the opportunity to contribute to your success.

George Rigg Vice President

Processor Products Division

**Advanced Micro Devices**

## **Preface**

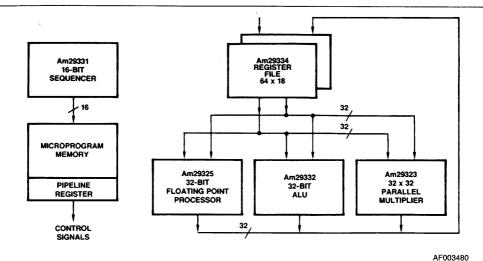

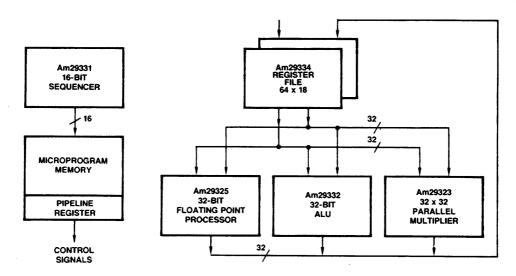

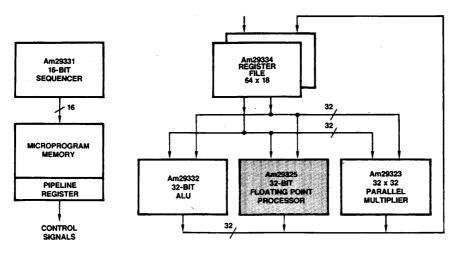

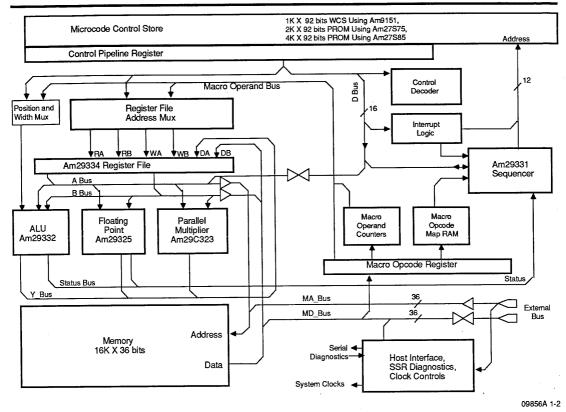

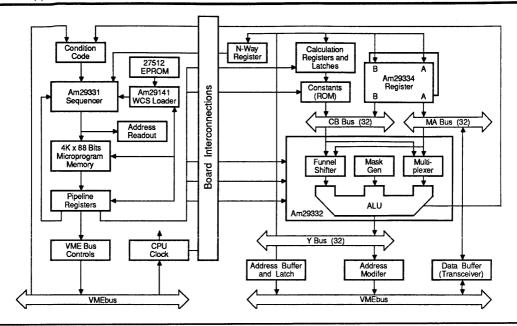

Advanced Micro Devices is recognized as the pioneer and leader in microprogrammable "bit slice" integrated circuits. The Am29300 family sets the current standard in general purpose 32-bit building blocks. Designed for high performance and flexibility with a choice of elegant, easy to implement architectures, this chip set brings microprogrammable products into the next generation.

The Am29300 generation gives the system designer flexibility both in hardware architecture and at the microprogram level. This 32-bit product family achieves high performance and high integration, while avoiding architectural restrictions. The products are designed to meet the high computational requirements of advanced graphics systems, image processing, high-end controllers, fault-tolerant processors, work stations, and other 32-bit applications limited not by process technology, but only by the designer's imagination.

Chapters 2, 3, and 4 of this databook describe the current full range of the Am29300 product offerings in bipolar and CMOS technologies. Three different types of data sheets are presented: Advanced Information, Preliminary, and Final.

- Advanced Information data sheets are developed from simulation data after circuit design is completed. After a process change, advanced information is again provided for speed select data.

- Preliminary data sheets are based on actual measurements when silicon is available and units have been tested for AC characteristics. The preliminary test programs are in place, but the normal fabrication process variations have not allowed setting of final AC limits.

- Final data-sheet status is applied to products that are fully characterized over the operating range and are in volume production.

Over 75 application notes and technical articles have been written in 11 different languages describing the features and benefits of the Am29300/29C300 family. A few representative articles are reprinted in Chapter 6 to serve as a starting point for readers less familiar with the broad scope of this chip set. A full list of articles is offered in the bibliography of Chapter 6.

Technical information regarding product and process reliability, as well as the Advanced Micro Devices model for reliability studies is provided in Chapter 7. This chapter also outlines the basic thermal characteristic data for the bipolar Am29300 products and describes test philosophy and methods.

Chapter 8 gives general information regarding package outlines and ordering information.

## **Table of Contents**

| CHAPTER 1 | Am29300/29C300 Family Overview                           |       |

|-----------|----------------------------------------------------------|-------|

|           | 1.1 Am29300/29C300 GENERAL OVERVIEW                      | 1-1   |

|           | 1.2 Am29300/29C300 FAMILY DEVICE OVERVIEW                | 1-3   |

|           | 1.3 A.C. AND D.C. PARAMETER DEFINITIONS                  | 1-17  |

| CHAPTER 2 | CMOS Family                                              |       |

|           | Am29C331 CMOS 16-Bit Microprogram Sequencer              | 2-1   |

|           | Am29C332 CMOS 32-Bit Arithmetic Logic Unit               | 2-38  |

|           | Am29C334 CMOS Four-Port Dual-Access Register File        | 2-76  |

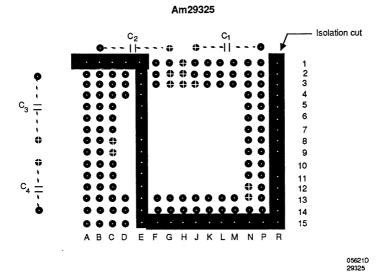

|           | Am29C325 CMOS 32-Bit Floating-Point Processor*           | 2-94  |

|           | Am29C327 CMOS Double-Precision Floating-Point Processor* | 2-95  |

| CHAPTER 3 | Bipolar Family                                           |       |

|           | Am29331 16-Bit Microprogram Sequencer                    | 3-1   |

|           | Am29332 32-Bit Arithmetic Logic Unit                     | 3-36  |

|           | Am29334 Four-Port Dual-Access Register File              | 3-74  |

|           | Am29434 ECL Four-Port, Dual-Access Register File         | 3-89  |

|           | Am29325 32-Bit Floating-Point Processor*                 | 3-103 |

|           | Am29337 16-Bit Bounds Checker                            | 3-104 |

|           | Am29338 32-Bit Byte Queue                                | 3-115 |

| CHAPTER 4 | Arithmetic Processors                                    |       |

|           | Am29C323 CMOS 32-Bit Parallel Multiplier                 | 4-1   |

|           | Am29325 32-Bit Floating-Point Processor                  | 4-24  |

|           | Am29C325 CMOS 32-Bit Floating-Point Processor            | 4-78  |

|           | Am29C327 CMOS Double-Precision Floating-Point Processor  | 4-133 |

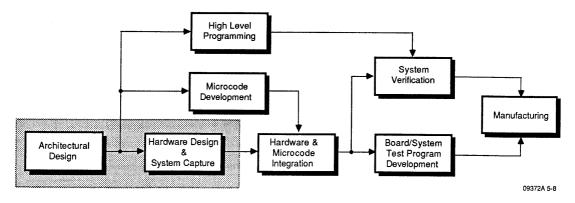

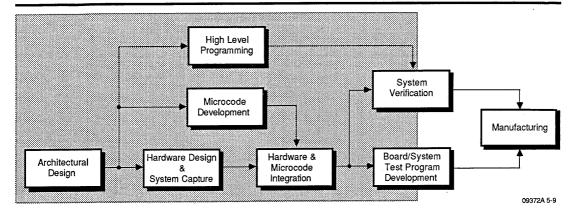

| CHAPTER 5 | Support Tools                                            |       |

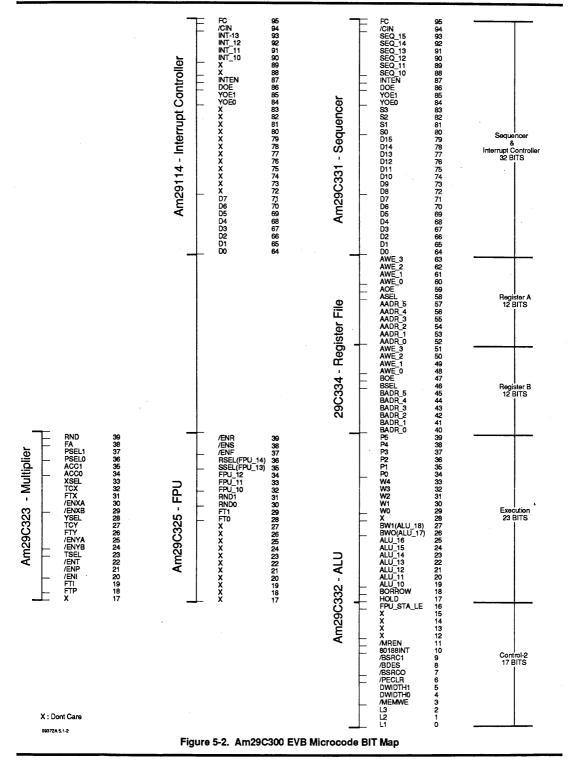

|           | 5.1 Am29C300 EVALUATION BOARD                            | 5-1   |

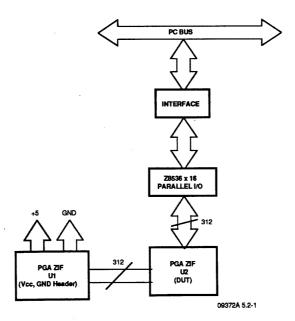

|           | 5.2 Am29300 TEST BOARD                                   | 5-4   |

|           | 5.3 Am29300 DEFINITION FILE                              | 5-7   |

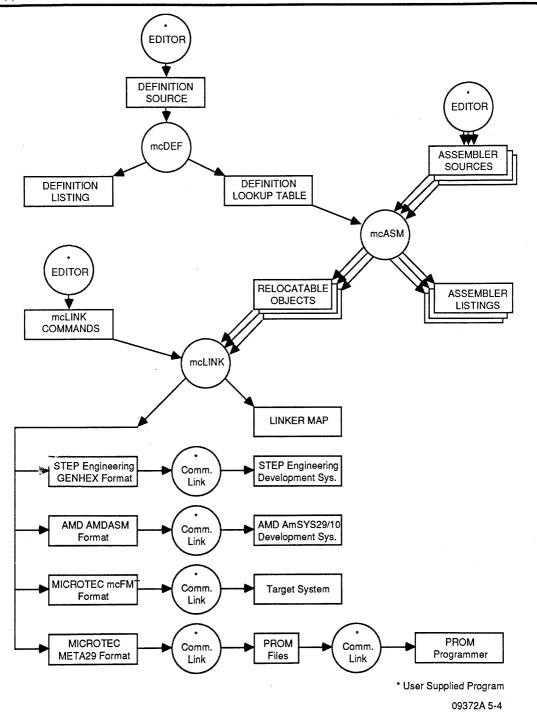

|           | 5.4 MICROCODE DEVELOPMENT                                | 5-23  |

|           | 5.4.1 Step Engineering 32-Bit Development Tools          | 5-23  |

|           | 5.4.2 Microtech mcASM Structured Microcode Assembler     | 5-31  |

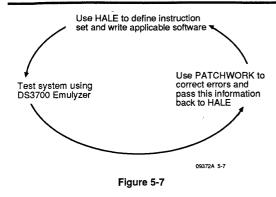

|           | 5.4.3 Hilevel Technology                                 | 5-37  |

|           | 5.4.4 Hewlett-Packard Microprogram Development Support   | 5-43  |

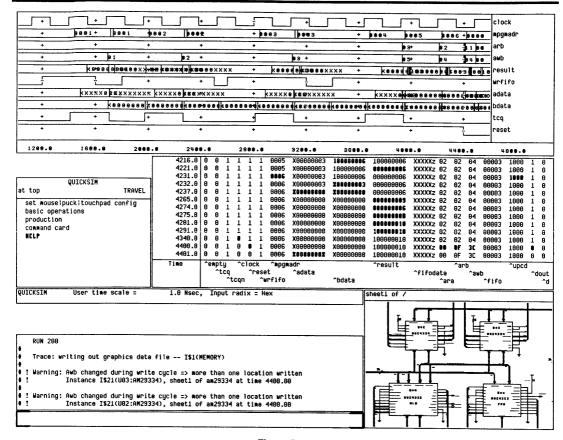

|           | 5.5 SIMULATION MODELS                                    | 5-48  |

| a service | 5.6 C COMPILER SUPPORT                                   | 5-54  |

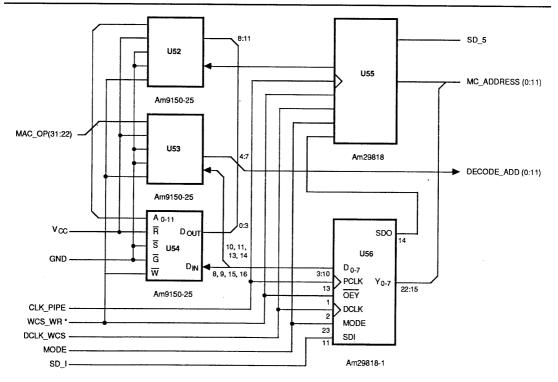

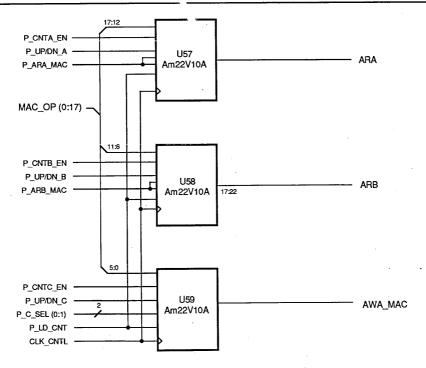

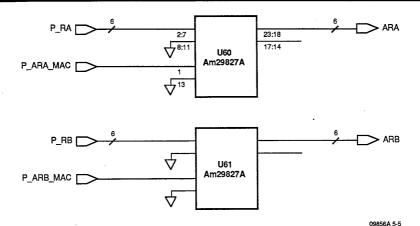

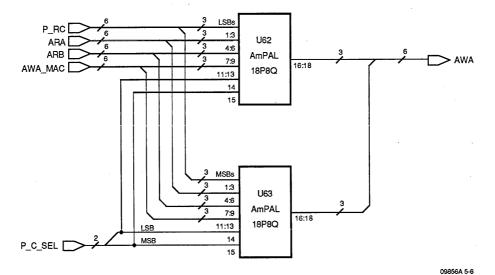

|           | 5.7 WRITABLE CONTROL STORE                               | 5-59  |

|           | 5.7.1 Agility AG-11B Microprogram Development            | 5-59  |

|           |                                                          |       |

<sup>\*</sup> Front page only of data sheet. See Chapter 4 for complete data sheet.

| CHAPTER 6 | Articles/Application Notes                                                       |       |

|-----------|----------------------------------------------------------------------------------|-------|

|           | <b>6.1</b> BIPOLAR BUILDING BLOCKS DELIVER SUPERMINI SPEED TO MICROCODED SYSTEMS | 6-1   |

| •         | 6.2 Am29300 DEMONSTRATION SYSTEM APPLICATION NOTE                                | 6-12  |

|           | 6.3 THE FAST WAY TO BUILD A RISC PROCESSOR                                       | 6-92  |

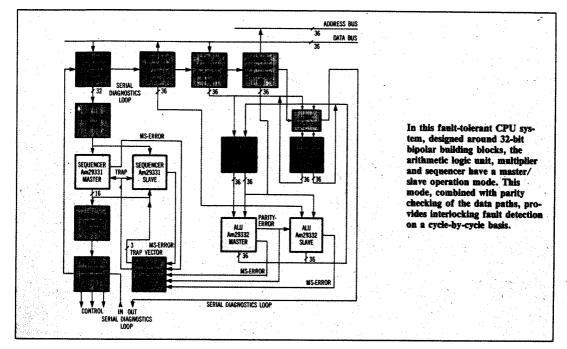

|           | 6.4 FAULT-TOLERANT CHIPS INCREASE SYSTEM RELIABILITY                             | 6-97  |

|           | <b>6.5</b> FLOATING-POINT MATH HANDLES ITERATIVE AND RECURSIVE ALGORITHMS        | 6-102 |

|           | 6.6 FLOATING-POINT ARRAY PROCESSOR IMPROVES COMPUTATIONAL POWER                  | 6-109 |

|           | <b>6.7</b> FLOATING-POINT $\mu P$ IMPLEMENTS HIGH-SPEED MATH FUNCTIONS           | 6-116 |

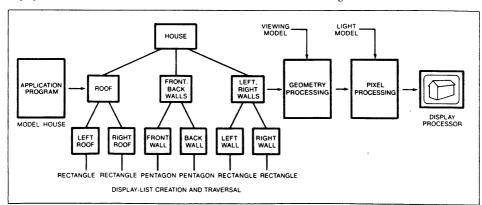

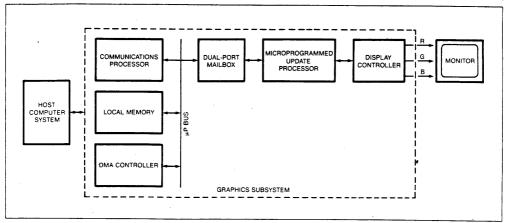

|           | 6.8 OPTIMIZE YOUR GRAPHICS SYSTEM FOR BOTH 2D AND 3D                             | 6-123 |

|           | 6.9 VARIABLE-WIDTH FIFO BUFFER SEQUENCES LARGE DATA WORDS                        | 6-136 |

|           | 6.10 DIGITAL SYSTEMS VME 29300-1                                                 | 6-141 |

|           | 6.11 BIBLIOGRAPHY                                                                | 6-144 |

| CHAPTER 7 | Technical Information                                                            |       |

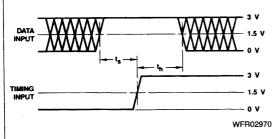

|           | 7.1 THE Am29300/29C300 TIMING ANALYSIS                                           | 7-1   |

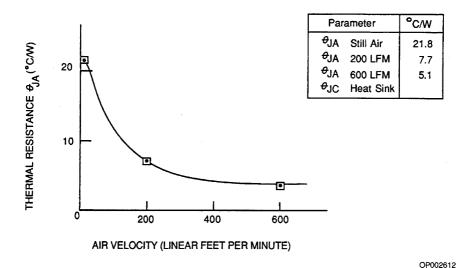

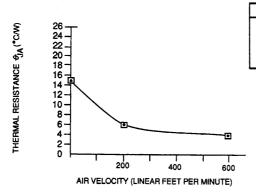

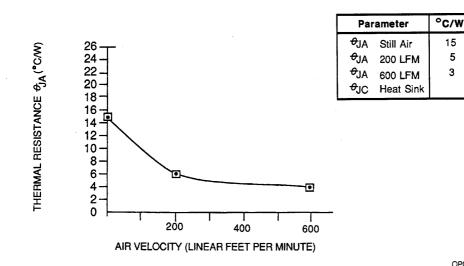

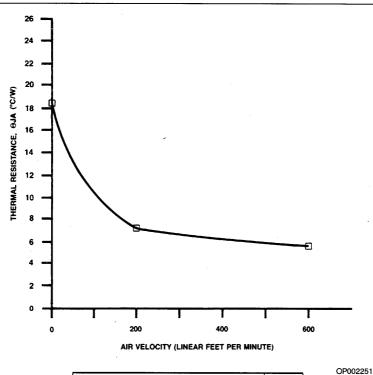

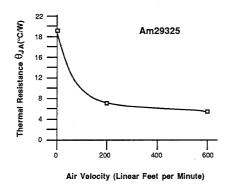

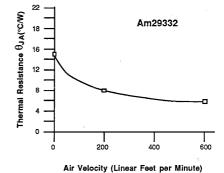

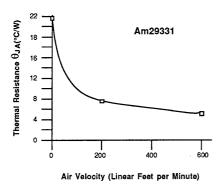

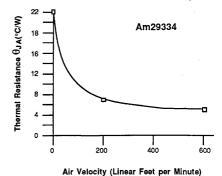

|           | 7.2 THERMAL CHARACTERISTICS/AIR FLOW                                             | 7-6   |

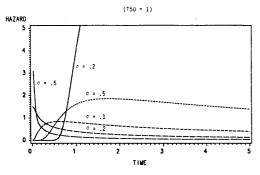

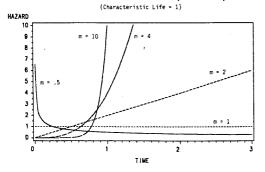

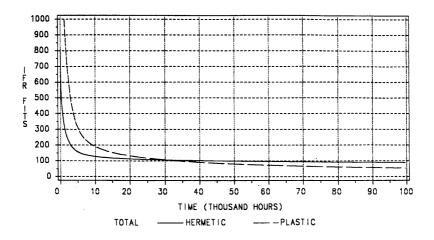

|           | 7.3 CMOS/BIPOLAR RELIABILITY                                                     | 7-10  |

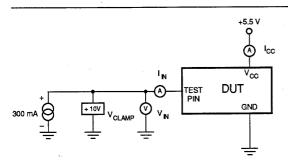

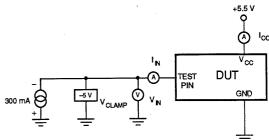

|           | 7.4 CMOS LATCH-UP TEST METHODS AND RESULTS                                       | 7-17  |

|           | 7.5 TEST PHILOSOPHY AND METHODS                                                  | 7-18  |

| CHAPTER 8 | General Information                                                              |       |

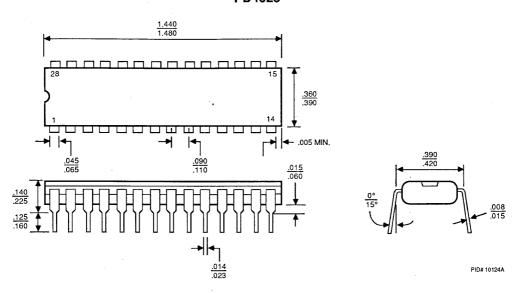

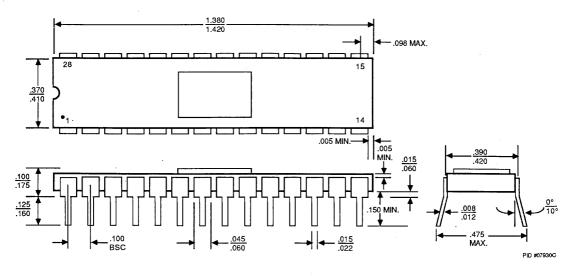

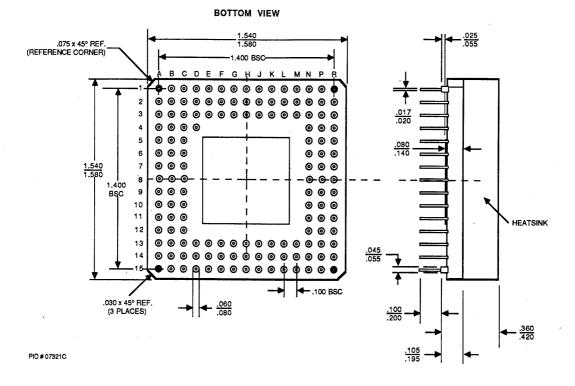

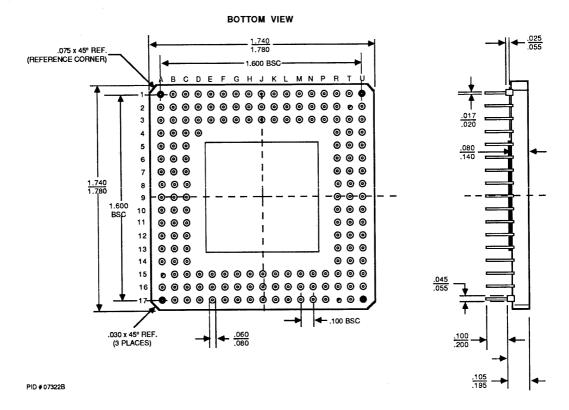

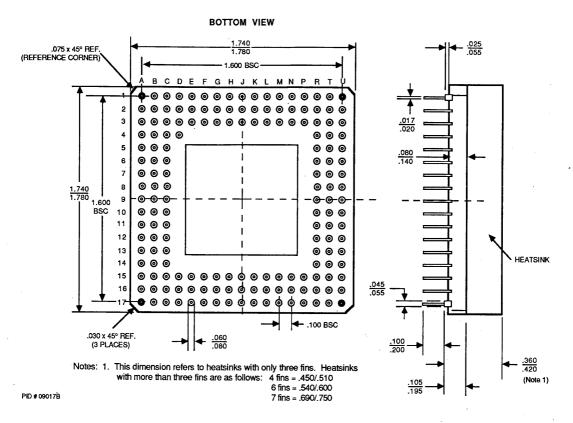

|           | 8.1 PHYSICAL DIMENSIONS                                                          | 8-1   |

|           | 8.2 ORDERING INFORMATION                                                         | 8-8   |

#### NUMERICAL DEVICE LISTING 4-1 CMOS 32-Bit Parallel Multiplier Am29C323 CMOS 32-Bit Parallel Multiplier - Speed Select 4-1 Am29C323-1 CMOS 32-Bit Parallel Multiplier - Speed Select 4-1 Am29C323-2 4-24 Am29325 32-Bit Floating-Point Processor 32-Bit Floating-Point Processor - Speed Enhancement 4-24 Am29325A 4-78 CMOS 32-Bit Floating-Point Processor Am29C325 CMOS 32-Bit Floating-Point Processor - Speed Select 4-78 Am29C325-1 4-78 CMOS 32-Bit Floating-Point Processor - Speed Select Am29C325-2 CMOS Double-Precision Floating-Point Processor 4-133 Am29C327 3-1 16-Bit Microprogram Sequencer Am29331 16-Bit Microprogram Sequencer - Speed Enhancement 3-1 Am29331A CMOS 16-Bit Microprogram Sequencer 2-1 Am29C331 CMOS 16-Bit Microprogram Sequencer - Speed Select 2-1 Am29C331-1 2-1 CMOS 16-Bit Microprogram Sequencer - Speed Select Am29C331-2 3-36 32-Bit Arithmetic Logic Unit Am29332 3-36 32-Bit Arithmetic Logic Unit - Speed Enhancement Am29332A 2-38 CMOS 32-Bit Arithmetic Logic Unit Am29C332 CMOS 32-Bit Arithmetic Logic Unit - Speed Select 2-38 Am29C332-1 CMOS 32-Bit Arithmetic Logic Unit - Speed Select 2-38 Am29C332-2 3-74 Am29334 Four-Port Dual-Access Register File 2-76 CMOS Four-Port Dual-Access Register File Am29C334 CMOS Four-Port Dual-Access Register File - Speed Select 2-76 Am29C334-1 2-76 CMOS Four-Port Dual-Access Register File - Speed Select Am29C334-2 3-104 16-Bit Bounds Checker Am29337 3-115 32-Bit Byte Queue Am29338 3-89 ECL Four-Port, Dual-Access Register File Am29434

## **CHAPTER 1**

| Am29300/29C300 Family Overview            |      |

|-------------------------------------------|------|

| 1.1 Am29300/29C300 GENERAL OVERVIEW       | 1-1  |

| 1.2 Am29300/29C300 FAMILY DEVICE OVERVIEW | 1-3  |

| 1.3 A.C. AND D.C PARAMETER DEFINITIONS    | 1-17 |

## **CHAPTER 1**

## Am29300/29C300 Family Overview

## 1.1 Am29300/29C300 GENERAL OVERVIEW

## CMOS and Bipolar 32-Bit High Performance Building Blocks

AMD's Am29300/29C300 family has been developed to provide systems designers with flexible, off-the-shelf, high-performance, 32-bit microprogrammable building blocks. The Am29300/29C300 family is ideal for complex and calculation-intensive applications such as intelligent peripheral controllers including graphics, telecommunications, switching systems and laser printers; artificial intelligence and RISC CPUs; array and digital signal processing; and a multitude of military applications.

## Am29300/29C300 Pushes the Limits of Your Imagination

## Flexibility of Design

Success is driven by innovation and differentiation. While "me too" systems companies merely struggle to be the lowest cost manufacturers, innovative companies strive ahead toward the future. The designers of AMD's 32-bit family recognize the need for system innovation and differentiation. The Am29300/29C300 family provides powerful building blocks with unlimited architectural flexibility, thus returning design innovation and value-added back to the design engineer. With the flexibility of custom architectures and custom microcode, system performance is limited only by imagination.

## Improve Your Time to Market

Because AMD's 32-bit family integrates high performance features such as master/slave, parity checking,

funnel shifters, priority encoders, and mask generators, the Am29300/29C300 family meets the complex functional requirements of sophisticated systems and can eliminate the need for custom ICs. With the Am29300/29C300 there are no engineering circuit turnaround delays, no hidden Non-Recurring-Engineering costs, no complex test engineering correlations, and no waiting. Off-the-shelf availability of a highly integrated, fully tested product of guaranteed quality can mean improved profits for the system application.

## Specifications that Count

We provide you with the tools and data necessary to make your design right the first time. You can be assured that the specifications of the parts you order are guaranteed by AMD as printed in the data sheets. Designers require worst case guaranteed parameter values, and AMD provides them. AMD removes the uncertainty of customized design with fully guaranteed, standard, off-the-shelf, 32-bit products. These state-of-the-art bipolar and CMOS building blocks are the ideal solution for 32-bit applications.

## Military Product Position

AMD is committed to support the industry with military qualified and specified Am29C300 family products. The entire family is being offered as 883C level B fully compliant APL products. In addition, we plan to release the family in DESC military drawings. This will provide the user with alternatives to source control drawings, thus saving cost and time.

## Manufacturing - Processes and Planning

## AMD's Commitment to Process Technology Improvements

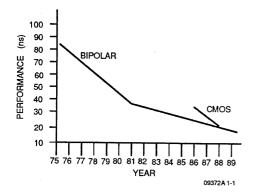

The Am2901 industry standard bit-slice ALU is an ideal example of AMD's commitment to process improvements. Table 1-1 and Figure 1-1 demonstrate the per-

formance improvements of the Am2901. Since its introduction, the Am2901's performance has increased nearly three-fold while its price has dropped by a factor of ten. This represents **25 percent** annual price/performance improvement over **12 years.** The philosophy of performance improvements through process technologies applies to all members of AMD's microprogrammable products.

Table 1-1

|      |           |                                      |                       | Speed                                   |       |

|------|-----------|--------------------------------------|-----------------------|-----------------------------------------|-------|

| Year | Device    | Technology                           | Die Size              | $\textbf{A,B} \rightarrow \textbf{G,P}$ | Power |

| 1975 | Am2901    | Low-Power Schottky                   | 33 K mil <sup>2</sup> | 80 ns                                   | 1.5 W |

| 1977 | Am2901A   | Dual Layer Metal<br>Ion Implantation | 20 K mil <sup>2</sup> | 65 ns                                   | 1.5 W |

| 1978 | Am2901B   | Projection Printing                  | 15 K mil <sup>2</sup> | 50 ns                                   | 1.5 W |

| 1981 | Am2901C   | ECL Internal<br>TTL, I/O IMOX        | 15 K mil²             | 37 ns                                   | 1.5 W |

| 1986 | Am29C01   | 1.6 µm CMOS                          | 15 K mil <sup>2</sup> | 37 ns                                   | 0.5 W |

| 1987 | Am29C01-1 | 1.2 µm CMOS<br>Speed Select          | 15 K mil²             | 28 ns                                   | 0.5 W |

| 1987 | Am29C01-2 | 1.0 μm CMOS                          | 15 K mil²             | 19 ns<br>(est)                          | 0.5 W |

Figure 1-1. Am2901 Performance

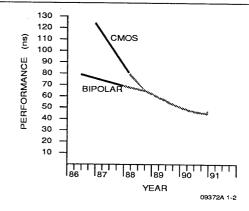

Figure 1-2. Am29300/29C300 Performance

## Bipolar VLSI

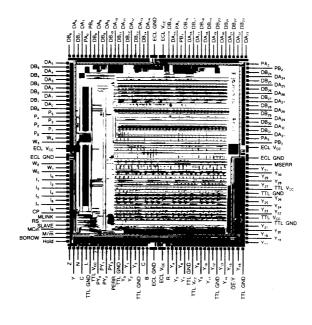

The Am29300 family contains some of the largest bipolar ICs produced anywhere in the world. For example, the Am29332 has over 5,000 gates, 31,000 devices, and measures 142,000 mils². AMD's IMOX S-2 process allows for such integration and high performance. Future advances in AMD's bipolar process will include process "tweaks" as well as total changes in process approach. These advances will provide improved performance and yields, directly affecting the price/performance of the Am29300 family.

#### CMOS VLSI

The Am29C300 family, like its bipolar counterpart, also contains very large die. The Am29C325 encompasses nearly 11,000 gates and measures almost 130,000 mils<sup>2</sup>.

AMD's CS-11 is the current CMOS workhorse process for the Am29C300 family. At an effective channel width of 1.6 microns, CS-11 is capable of approaching the bipolar speeds on all specifications.

There will be continued process improvements to the current CMOS technology. The first improvement, CS-11A, will be available on all Am29C300 products in Q4 1987. CS-11A has an effective channel width of 1.2 microns, resulting in a 25 percent performance improvement over CS-11.

Table 1-2 demonstrates the performance improvements expected on the Am29C300 family as these processes are incorporated into the family.

**Table 1-2 CMOS Evolution**

| - | Year | Process | Effective<br>Channel Length | Typical<br>Gate Delay |

|---|------|---------|-----------------------------|-----------------------|

|   | 1986 | CS-11   | 1.6 micron                  | 1.25 ns               |

|   | 1987 | CS-11A  | 1.2 micron                  | 0.90 ns               |

|   | 1988 | CS-21   | 1.0 micron                  | 0.65 ns               |

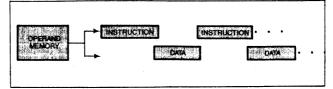

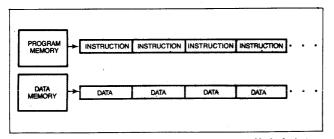

## The Philosophy Behind the Functionality

When AMD introduced the 4-bit slice (memory plus ALU) Am2901 in 1975, semiconductor and packaging technologies prevented the integration of a 16- or 32-bit unit. The 4-bit slice with internal memory and external carry-

look-ahead and a 48-pin package were the right compromise then. Today, semiconductor and packaging technologies have advanced to a point where a full 32-bit ALU with many non-sliceable features, internal carry-lookahead, and systems access to all buses can be put on one chip, with expandable memory on another. This results in higher versatility and higher performance.

There are several reasons for the choice of a wider data path. First, cycle time is improved significantly if carry lookahead is contained entirely on the chip. Second, certain powerful on-chip functions, such as the funnel shifter, priority encoder, and mask generator are extremely difficult to "slice." Third, a higher level of integration leads to a more cost-effective system solution. These and other advantages contributed to the decision to make the Am29332/29C332 a complete 32-bit function rather than a slice.

The Am29300/29C300 philosophy has also removed the register file from the ALU, providing the designer greater system flexibility and making expansion and regular addressing much easier. The new partitioning results in a number of benefits. The user gets a functionally more powerful processor with two uncommitted input buses and gains the flexibility of adding storage elements to those buses. The Am29300/29C300 family is designed to be the most functional and powerful family of microprogrammable building block products available on the market.

## 1.2 Am29300/29C300 FAMILY DEVICE OVERVIEW

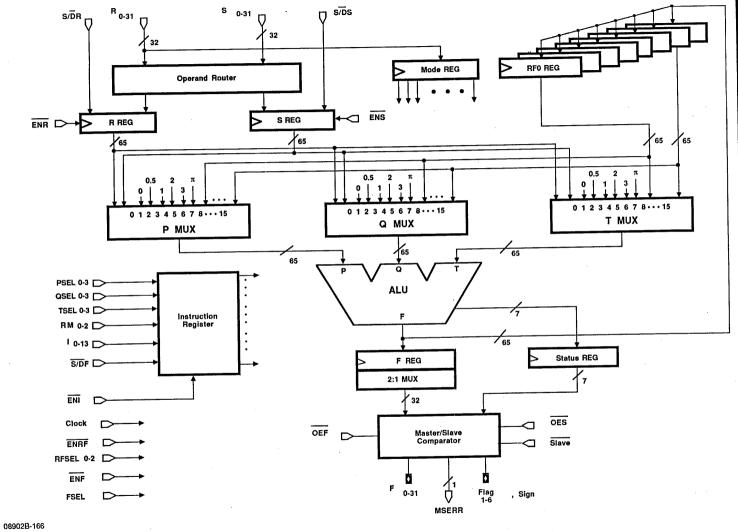

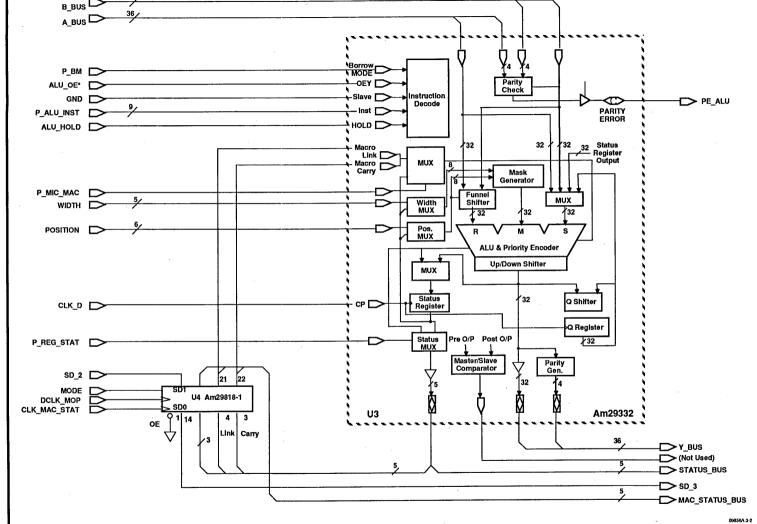

## The Am29332/29C332 32-Bit ALU – The Heart of a New Generation of Machines

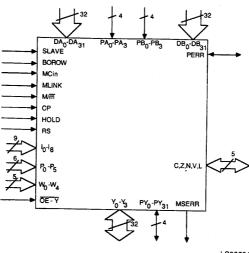

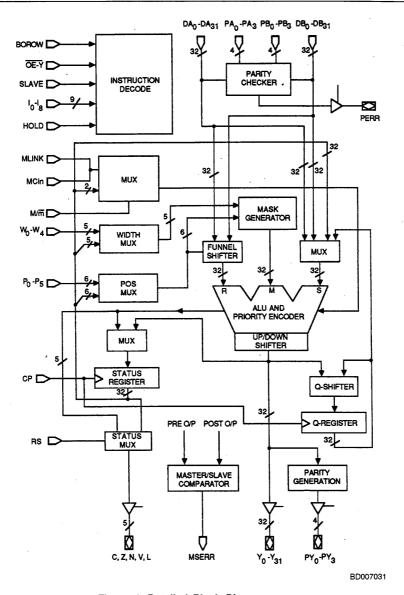

The Am29332/29C332 is AMD's first 32 bit wide ALU. Parallel processing of 32 bits of data, coupled with very fast cycle time, provides throughput unprecedented in VLSI-based systems.

The 32-bit ALU combines maximum performance and integration by keeping all critical timing paths short and balanced. All ALU instructions have the same short cycle time. This includes barrel shifting, normalization, priority encoding and field logical operations.

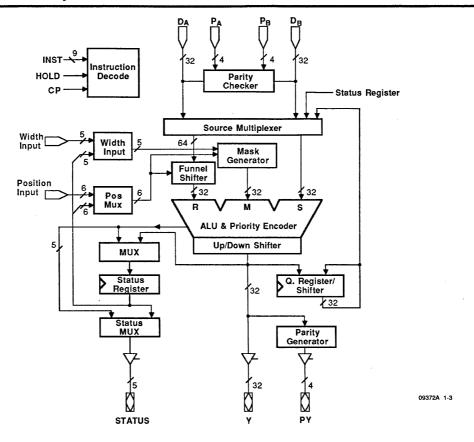

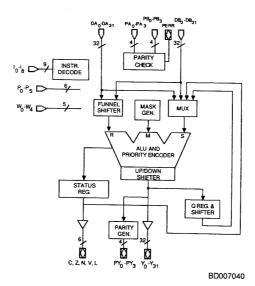

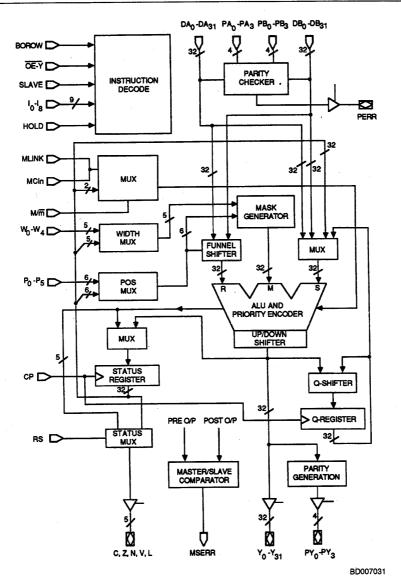

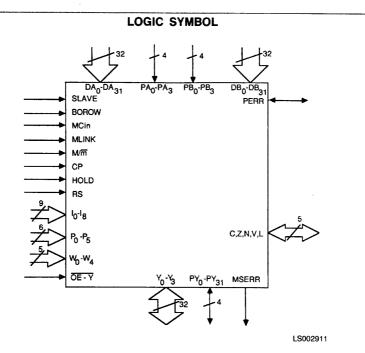

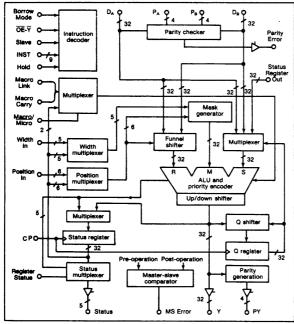

Figure 1-3. Am29332/29C332 32-Bit ALU

## Three Ports Facilitate High Throughput

The Am29332/29C332 has two input ports (A and B) and an output port (Y), all 32 bits wide. These three ports provide flexibility and accessibility for high-performance processor designs. Dedicated input and output ports provide a flow-through architecture and avoid the penalty associated with switching a bidirectional bus halfway through the cycle. In addition, the three-bus architecture allows easy parallel connection of other arithmetic units for even higher performance.

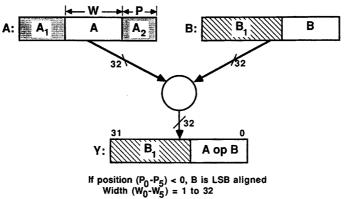

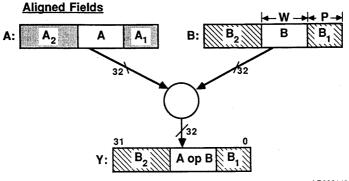

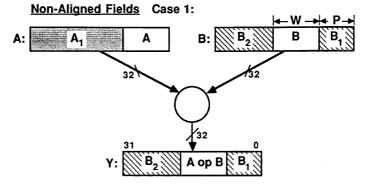

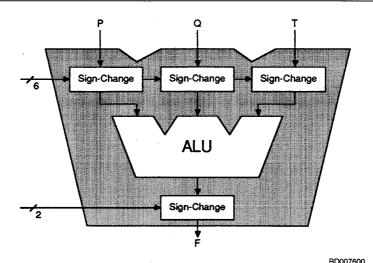

### Arithmetic and Logic Unit

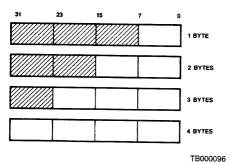

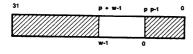

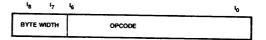

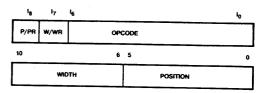

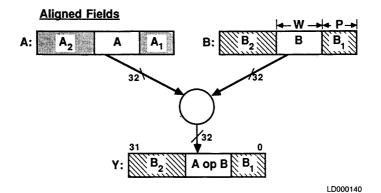

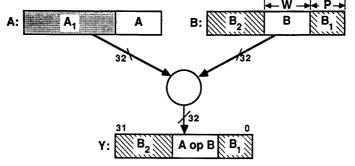

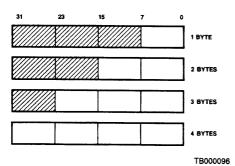

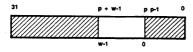

The 32-bit wide ALU in the Am29332/29C332 has full carry-lookahead to improve cycle time for all arithmetic operations. The ALU is a unique three-input structure with two data input ports and a mask input that is used on every cycle, thus providing very powerful instructions

that execute in a single cycle. The mask supports bytealigned arithmetic operations and field logical operations on variable-position, variable-length fields. The bytealigned arithmetic operations use 8-, 16-, 24-, and 32-bit LSB-aligned operands. Field-logical instructions operate on operands of arbitrary length and starting position.

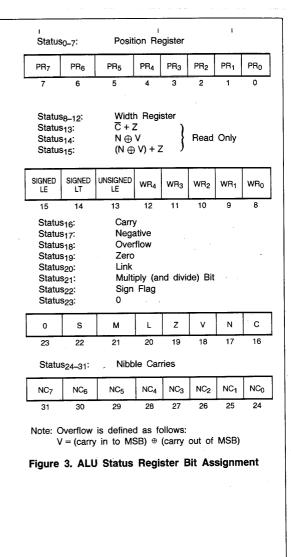

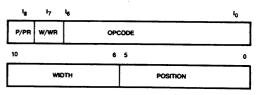

## Priority Encoder

The priority encoder generates a 5-bit vector indicating the highest order 'one' in the 32-bit operand. These 5 bits are then stored in the position field of the status register for use during the next cycle. The priority encoder supports all byte-aligned data types; the result is dependent upon the byte width specified. This function supports normalization necessary for floating point operations; it also enhances certain graphics primitives.

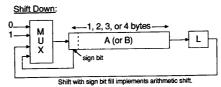

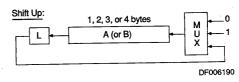

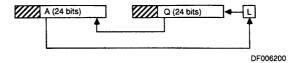

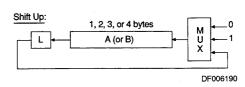

## 64-Bit Funnel Shifter

The on-board 64-bit input, 32-bit output funnel shifter is much more than a conventional barrel shifter. The shifter can extract any contiguous field of 32 bits from a 64-bit input. This input may consist of concatenated A and B input words or, for barrel shifting, duplicated A or B input words.

Residing in the ALU data path, the shifter can perform nbit shift or rotate in conjunction with a logical ALU operation—all in the same cycle, without increasing the length of the cycle. This capability affords single-cycle execution of logical operations beween unaligned fields — a function that would take multiple cycles in other architectures.

## Mask Generator

The power and flexibility of the processor stems partly from its ability to generate a mask to control the width of an operation for each instruction without any cycle time penalty. The mask generator at the ALU input creates a contiguous field of ones and contains its own shifter to position this control field anywhere in the data path. The mask generator can also be used as a pattern generator, bypassing the mask through the ALU.

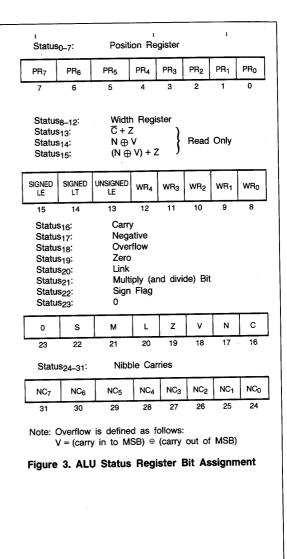

## Status Register

The processor has a 32-bit wide status register that contains: information on position and width of the operand; the ALU status flags Carry, Negative, Overflow, and Zero; status bits for evaluation of inequalities; a link bit for multiprecision shifts; an M flag for high speed multiply and divide; and intermediate nibble carries for BCD arithmetic. An extract-status instruction is provided that allows any bit from the status register to be output at the Y-port. This is particularly useful in machines employing stack architectures. Instructions to save and restore the status register are also provided.

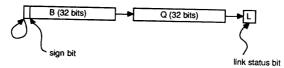

## Multiply and Divide Support

The chip incorporates dedicated hardware to allow efficient implementation of multiply and divide algorithms for

both unsigned and signed arithmetic data types. The modified Booth multiply algorithm processes **two bits per cycle**. The four-quadrant, non-restoring divide algorithm processes one bit per cycle. Since the data path width is fixed at 32 bits, the instructions can be simplified to provide "first step," "iterate step" and "last step" commands for both multiply and divide. Programming slices is no longer necessary since all multiply and divide steps are provided in the instruction set. For business-oriented machines, the ALU is capable of performing BCD arithmetic on packed BCD numbers. In order to keep non-BCD operations fast, BCD arithmetic is executed by binary arithmetic followed by BCD correction.

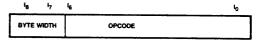

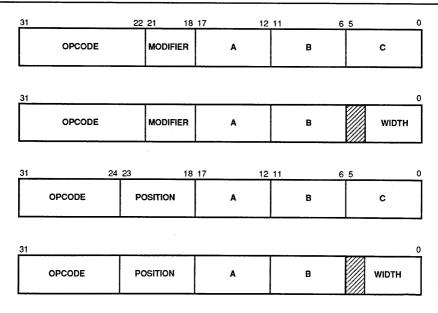

## The Instruction Set: Powerful and Flexible Yet Simple and Regular

The Am29332/29C332 instruction set complements the powerful hardware. To ease the task of code generation, the instruction set is symmetrical and regular. There are two large classes of instructions. The first class handles byte-aligned data (8-, 16-, 24-, or 32-bit LSB-aligned). It is comprised of: data movement instructions; arithmetic instructions, including multiply and divide steps and BCD instructions; logical instructions; and single-bit shift and prioritize operations. The second class of instructions operates on variable-length, variable-position fields. It includes N-bit shift and rotate, field extract, and field logical operations.

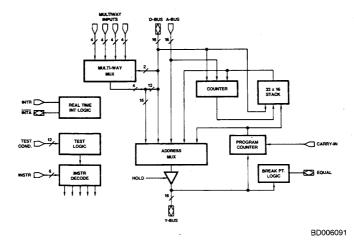

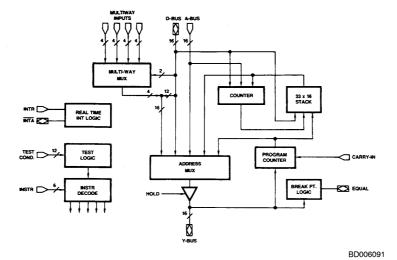

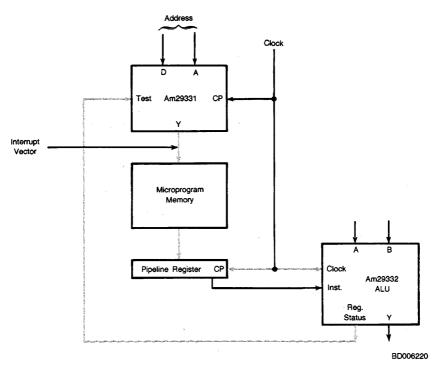

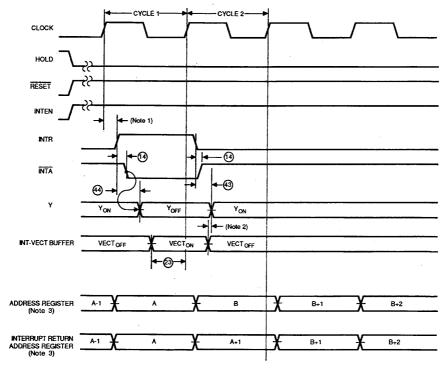

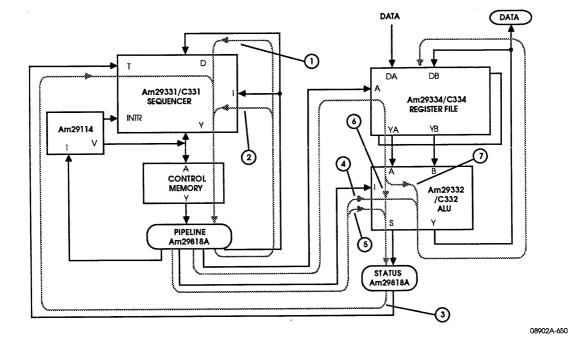

## The Am29331/29C331 – 16-Bit Micro-Interruptible Sequencer

The Am29331/29C331 is a high speed sequencer controlling the sequence of microinstructions stored in microprogram memory. The instruction set aids structured microprogramming and handles sequential execution, branches, subroutines and loops. The sequencer instructions may be unconditional or conditional based on CPU status, an on-board 8-input test multiplexer, and a polarity control. The sequencer has a 16-bit wide address path and can thus access 64K words of microcode memory. It is transparently interruptible at any microinstruction boundary.

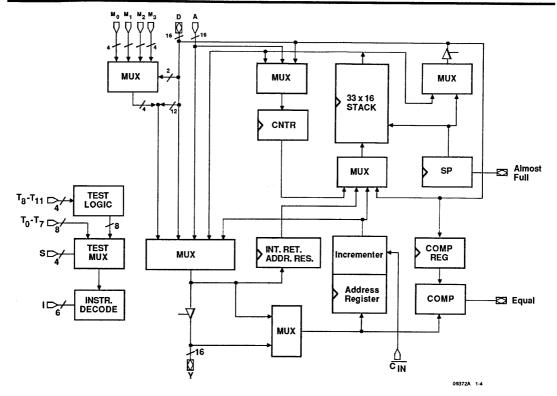

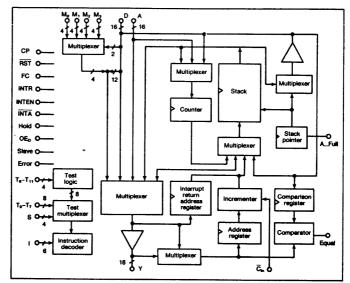

Figure 1-4. Am29331/29C331 16-Bit Microinterruptible Sequencer

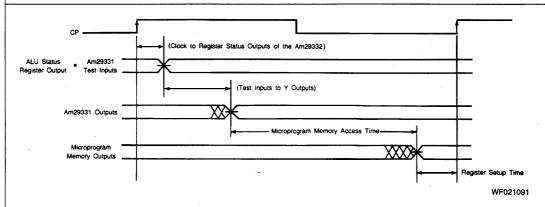

## Balanced Timing Means Greater Throughput

In previous generation microprogrammed systems, the control path containing the sequencer has often been the bottleneck, because the sequencers were slower than the associated data paths. Not so in the Am29300/29C300 family. The speed of the Am29331/29C331 sequencer has been designed such that the entire system timing is balanced between the control path and data path, leading to higher overall throughput.

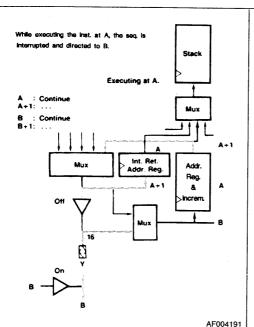

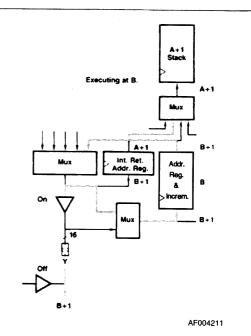

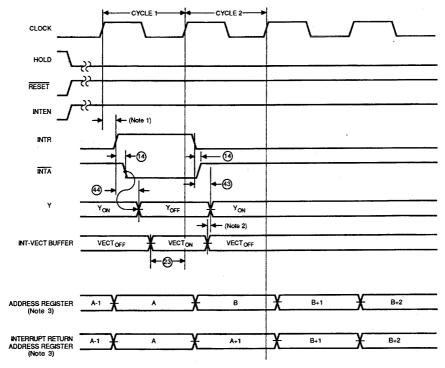

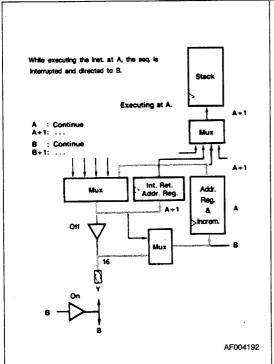

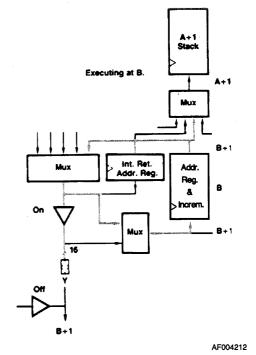

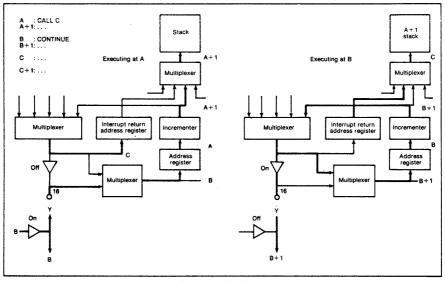

## Micro-Level Interruptible

Real time interrupt handling at the microinstruction level is made possible by the interrupt return address register and the bidirectional Y-port. While the interrupt address enters the part through the Y-port, the interrupt return address is saved on the stack. Nested interrupts are handled the same way.

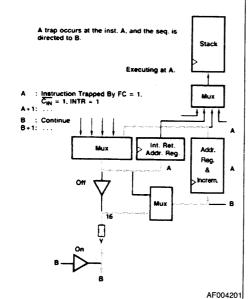

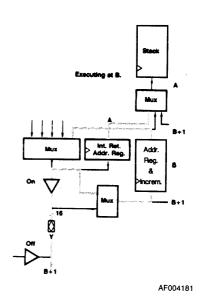

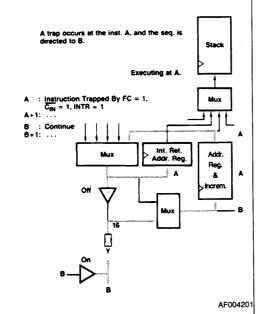

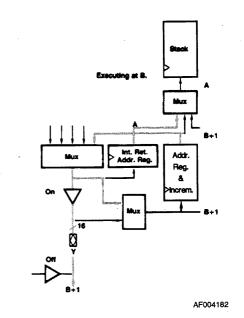

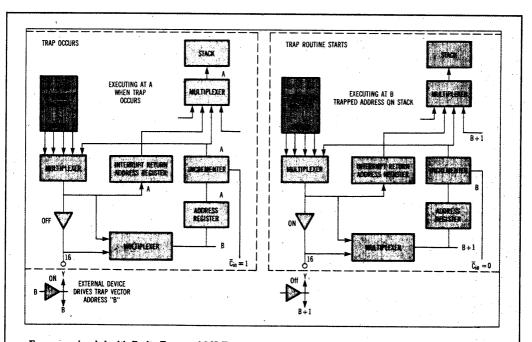

## Built-in Trap Handling

As an architectural alternative to the interrupt-driven approach, the Am29331/29C331 Sequencer also has provision for handling "traps" transparently at the microinstruction level, upon the occurrence of specified system events. In this mode, the current microinstruction is aborted. The specified trap routine is executed (like an interrupt). But, following the trap routine, the aborted microinstruction is re-executed (instead of proceeding on to the next microinstruction, as in an interrupt).

#### 33-Level Stack

The 33-level stack provides sufficient depth to handle nested loops and subroutines; it is also used to save the status of the sequencer when handling interrupts. Since the stack is externally accessible, its contents may be unloaded through the bidirectional D-port for diagnostic, debugging or fault recovery purposes. The stack may also be loaded from the outside through the D-port. This may be used for context switching, for example.

## Multitasking Support

By providing a HOLD control pin, the designer may use multiple sequencers in a multitasking system, with only one sequencer active at any one time. The output Y-ports of the sequencers are tied together to address the same microcode memory. This is useful, for example, for rapid context switching at the microinstruction level.

## Address Comparator Eases Debugging

The sequencer compares the address on the Y-port with the contents of an internal break-point register. Breakpoint detection is useful for debugging the system or gathering run-time statistics.

## Two-Branch Address Inputs

Two separate branch address inputs, D and A, are provided to speed up source address selection. Both A and D ports can be used to load the counter. The D port can also be used to load or unload the stack while the A port may be used to input a branch or map address, eliminating the need to three-state selected sources.

## Built-in Test Generation Logic

In the Am29331/29C331, unlike previous sequencers, test generation logic and one layer of condition test multiplexer logic are built-in. This not only reduces component count, but also improves cycle time by minimizing inter-chip delays and by moving the multiplexer into fast internal ECL gates.

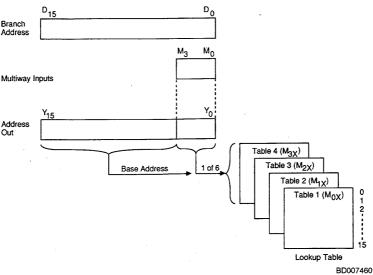

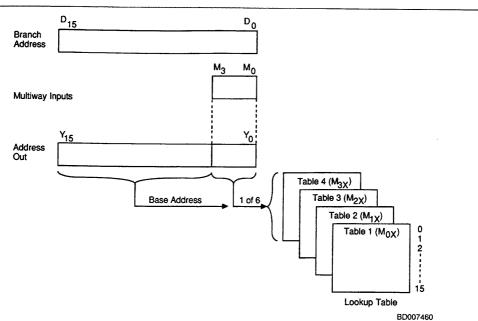

## Multiway

Four sets of four-bit multiway inputs are provided. Each such set of 4 bits can replace the four least significant bits of D input, allowing a direct branch to any of 16 consecutive locations in the microprogram memory. The multiway capability allows checking of up to four simultaneous test conditions in a single cycle. This is obviously an attractive alternative to checking each test condition serially, a much slower multicycle process.

## The Most Versatile Sequencer Ever

The combination of 16 bits of address, real time interrupt capability, two address ports, a deep stack and other

capabilities make this device the most feature-loaded sequencer ever offered.

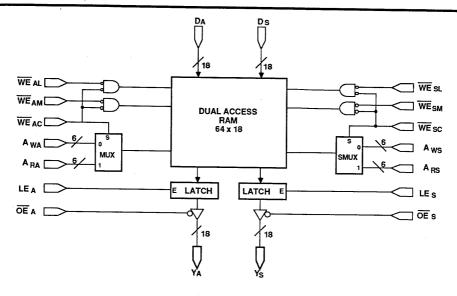

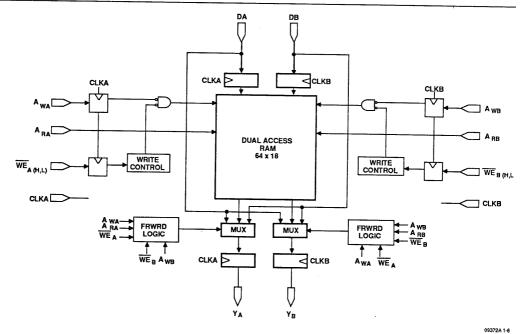

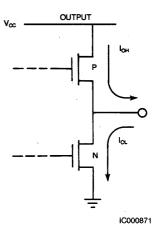

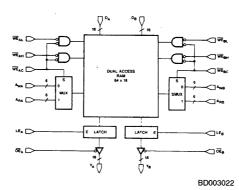

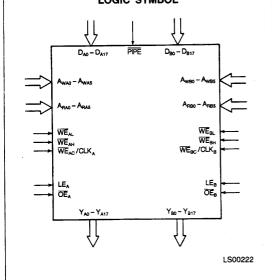

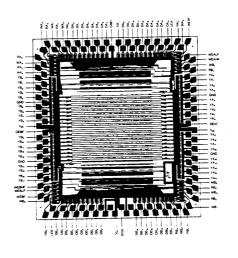

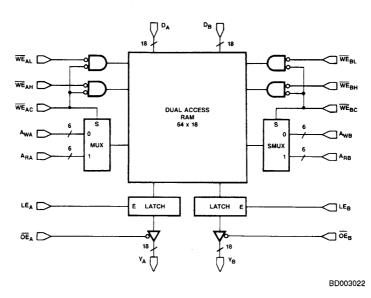

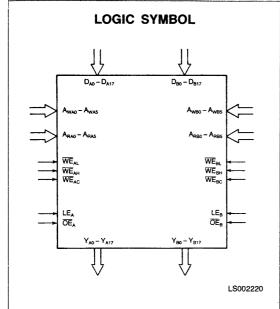

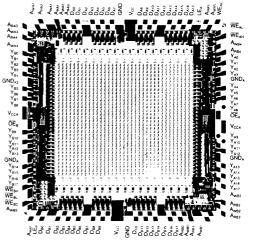

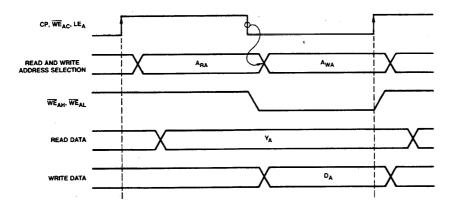

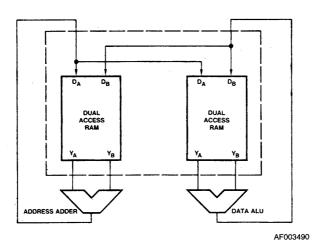

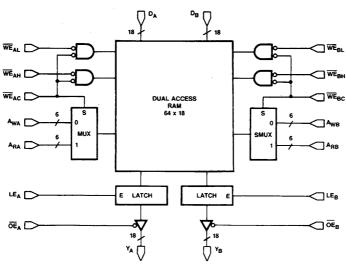

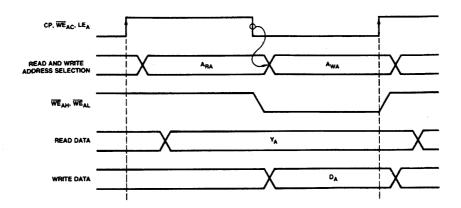

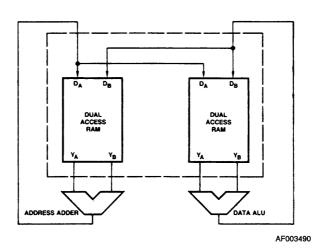

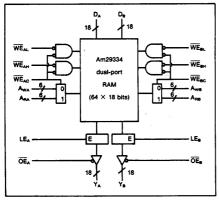

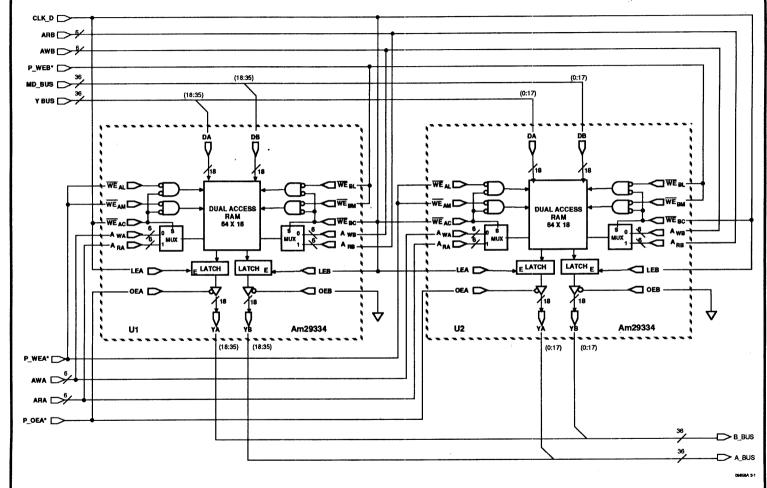

## The Am29334/29C334 Register File

The Am29334/29C334 is a 64 word by 18 bit, dual-access, four-port register file. It is deliberately separate from the ALU to allow easy, regular expansion, both horizontally for wide data paths and vertically for large register file machines.

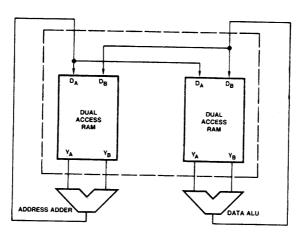

### Four-Port Achitecture

Two Read and two Write data ports allow independent and simultaneous access to two register file locations. The Read and Write ports are separated to eliminate the delay caused by turn-around of bidirectional buses. The dual-address, four-port architecture allows any combination of two reads, writes, or read-writes – no restrictions.

## Organization Supports Parity

Since the Am29334/29C334 has a by-18 organization, it can store two bytes with parity in each of its 64 words. As a data path storage element, the register file neither generates nor checks parity. When used in conjunction with the Am29332/29C332 processor (which provides parity checking on its inputs and parity generation on its output), it provides a bus compatible register file, thus extending parity protection to the entire data path loop.

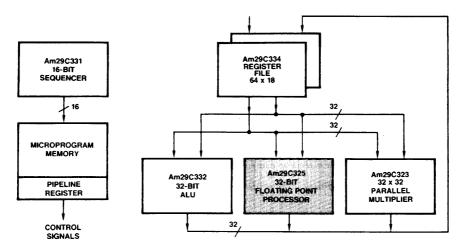

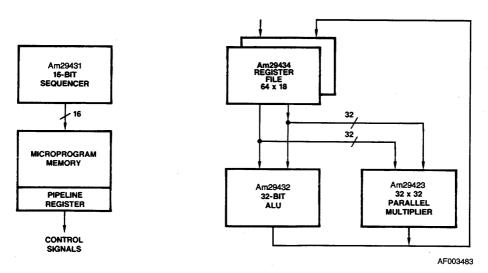

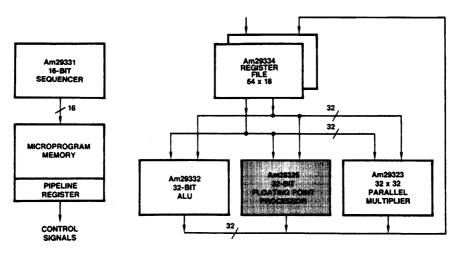

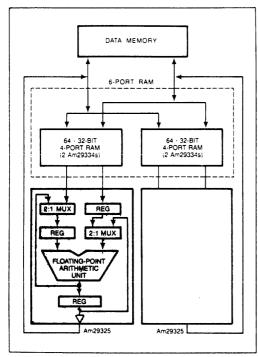

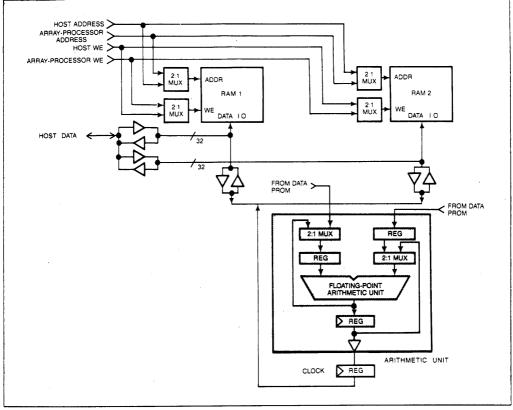

## Array Processing Products/Arithmetic Accelerators

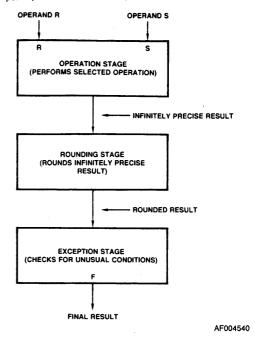

The Am29300/29C300 family is capable of very fast operation on 32-bit fixed-point numbers. When greater dynamic range is necessary, floating-point numbers are often chosen. Advanced Micro Devices offers highspeed VLSI integrated circuits designed to support the growing need for high-performance array and signal processing. Applications include graphics, image processing, communications, medical instrumentation, radar and other electronic warfare applications. Three AMD devices address these needs: Am29325/29C325 32-bit Floating-Point Processor, Am29C323 32x32-bit Multiprecision Multiplier, and Am29C327 64-bit Floating-Point Processor. These devices achieve very high speeds through a combination of innovative architecture and AMD's advanced bipolar IMOX process and CMOS process.

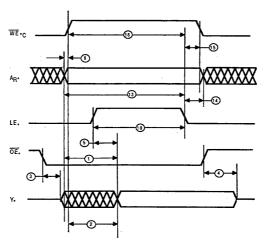

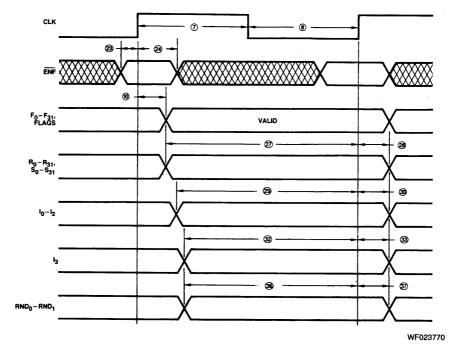

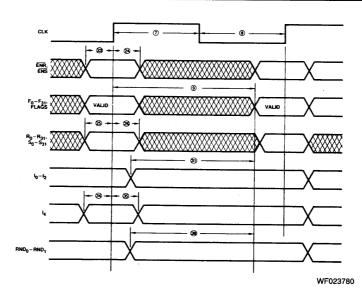

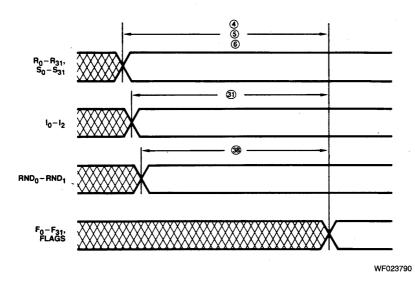

Figure 1-5. Am29334/29C334 Non-Pipelined Mode

09372A 1-5

Figure 1-6. Am29334/29C334 Pipelined Mode

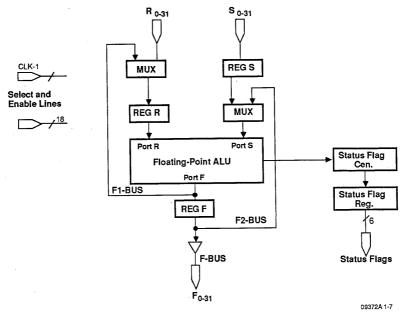

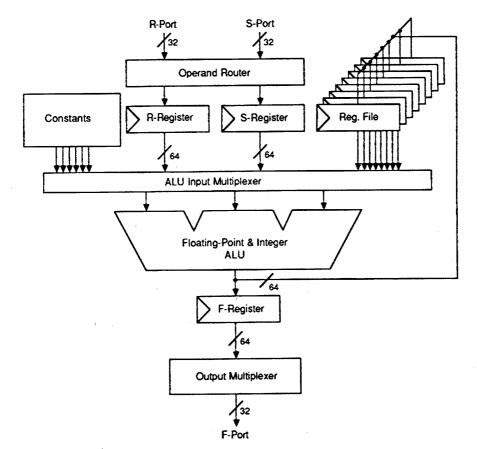

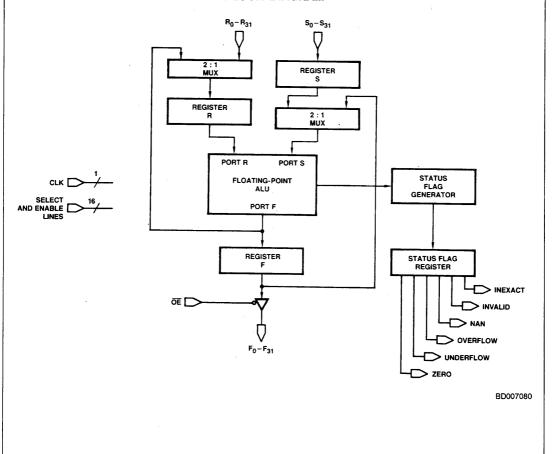

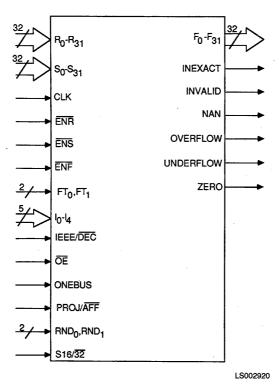

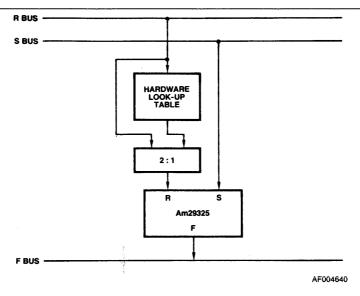

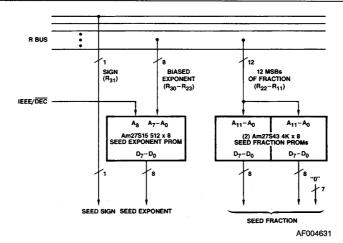

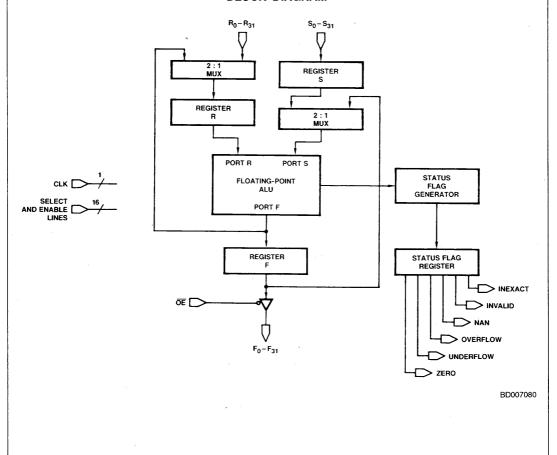

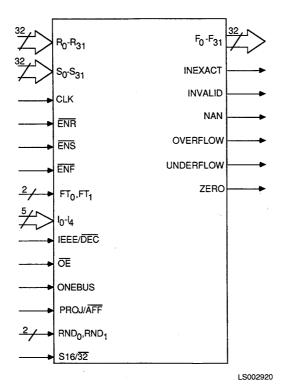

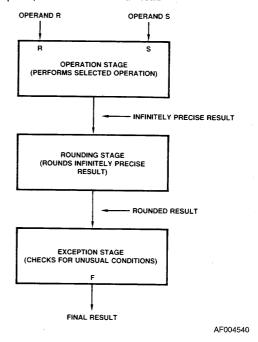

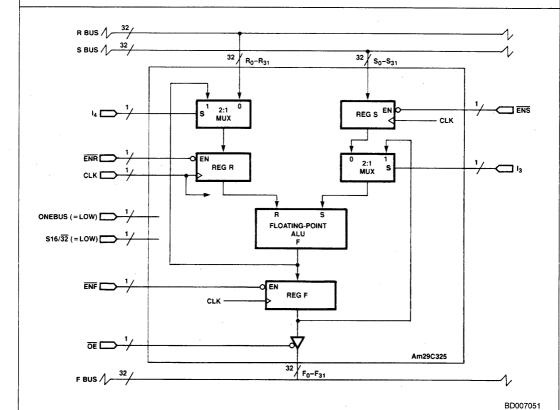

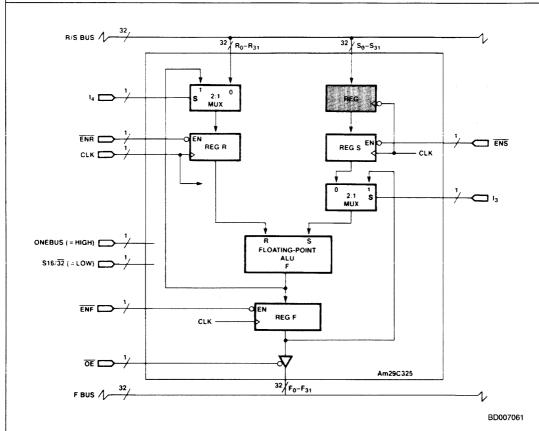

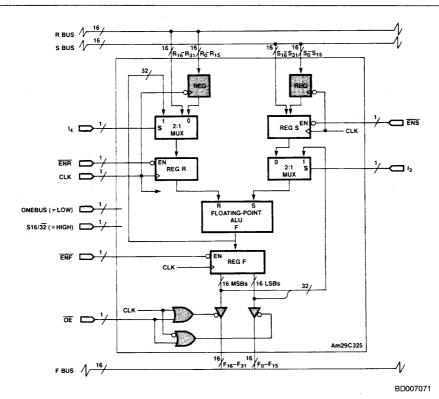

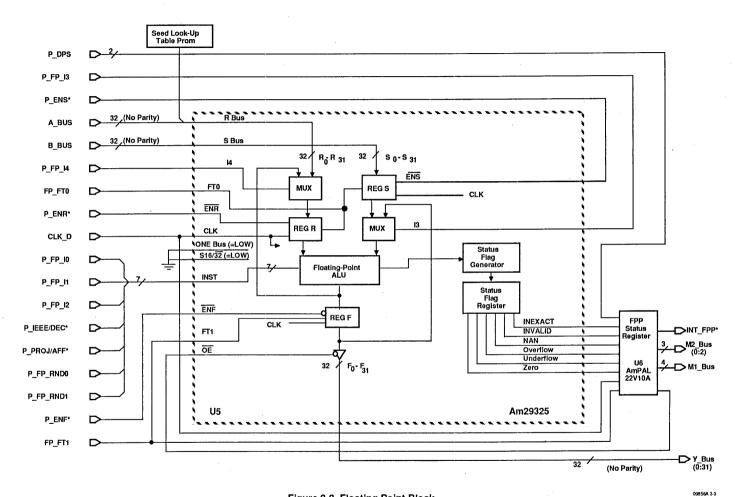

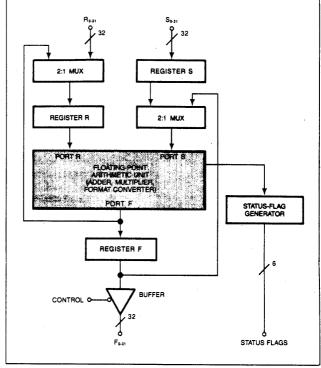

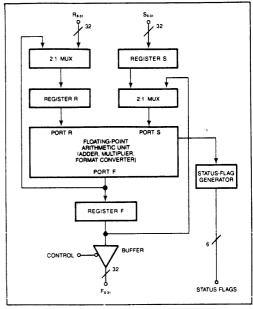

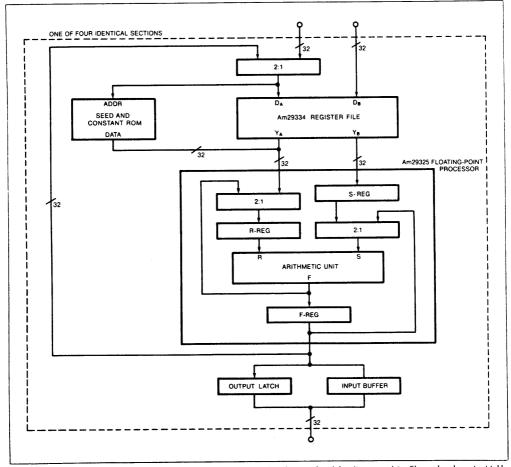

## Am29325/29C325

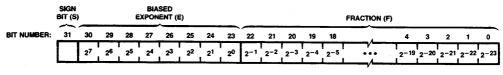

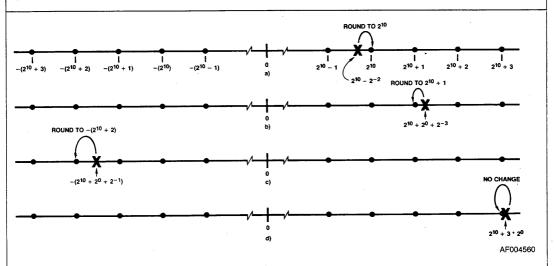

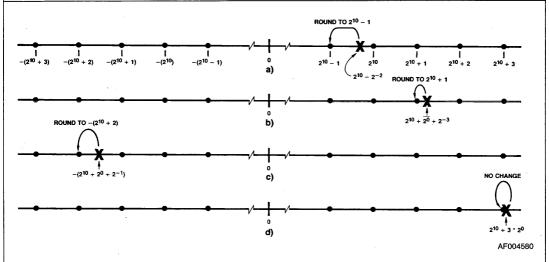

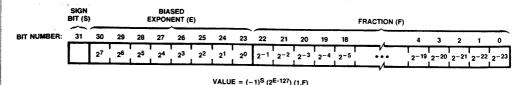

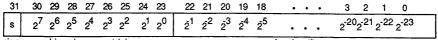

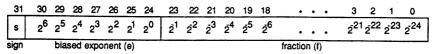

The Am29325/29C325 is a high-speed, single precision floating-point processor. It performs 32-bit floating-point addition, subtraction and multiplication operations in a single device, using either IEEE-P754, draft 10.0 or DEC VAX format.

## Single-Cycle Execution

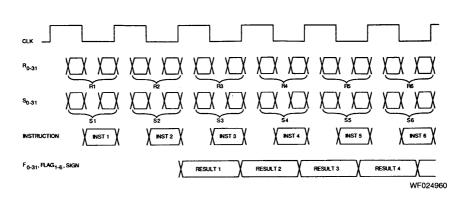

Since performance is the objective, all instructions—including multiply—require only one cycle to execute.

## No Mandatory Pipelining

Although the Am29325/29C325 FPP has input and output registers to make it a general purpose accelerator, there are no pipeline registers internal to the floating point array. Even the I/O registers can be made transparent.

### Three-Bus Architecture

The Am29325/29C325, like the Am29332/29C332, has a three-bus architecture, with two input buses and one output bus, thereby providing a bus compatible accelerator. This configuration provides high I/O bandwidth allowing the user to take full advantage of the single cycle, high-speed, floating-point ALU. Naturally, the input and output registers may be made transparent with individual clock enables. In addition, the input and output registers may be made transparent with independent feed-

through controls. The rules remain consistent – the system architecture achieves the highest performance when the component architectures do not interfere.

#### Powerful Instruction Set

The Am29325/29C325 executes the following instructions:

- Add (R plus S)

Subtract (R minus S)

Multiply (R times S)

- Constant Subtract (2 minus S)

- Integer to Floating Point Conversion

- Floating Point to Integer Conversion

- IEEE to DEC Format Conversion

- . DEC to IEEE Format Conversion

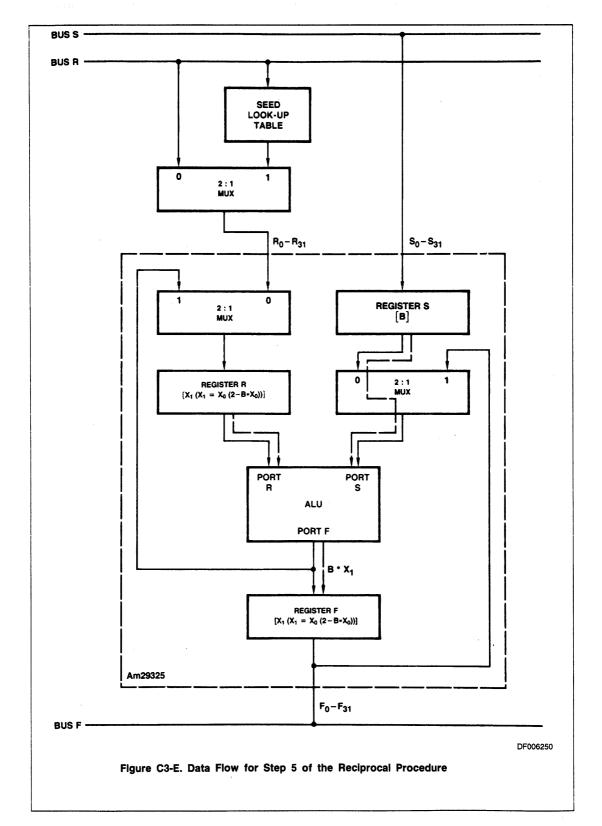

The instruction (2 minus S) is provided to support the Newton-Raphson division algorithm.

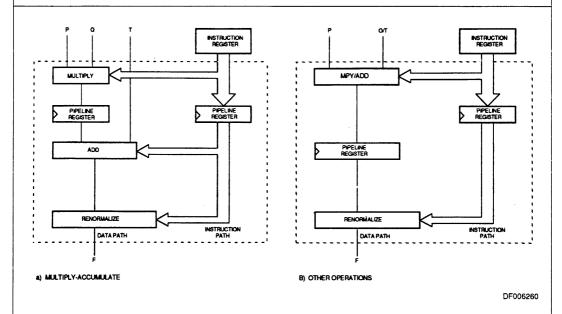

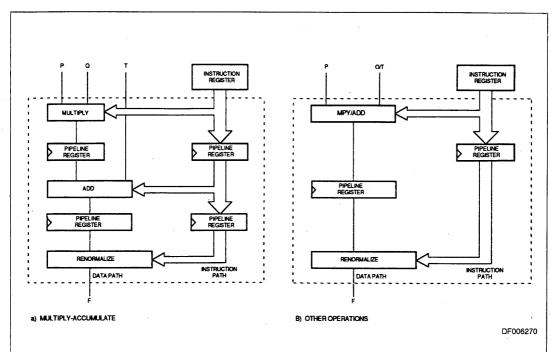

## Internal Data Paths Support Accumulation

The Am29325/29C325 has two internal feedback paths to facilitate two-cycle internal multiply-accumulate operation. The F1 bus can store the results of the multiply operation in an input register for subsequent accumulation. The F2 bus lets the output register function as an accumulator by making its output available as an operand for the next cycle.

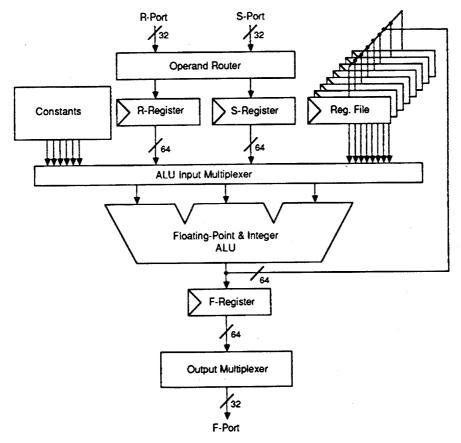

Figure 1-7. Am29325/29C325 32-Bit Floating Point Processor

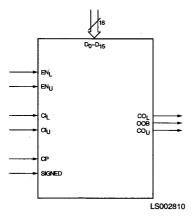

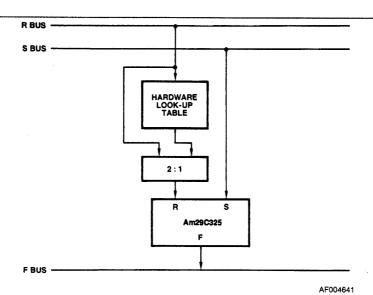

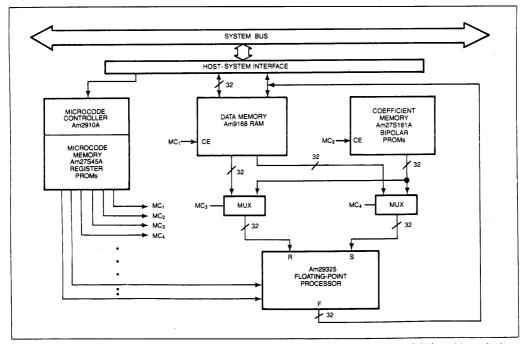

### Am29C325 Stand-Alone Performance

The Am29C325 is a stand-alone CMOS Floating Point Processor. When used with a simple sequencer such as the Am29C10A, it can be used as a low cost floating-point engine for applications requiring iterative algorithms such as Chebyshev and Newton-Raphson. These algorithms are used extensively in guidance, image and signal processing, and other DSP applications.

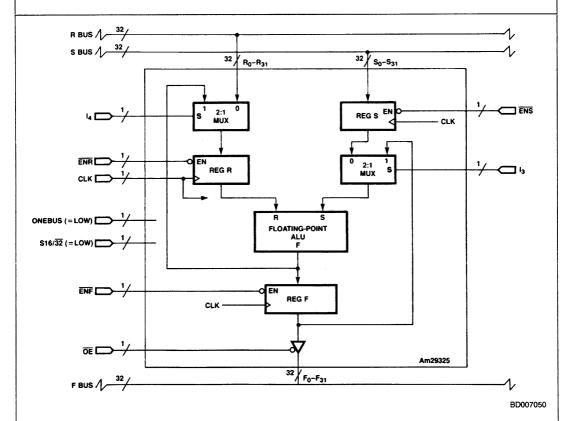

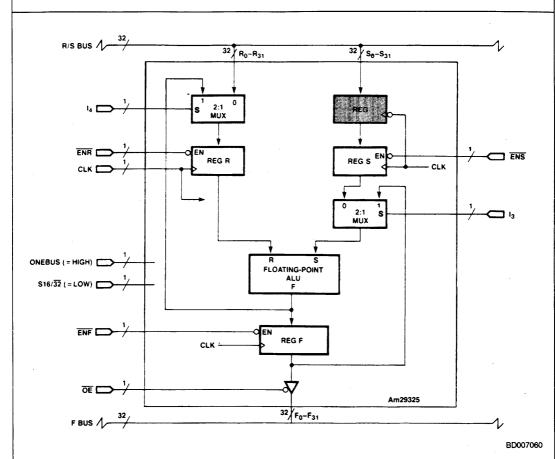

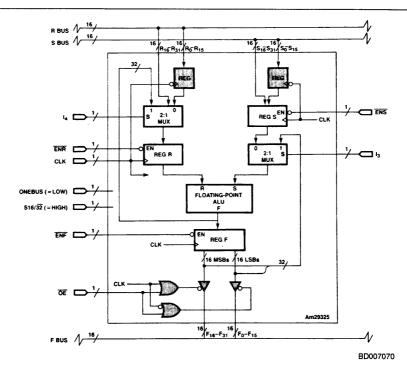

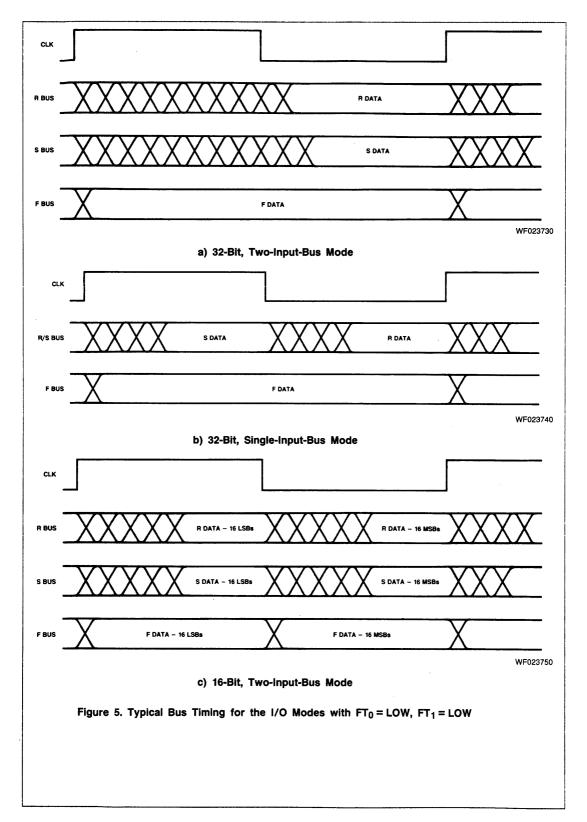

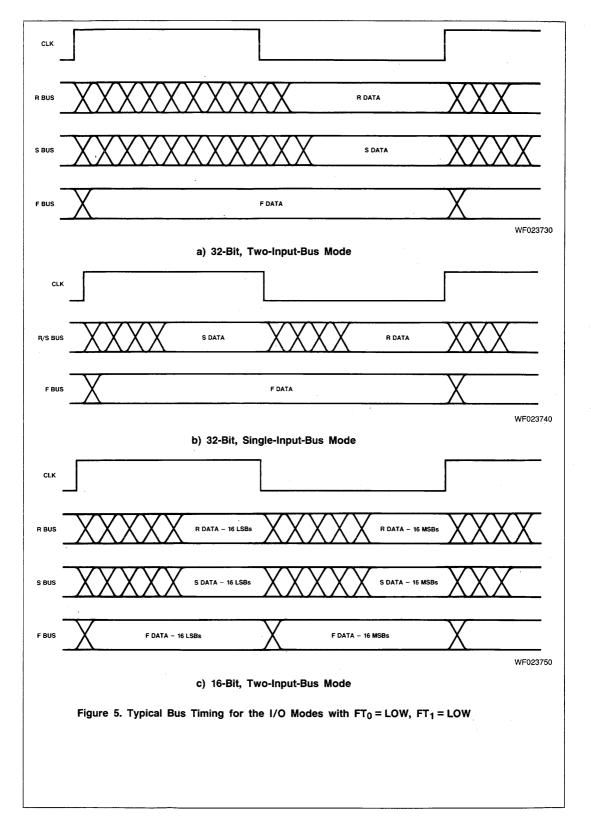

## Programmable I/O Structure

To provide compatability with different system buses, controls are provided for the following options:

- Two 32-bit input buses and one 32-bit output bus

- One 32-bit input bus and one 32-bit output bus

- Two 16-bit input buses and one 16-bit output bus

The input modes affect only the manner in which operands are entered into the device. The operation

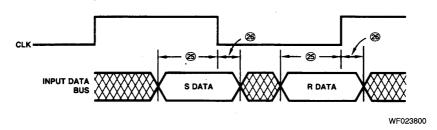

of the floating-point ALU is not altered. For example, in the 32-bit/one input-bus mode, the two 32-bit inputs are tied together and the two input operands are clocked into the input registers on alternate rising and falling edges of the clock. In the 16-bit, 3-bus mode, the 32-bit operands are delivered on two consecutive clock cycles in 16-bit increments.

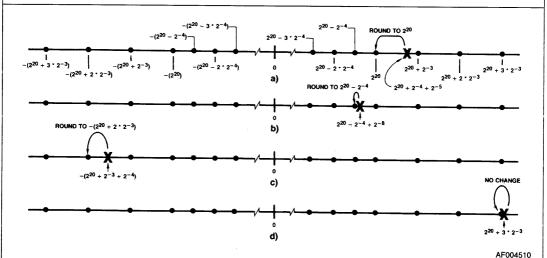

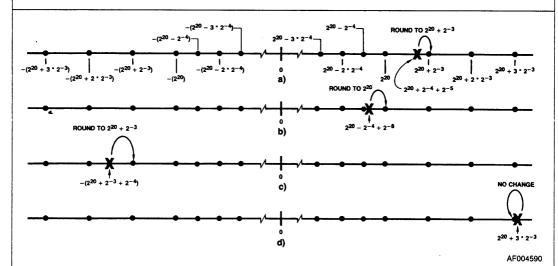

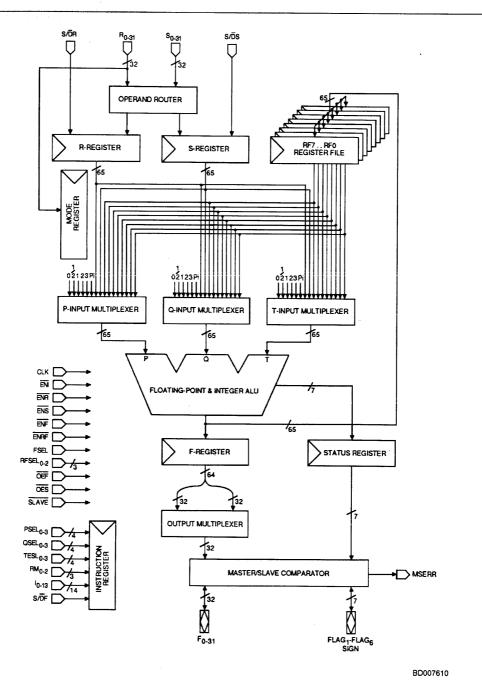

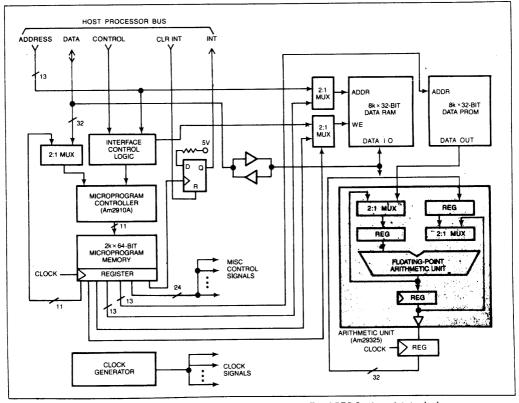

## Am29C327 Double-Precision Floating-Point Processor

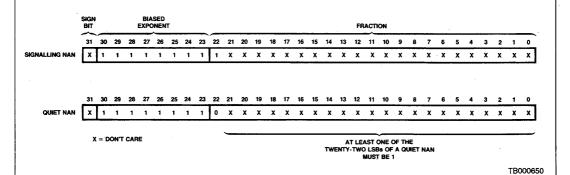

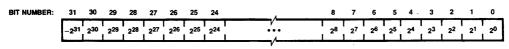

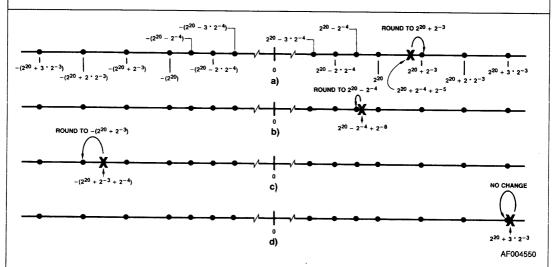

The Am29C327 double-precision floating-point processor is a high performance, single VLSI device that implements an extensive floating-point and integer instruction set. It can perform operations on single-, double-, or mixed-precision operands. The three most popular floating-point formats – IEEE, DEC, and IBM – are supported. IEEE operations comply with the standard P754, with direct implementation of special features such as gradual underflow and trap handling.

09372A 1-8

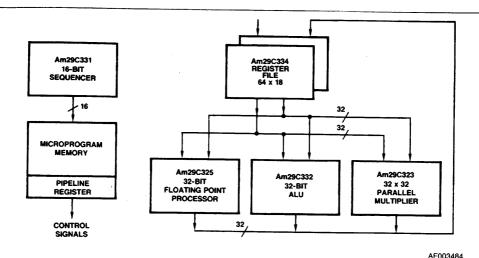

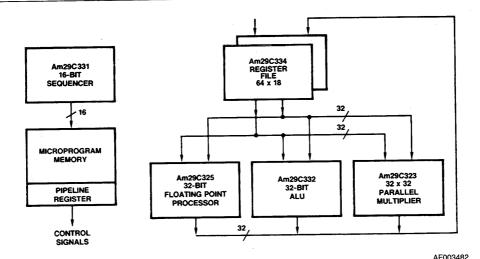

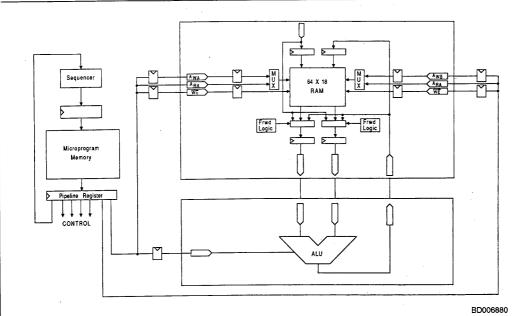

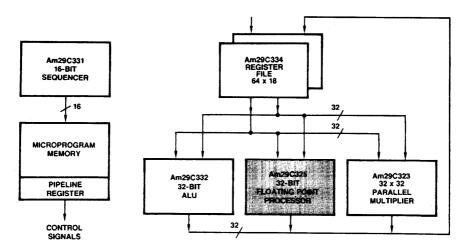

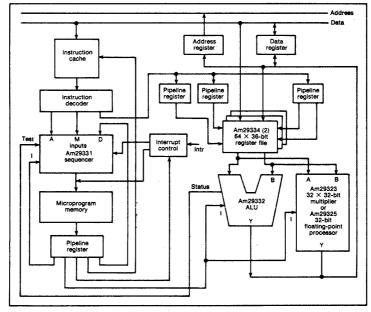

Figure 1-8. Microcoded Floating Point Co-Processor

Figure 1-9. Am29C327 Floating-Point Processor

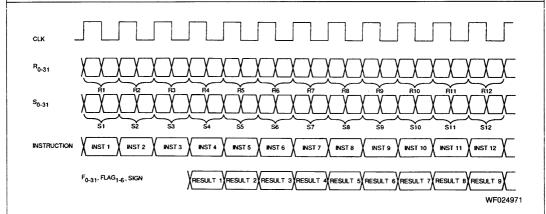

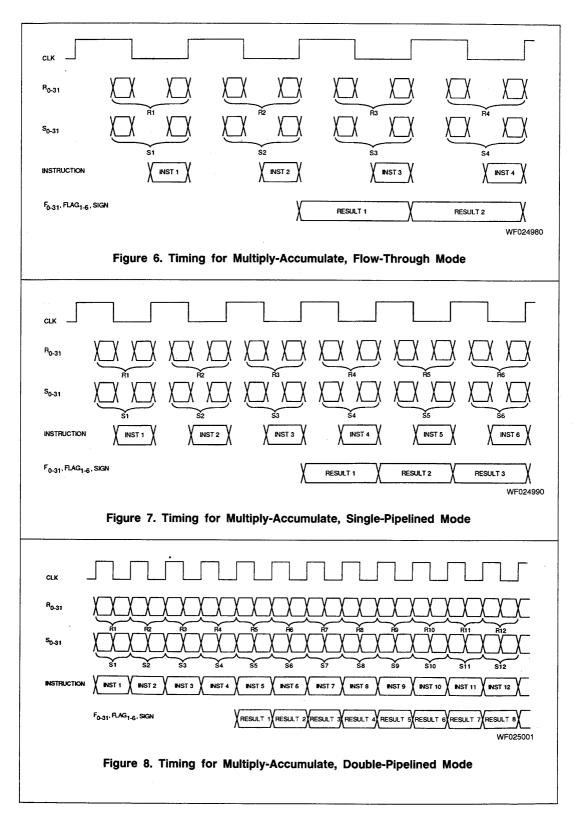

## Flow-Through or Pipelined

Operations can be performed in either of two modes: flow-through or pipelined. In the flow-through mode, the ALU is completely combinatorial; this mode is best suited for scalar operations. Pipelined mode divides the ALU into one or two pipelined stages for use in vector operations, as is often found in graphics or signal processing.

## Three-Bus Architecture

The Am29C327 has two input buses and one output bus – a three-bus architecture just like the Am29C325 floating-point processor. It provides flexibility and ease of interface, making it a very high performance accelerator.

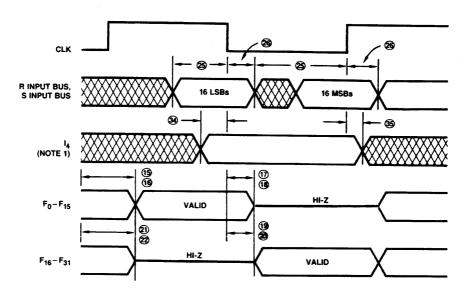

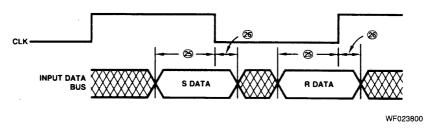

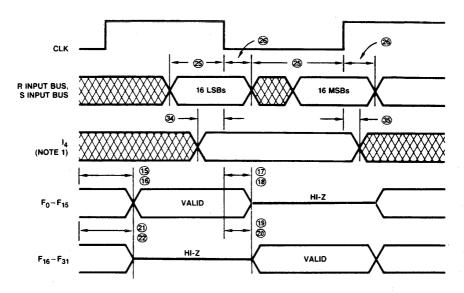

## Input/Output Modes

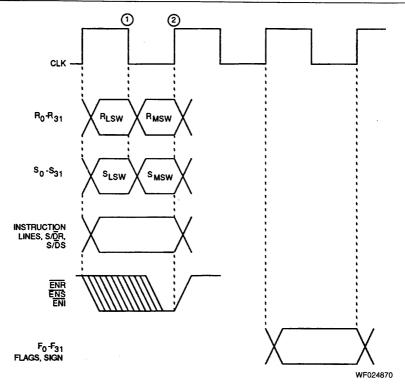

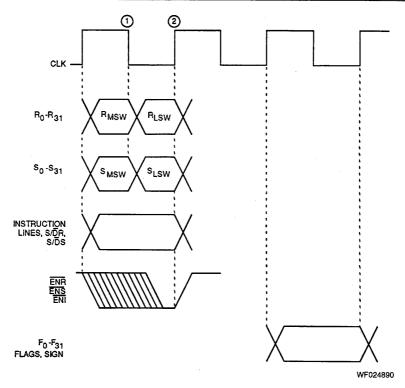

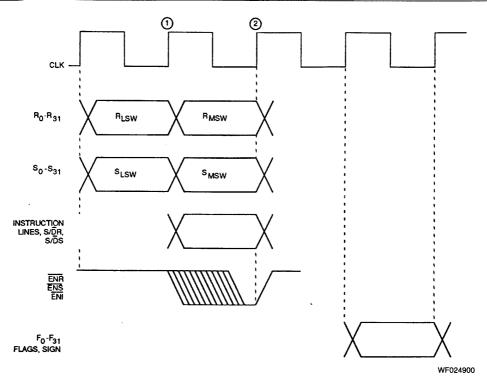

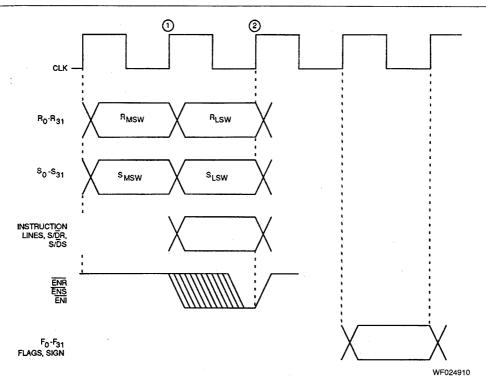

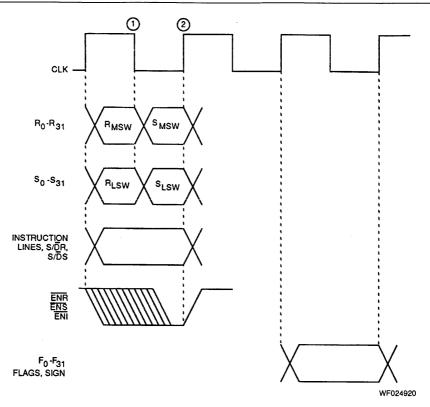

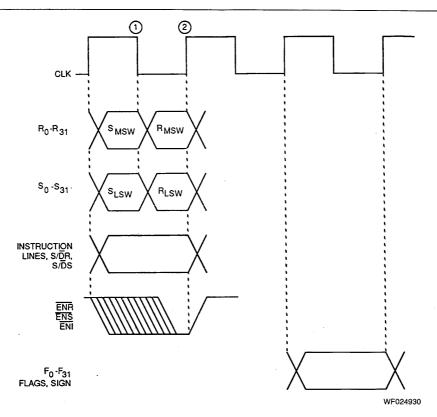

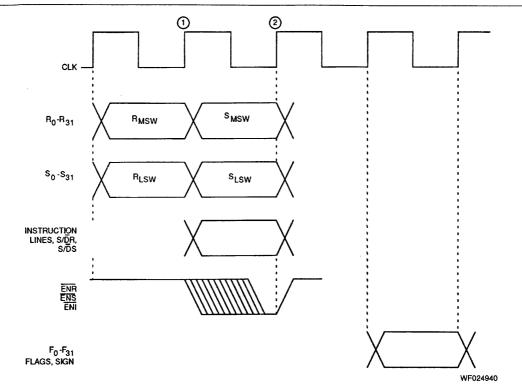

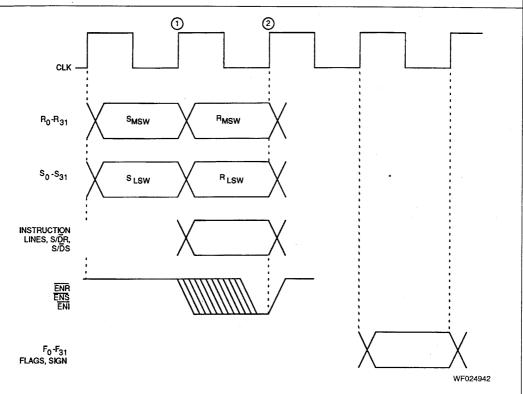

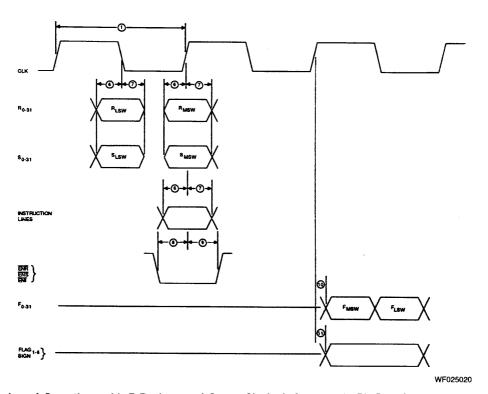

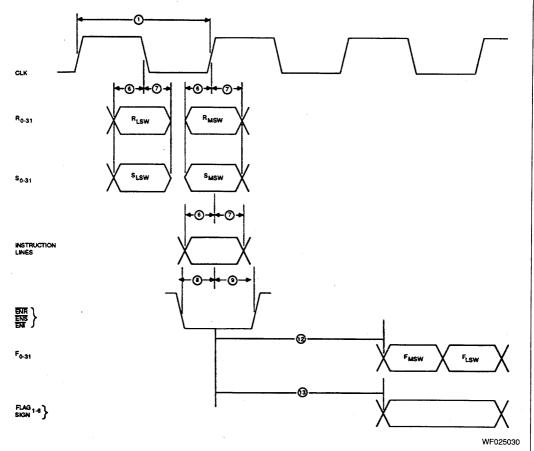

The Am29C327 supports eight I/O modes which provide a flexible interface to a variety of 32-bit and 64-bit systems. The input buses can be configured as separate 32-bit input buses or as a single 64-bit input bus. It is possible to load two 64-bit operands in a single clock cycle. The input modes are:

32-bit, double-cycle, LSWs first

32-bit, double-cycle, MSWs first

32-bit, single-cycle, LSWs first

32-bit, single-cycle, MSWs first

64-bit, double-cycle, R first

64-bit, double-cycle, S first

64-bit, single-cycle, R first

64-bit, single-cycle, S first

## Integer or Floating-Point

In addition to supporting 32-bit and 64-bit integer operations, the Am29C327 supports the following floating-point formats in single- or double-precision:

IEEE P754 version 10.1

DEC F, DEC D, and DEC G formats

IBM system 370 format.

Conversion between the floating-point formats and conversion between floating-point and integer formats are also provided. This is a very powerful feature not available in any other architecture.

## Mixed-Precision Operations

All Am29C327 instructions, floating-point or integer, can be performed in either single- or double-precision operands. In addition, the user can elect to mix precisions within an operation. All operations are internally performed in double precision; the user specifies the desired precision of the input and output operands. The

necessary precision conversions are made in concert with the selected operation, with no additional cycle-time overhead.

## Register File and Internal Datapath Support Compound Operations

The ALU of the Am29C327 has three data input ports and can perform operations of the form (A\*B)+C. An eight-deep register file for storing immediate results used in recursive operations, and the on-chip 64-bit datapath, facilitates compound operations such as Newton-Raphson division, sum-of-products, and transcendentals.

## Comprehensive Floating-Point and Integer Instruction Sets

The Am29C327 implements an extensive number of arithmetic and logical instructions. These instructions fall into the following categories:

addition/subtraction

multiplication

multiplication/ accumulation

comparison

max/min

saturation (clipping)

rounding to integral value

absolute value, negation

reciprocal seed generation

floating-point  $\leftarrow \rightarrow$  floating-point conversion

floating-point  $\leftarrow \rightarrow$  integer conversion

integer ← → integer conversion

pass operand

logical operations; e.g. AND, OR, XOR, NOT

move data

By concatenating these operations, the user can also perform division, square-root extraction, polynomial evaluation, and other functions not implemented directly.

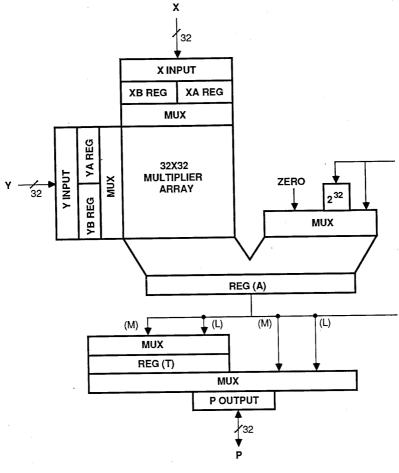

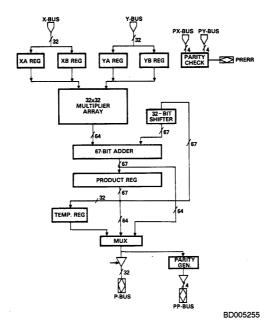

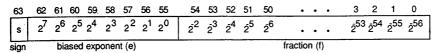

## Am29C323 Multiplier

The Am29C323 is a high-speed parallel 32x32-bit multiplier designed to speed up systems using fixed or floating-point notation.

## Three-Bus Architecture

Just like other members of the family, the Am29C323 has two input buses and one output bus. This configuration provides high I/O bandwidth, allowing the user to take full advantage of the high-speed parallel multiplier core of the device.

09372A 1-10

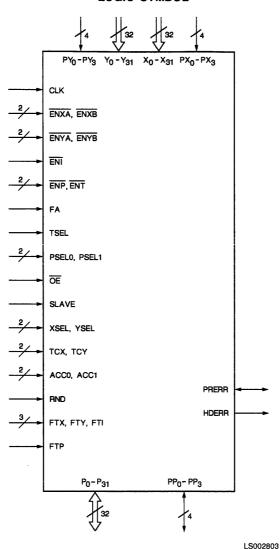

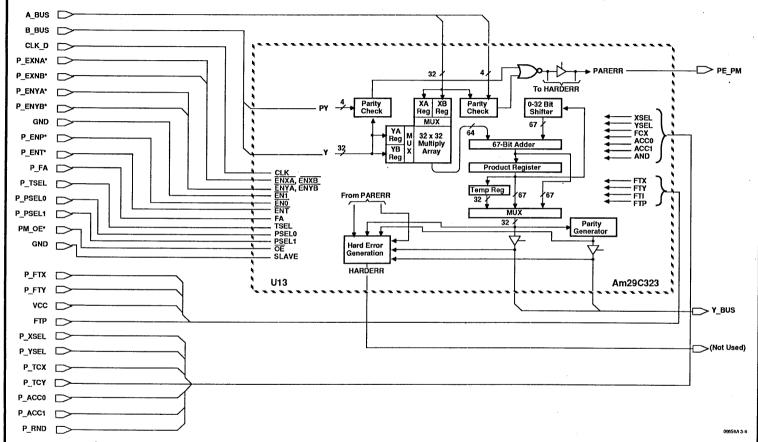

Figure 1-10. Am29C323 32x32 Parallel Multiplier

## Multiprecision Multiplication Made Easy

By including 32-bit shift and accumulate to generate partial products, the internal architecture of the Am29C323 supports fast multiprecision multiplication. Both input ports have dual 32-bit registers, and the output port can select from a 67-bit product register, a 32-bit temporary register, or directly from the 32x32-bit multiplier array. A complete 32x32-bit clocked multiplication takes a single cycle (naturally – and with no pipelining!). Multiprecision multiplication uses the shift and accumulate logic to collect partial products starting with the least significant product. The number of cycles depends upon the input data width, with three-cycle latency, as shown in the table below. By using the I/O registers for pipelin-

ing, much greater throughput can be achieved. For example, by overlapping 64x64-bit operations, a full 128-bit product is available every four cycles. Multiplying the mantissas of two double-precision 64-bit floating-point numbers, for example, is one possible application of this high speed multiprecision multiplication capacity.

|          | Number of Cycle   | es                       |

|----------|-------------------|--------------------------|

| Operands | Single<br>Product | Overlapped<br>Operations |

| 32x32    | 1                 | 1                        |

| 64x64    | 7                 | 4                        |

| 96x96    | 12                | 9                        |

| 128x128  | 19                | 16                       |

## Registered Buses

All buses in the device are registered, and each register has its own Clock Enable. The device operates from a single clock, ideal for microprogrammed systems. All ports – input, output, and instruction – can be made transparent independently.

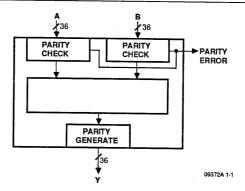

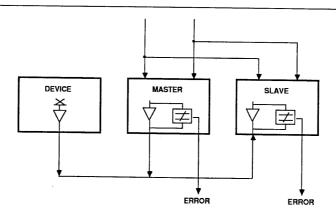

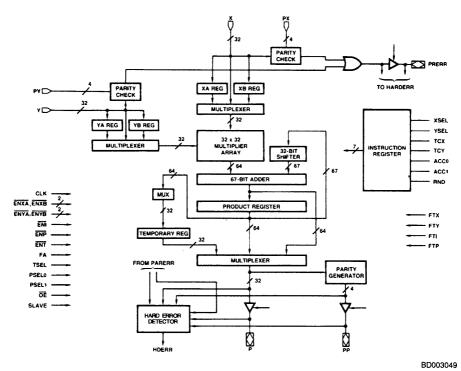

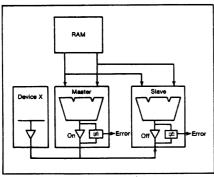

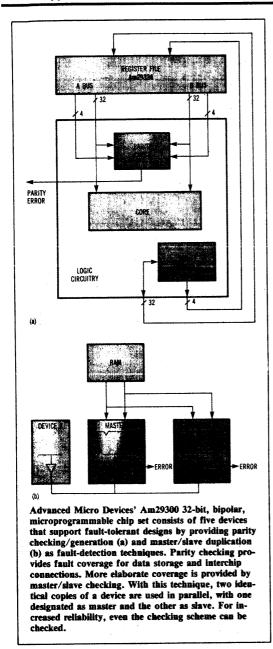

## Complete Interlocking Fault Detection

To enhance system reliability by ensuring data integrity and correct hardware operation, the family supports both master/slave fault detection and data path parity. The system features byte parity checking on the inputs and byte parity generation on the outputs of the Am29332/29C332 ALU and Am29C323 32x32-bit multiplier. Also, the organization of the Am29334/29C334 64x18 register file accommodates parity bits for each byte. The parity mechanism assures data path integrity. Major functional blocks—Am29332/29C332 ALU, Am29331/29C331 sequencer, Am29C323 32x32 bit multiplier, and

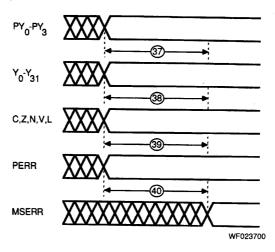

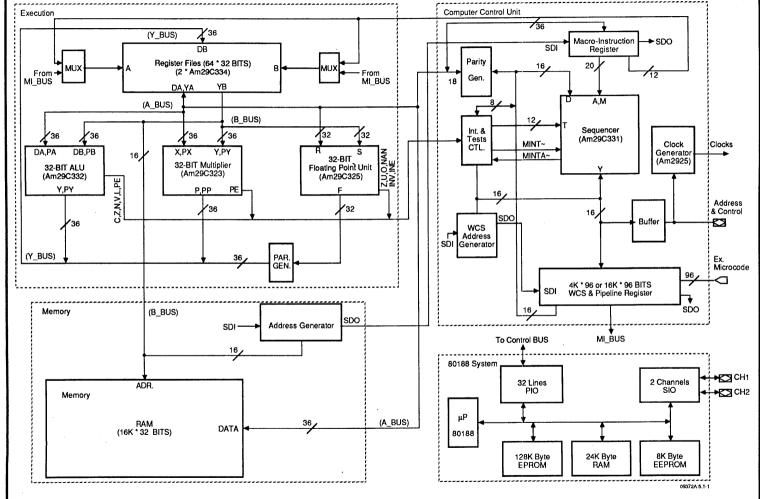

Am29C327 64-bit floating-point processor-have "master/slave fault detection" to ensure correct operation without having to carry parity through complex internal logic (shifters, mask generators, etc.) and without having to pay the resulting delay penalties. In master/slave mode, two functional units are connected in parallel with one unit doing the actual operation and the other checking the result, on a cycle-by-cycle, bit-by-bit basis. The master is used for the normal data path. In the slave, however, all outputs become inputs, and the slave compares the outputs of the master with its own internally generated result. If the two don't match, an error signal is generated, triggering an interrupt at the microinstruction level. No specialized software is required for the master/slave scheme. Also, the designer can choose to impose redundancy at the component or board level. The parity mechanism and the master/slave concept, which use cost-effective hardware rather than expensive software, provide a comprehensive solution for fault tolerant systems.

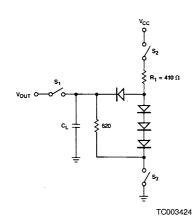

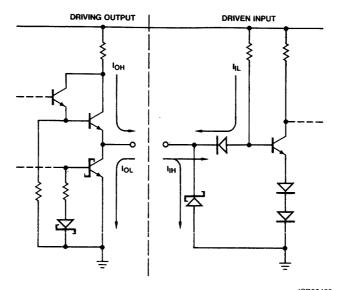

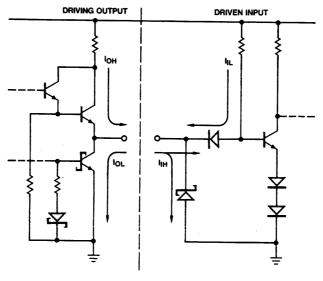

Figure 1-11. Input Parity Checking / Output Parity Checking

09372A 1-12

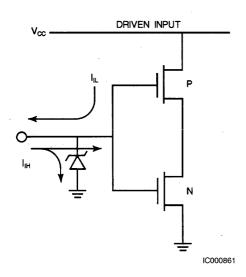

Figure 1-12. Master/Slave Error Checking

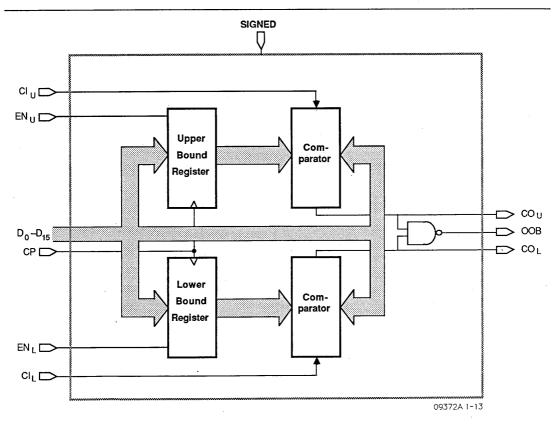

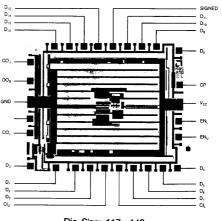

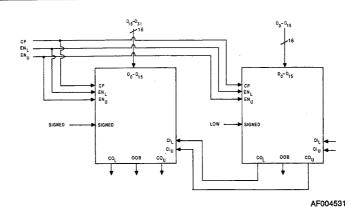

## Am29337 16-Bit Bounds Checker

The need for simple yet sophisticated functionality and board space savings created the Am29337, a 16-bit bounds checker. This product provides inexpensive, easy-to-use solutions fro the following applications:

- · intelligent address decoder

- · window clipping in graphics

- · filter in DSP

- · memory protection systems

- · RISC processors

- · multi/parallel processors

- · logic analyzers

- · tag/data buffers

The Am29337 compares incoming 16-bit data against both lower and upper bounds and reports whether the

data is inside or outside the bounds. It can be cascaded for 32-bit data and longer without sacrificing speed.

The Am29337 is housed in a 400 mil ceramic 28-pin DIP for board space savings.

### User Benefits

- · Replaces MSI devices, saves board space

- Low-cost solution compared to conventional alternatives

#### Distinctive Features

- Double Comparators compare a 16-bit input number against a lower and an upper limit

- 16-bit operation, cascadable to longer words

- Compares signed or unsigned numbers

Figure 1-13. Am29337 Block Diagram

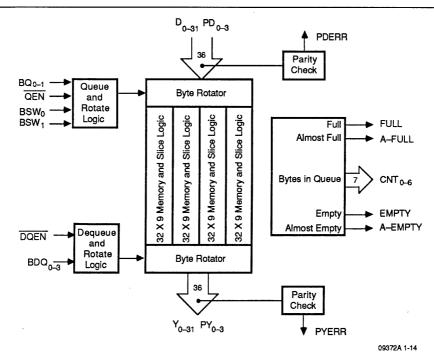

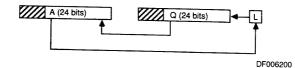

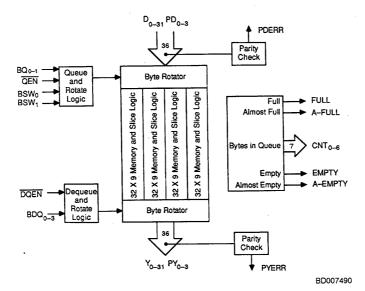

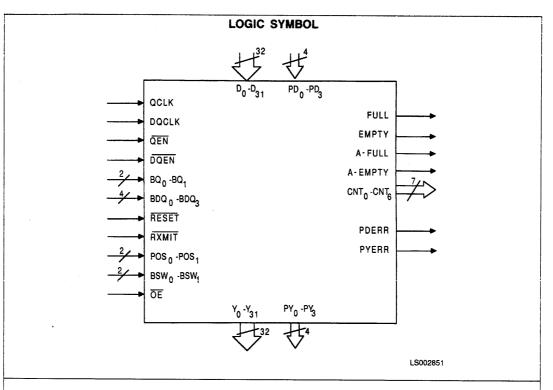

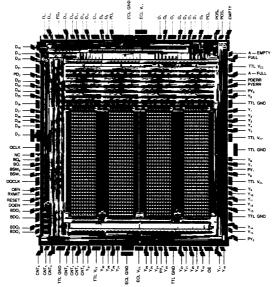

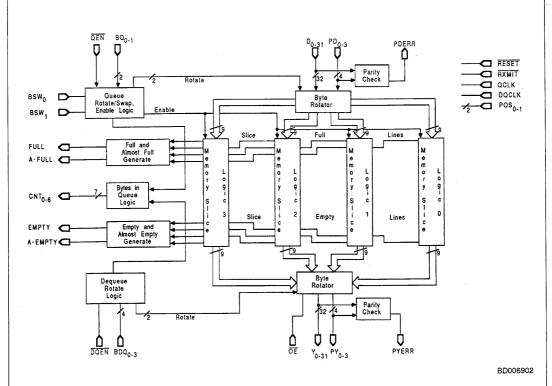

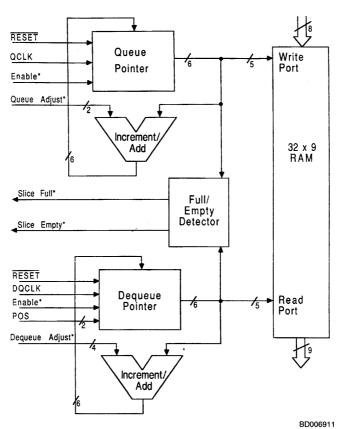

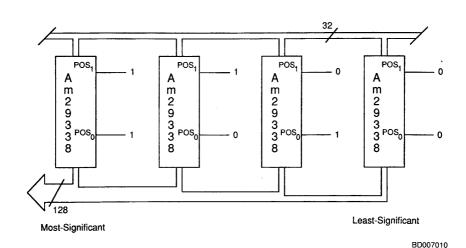

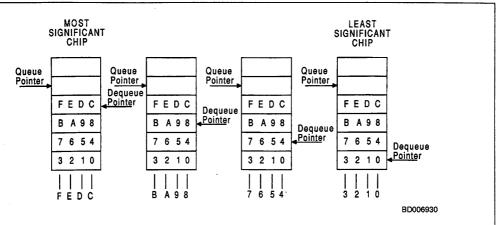

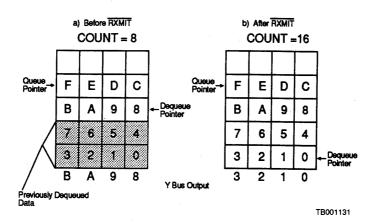

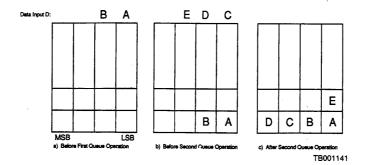

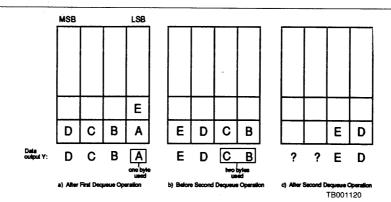

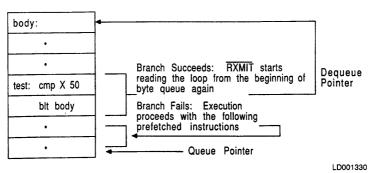

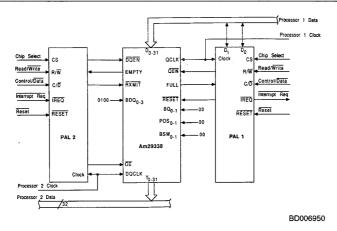

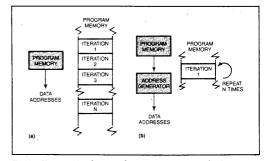

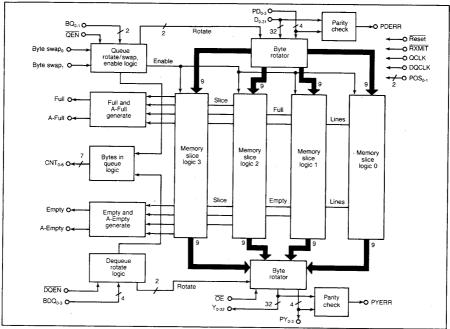

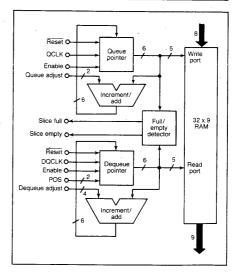

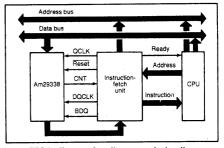

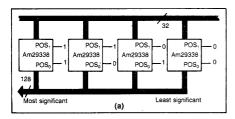

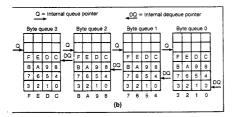

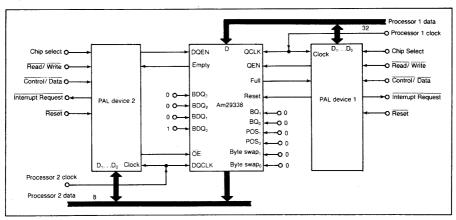

## Am29338 32-Bit Byte Queue

The Am29338 is a general purpose 32-bit intelligent FIFO that allows up to four bytes to be queued or dequeued in a single cycle.

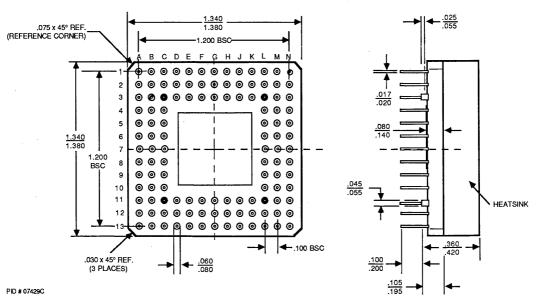

Fabricated with AMD's IMOX-S2 technology and housed in a 120-pin PGA, the Am29338 meets the requirements for a high-speed FIFO buffer with minimum real estate. The part will also be made available in high-speed, low-power 1.2 micron CMOS technology.

## Features of the Am29338 include:

- · Queuing of up to 128 bytes

- · Queuing or de-queuing of up to 4 bytes at a time

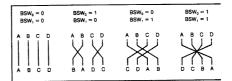

- · Byte rotation on the inputs and outputs

- · Asynchronous/synchronous operations

- Accepts 8-, 16-, 24-, and 32-bit input data

- · Repetitive queuing of block data

- Almost empty/full signal if less than 4 bytes available

## Significant User Benefits

The Am29388 is an excellent choice for a wide variety of system design problems. Its benefits include: a shorter design cycle when compared with implementing the same functions with traditional FIFOs, higher performance, off-the-shelf functionality, less board space, and less power than the separate parts needed to combine this logic.

## **Applications**

- Hardware mailbox between two heterogeneous processors

- I/O bus buffers between a processor and controller

- Instruction prefetch queue for byte addressable microprocessor systems

- Write buffer between CPU and main memory

- Bus conversions, 8-, 16-, 24-, and 32-bits.

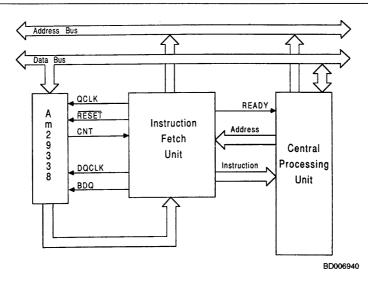

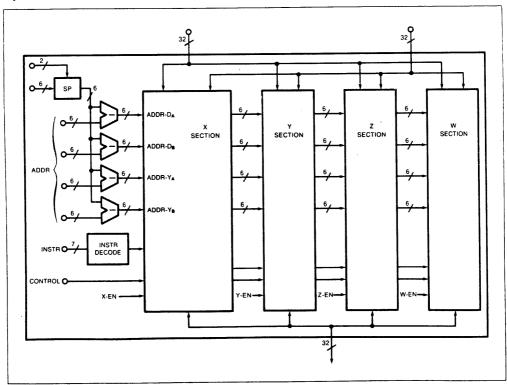

Figure 1-14. Am29338 Block Diagram

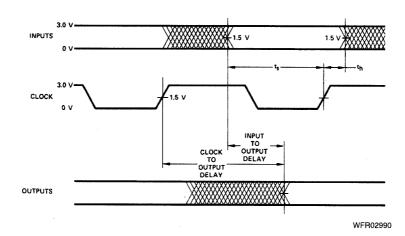

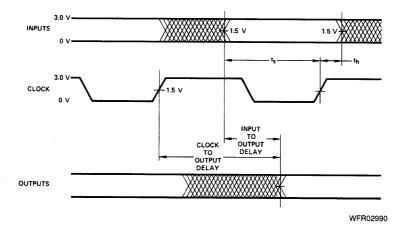

## 1.3 A.C. AND D.C. PARAMETER DEFINITIONS

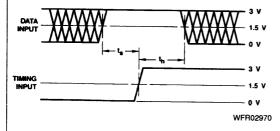

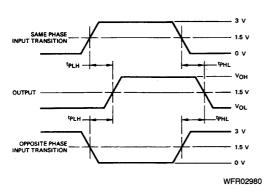

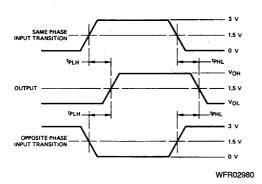

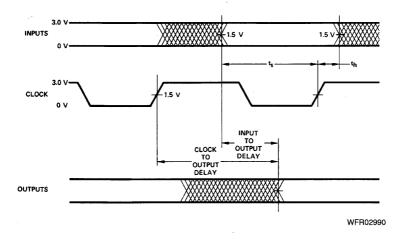

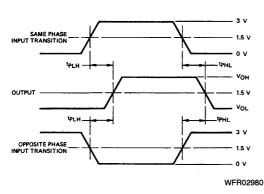

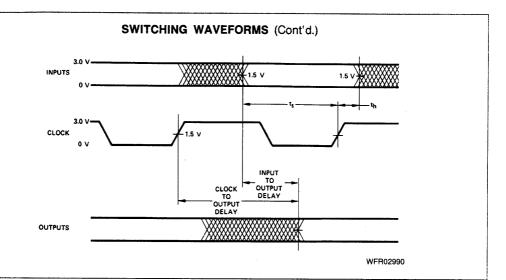

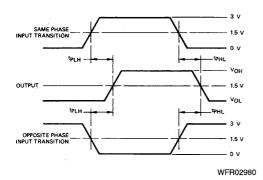

## **Definition of A.C. Switching Terms**

| The highest operating clock frequency.                                                         |

|------------------------------------------------------------------------------------------------|

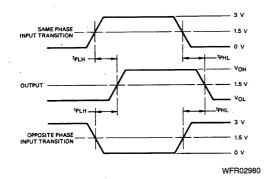

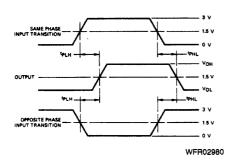

| The propagation delay time from an input change to an output LOW-to-HIGH transition.           |

| The propagation delay time from an input change to an output HIGH-to-LOW transition.           |

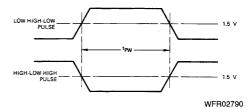

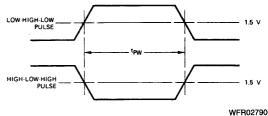

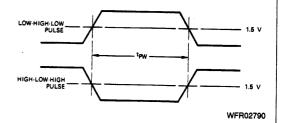

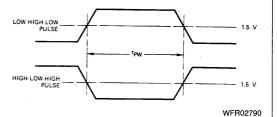

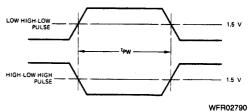

| Pulse width. The time between the leading and trailing edges of a pulse.                       |

| Rise time. The time required for a signal to $$ change from 10% to 90% of its measured values. |

| Fall time. The time required for a signal to change from 90% to 10% of its measured values.    |

|                                                                                                |

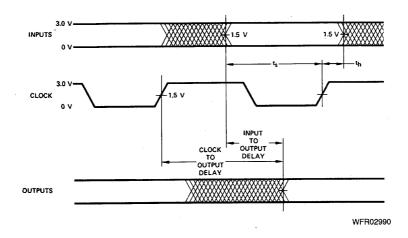

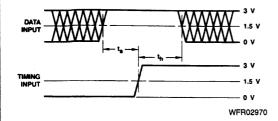

Set-up time. The time interval for which a signal must be applied and maintained at one input terminal before an active transition occurs at another terminal.

Hold time. The time interval for which a signal must be retained at one input after an active transition occurs

at another input terminal.

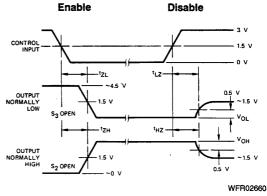

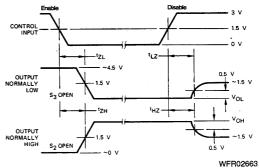

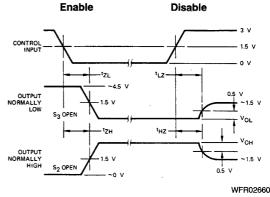

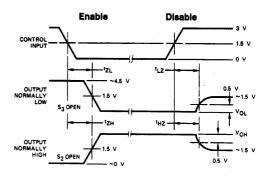

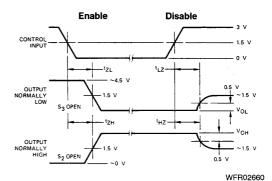

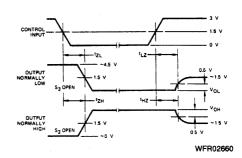

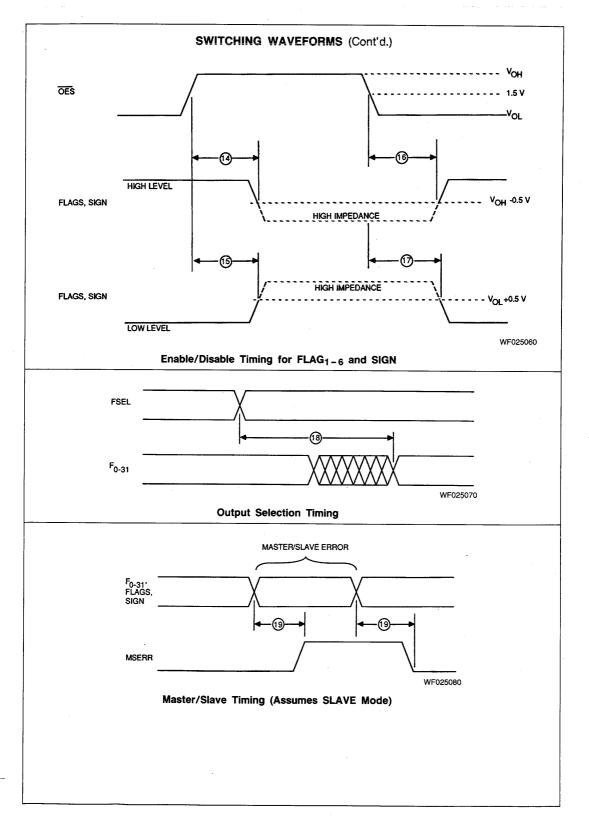

HIGH to disable. The delay time from a control input change to the output transition from the HIGH-level

to high-impedance (measured at 0.5V change).

LOW to disable. The delay time from a control input change to the output transition from the LOW-level

to high-impedance transition (measured at 0.5 V change).

t<sub>2H</sub> Enable HIGH. The delay time from a control input change to the output transition from high-impedance to HIGH-level.

t<sub>ZL</sub> Enable LOW. The delay time from a control input change to the output transition from high-impedance to LOW-level.

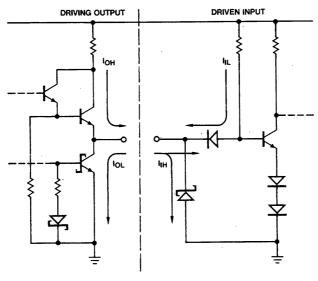

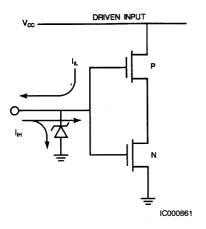

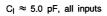

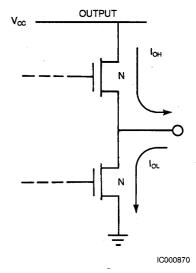

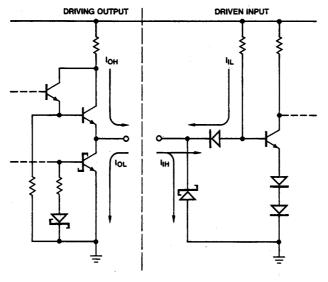

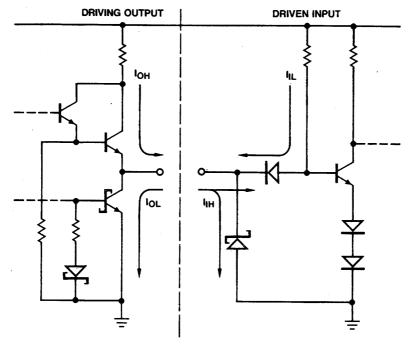

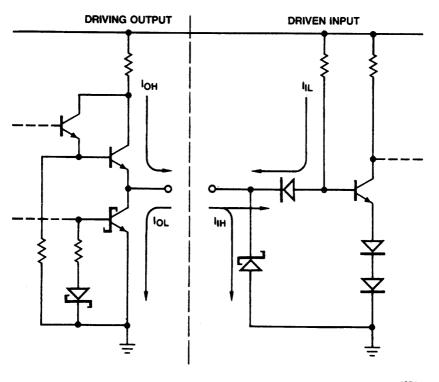

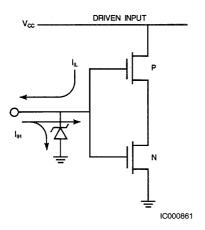

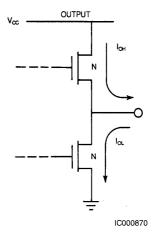

## Definition of D.C. Terms

| $C_{PD}$            | Power dissipation capacitance used to determine the no-load dynamic current consumption. |

|---------------------|------------------------------------------------------------------------------------------|

| Н                   | HIGH, applying to a HIGH voltage level.                                                  |

| L                   | LOW, applying to a LOW voltage level.                                                    |

| 1                   | Input                                                                                    |

| 0                   | Output                                                                                   |

| Negative<br>Current | Current flowing out of the device.                                                       |

| Positive<br>Current | Current flowing into the device.                                                         |

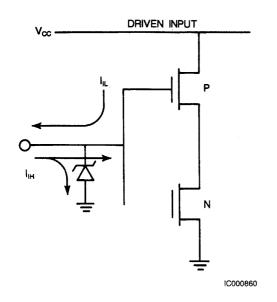

| I                   | LOW-level input current with a specified LOW-level voltage applied.                      |

| I <sub>IH</sub>     | HIGH-level input current with a specified HIGH-level voltage applied.                    |

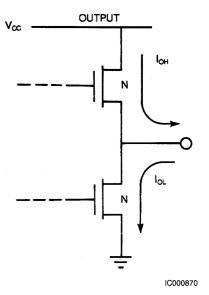

| I <sub>OL</sub>     | LOW-level output current.                                                                |

| $I_{OH}$            | HIGH-level output current.                                                               |

| I <sub>sc</sub>     | Output short-circuit source current.                                                     |

| I <sub>cc</sub>     | Supply current drawn by the device from the $V_{\rm cc}$ power supply.                   |

| I <sub>OZH</sub>    | Three-state off-state output current, HIGH- level voltage applied.                       |

| I <sub>OZL</sub>    | Three-state off-state output current, LOW- level voltage applied.                        |

## Am29300/29C300 Family Overview

| $V_{cc}$        | The range of supply voltage over which the device is guaranteed to operate.                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| $V_{IL}$        | The highest input voltage that is guaranteed to be recognized by the device as a logic LOW.                                             |

| $V_{IH}$        | The lowest input voltage that is guaranteed to be recognized by the device as a logic HIGH.                                             |

| $V_{OL}$        | The highest logic LOW voltage guaranteed at the output terminal while sinking the specified load current $\mathbf{I}_{\text{OL}}$ .     |

| $V_{OH}$        | The lowest logic HIGH voltage guaranteed at the output terminal when sourcing the specified source current $\boldsymbol{I}_{\text{OH}}$ |

| I <sub>EE</sub> | The supply current drawn by the device from the $V_{\text{EE}}$ power supply for an ECL circuit.                                        |

| $V_{EE}$        | Most negative power supply for an ECL circuit.                                                                                          |

## **CHAPTER 2**

| CMOS Family                                              |      |

|----------------------------------------------------------|------|

| Am29C331 CMOS 16-Bit Microprogram Sequencer              | 2-1  |

| Am29C332 CMOS 32-Bit Arithmetic Logic Unit               | 2-38 |

| Am29C334 CMOS Four-Port Dual-Access Register File        | 2-76 |

| Am29C325 CMOS 32-Bit Floating-Point Processor*           | 2-94 |

| Am29C327 CMOS Double-Precision Floating-Point Processor* | 2-95 |

<sup>\*</sup> Front page only of data sheet. See Chapter 4 for complete data sheet.

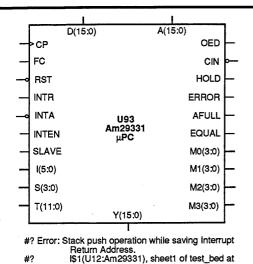

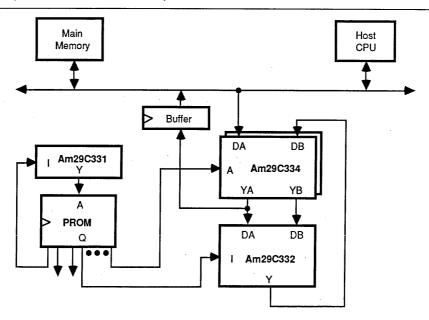

## Am29C331

CMOS 16-Bit Microprogram Sequencer

#### **PRELIMINARY**

## DISTINCTIVE CHARACTERISTICS

### • 16-Bits Address up to 64K Words

Supports 110-ns microcycle time for a 32-bit highperformance system when used with the other members of the Am29C300 Family.

## Speed Select

Supports 80-ns system cycle time.

## Real-Time Interrupt Support

Micro-trap and interrupts are handled transparently at any microinstruction boundary.

#### • Built-In Conditional Test Logic

Has twelve external test inputs, four of which are used to internally generate an additional four test conditions. Test multiplexer selects one out of 16 test inputs.

#### Break-Point Logic

Built-in address comparator allows break-points in the microcode for debugging and statistics collection.

#### Master/Slave Error Checking

Two sequencers can operate in parallel as a master and a slave. The slave generates a fault flag for unequal results.

#### • 33-Level Stack

Provides support for interrupts, loops, and subroutine nesting. It can be accessed through the D-bus to support diagnostics.

## **GENERAL DESCRIPTION**

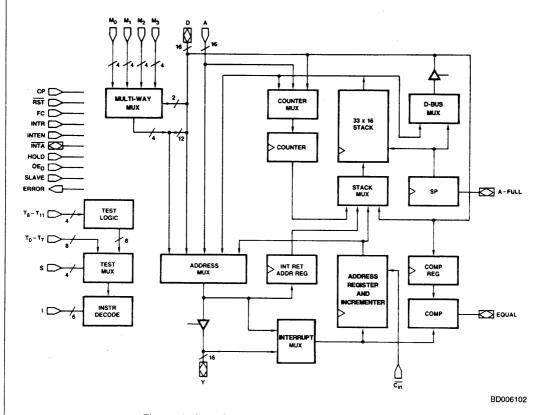

The Am29C331 is a 16-bit wide, high-speed single-chip sequencer designed to control the execution sequence of microinstructions stored in the microprogram memory. The instruction set is designed to resemble high-level language constructs, thereby bringing high-level language programming to the micro level.

The Am29C331 is interruptible at any microinstruction boundary to support real-time interrupts. Interrupts are handled transparently to the microprogrammer as an unexpected procedure call. Traps are also handled transparently at any microinstruction boundary. This feature allows re-execution of the prior microinstruction. Two separate buses are provided to bring a branch address directly into the chip from two sources to avoid slow turn-on and turn-off times for different sources connected to the data-input bus. Four

sets of multiway inputs are also provided to avoid slow turnon and turn-off times for different branch-address sources. This feature allows implementation of table look-up or use of external conditions as part of a branch address. The 33-deep stack provides the ability to support interrupts, loops, and subroutine nesting. The stack can be read through the D-bus to support diagnostics or to implement multitasking at the micro-architecture level. The master/slave mode provides a complete function check capability for the device.

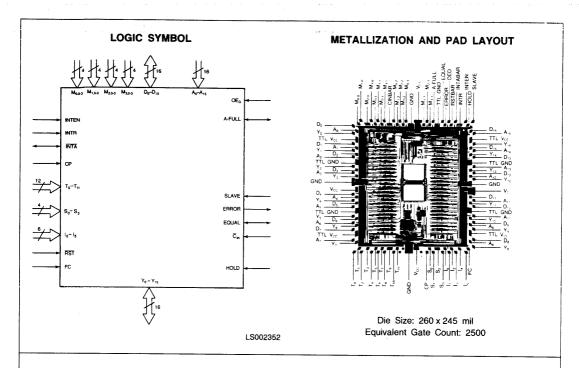

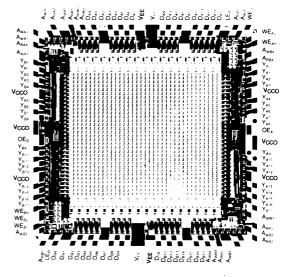

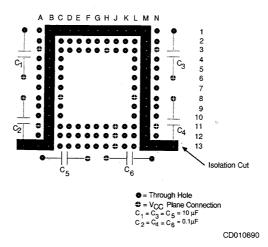

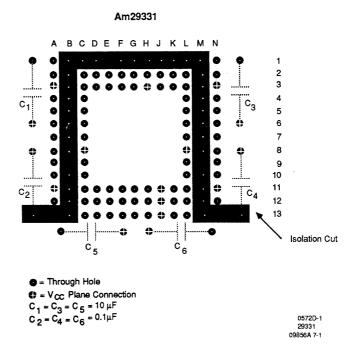

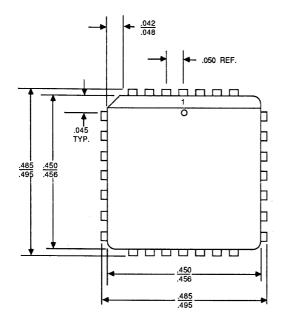

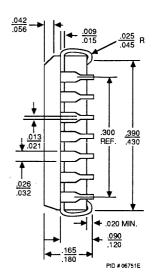

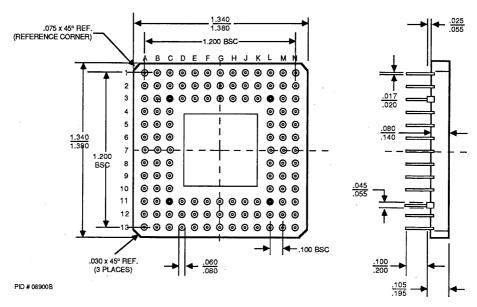

Fabricated using Advanced Micro Devices' 1.6 micron CMOS process, the Am29C331 is powered by a single 5-volt supply. The device is housed in a 120-terminal pin-grid array package.

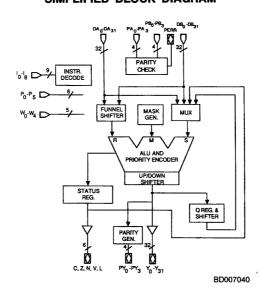

## SIMPLIFIED BLOCK DIAGRAM

Publication # Rev. Amendmen

08823 C /0

Issue Date: December 1987

## **RELATED AMD PRODUCTS**

| Part No.  | Description                                      |

|-----------|--------------------------------------------------|

| Am29114   | Vectored Priority Interrupt Controller           |

| Am29116   | High-Performance Bipolar 16-Bit Microprocessor   |

| Am29C116  | High-Performance CMOS 16-Bit Microprocessor      |

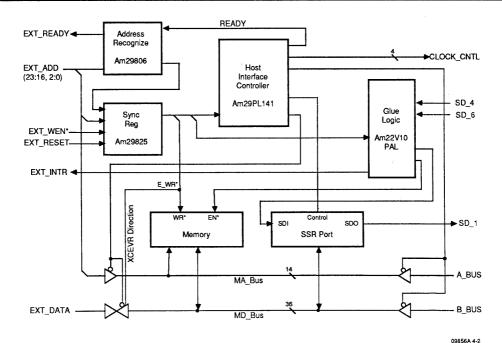

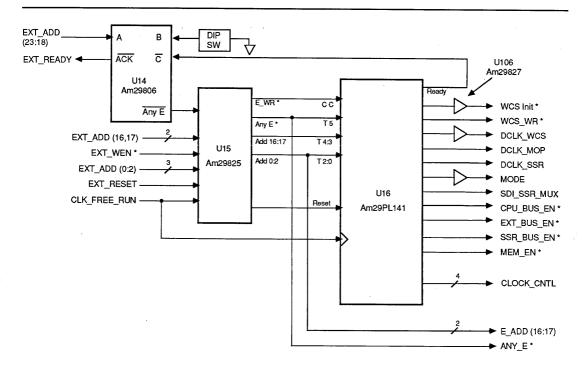

| Am29PL141 | Field-Programmable Controller                    |

| Am29C323  | CMOS 32-Bit Parallel Multiplier                  |

| Am29325   | 32-Bit Floating-Point Processor                  |

| Am29C325  | CMOS 32-Bit Floating-Point Processor             |

| Am29332   | 32-Bit Extended Function ALU                     |

| Am29C332  | CMOS 32-Bit Extended Function ALU                |

| Am29334   | 64 x 18 Four-Port, Dual-Access Register File     |

| Am29C334  | CMOS 64 x 18 Four-Port Dual-Access Register File |

| Am29337   | 16-Bit Bounds Checker                            |

| Am29338   | Byte Queue                                       |

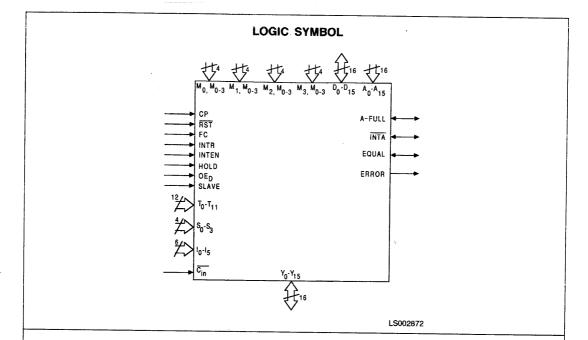

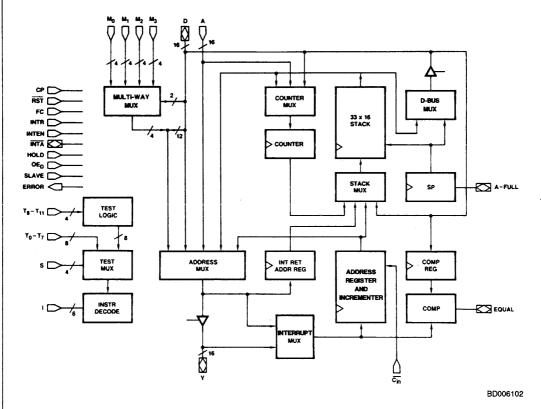

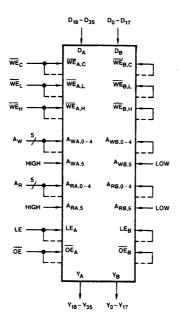

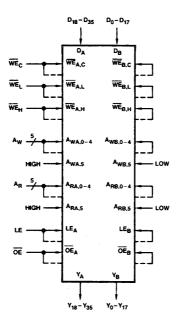

Figure 1. Am29C331 Detailed Block Diagram

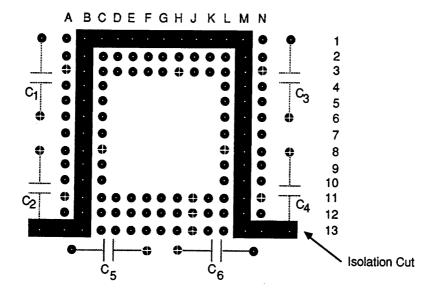

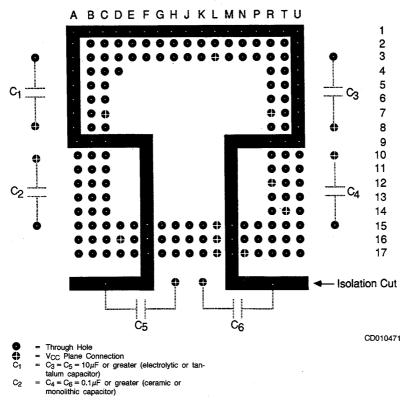

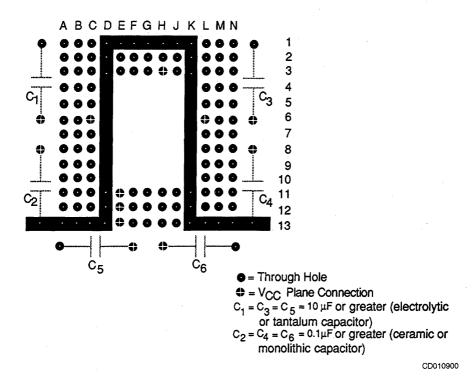

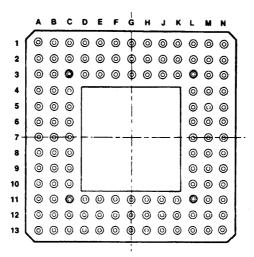

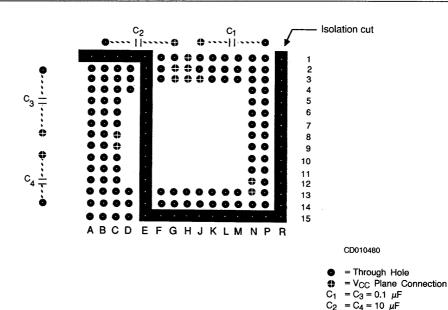

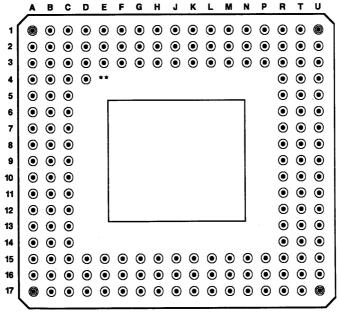

## CONNECTION DIAGRAM

## 120-Lead PGA\*

|     | A    | В          | С    | Đ            | E    | F          | G            | H    | J      | ĸ     | L          | м           | N   |

|-----|------|------------|------|--------------|------|------------|--------------|------|--------|-------|------------|-------------|-----|

| 1   | M0,0 | M1,0       | M2,0 | M2,1         | CIN  | M1,2       | M1,3         | M2,3 | GND    | RST   | INTR       | SLAVE       | D15 |

| 2   | DO   | A0         | M3,0 | M1,1         | M0,2 | M2,2       | <b>M</b> 0,3 | M3,3 | EQUAL  | OED   | INTEN      | HOLD        | A15 |

| 3   | vcc  | YO         | D1   | <b>M</b> 0,1 | M3,1 | GND        | M3,2         | vcc  | A-FULL | ERROR | ÎNTA       | Y15         | vcc |

| 4   | A1 . | <b>Y</b> 1 | D2   |              |      |            |              |      |        |       | D14        | A14         | Y14 |

| 5   | GND  | A2         | Y2   |              |      |            |              |      |        |       | D13        | A13         | GND |

| 6   | A3   | D3         | GND  |              |      |            |              |      |        |       | GND        | D12         | Y13 |

| · 7 | Y3   | D4         | A4   |              |      |            |              |      |        |       | A12        | Y12         | D11 |

| 8   | D5   | Y4         | vcc  |              |      |            |              |      |        |       | vcc        | <b>Y</b> 11 | A11 |

| 9   | GND  | <b>A</b> 5 | Y5   |              |      |            |              |      |        |       | D10        | A10         | GND |

| 10  | D6   | A6         | Y6   |              |      |            |              |      |        |       | Y10        | D9          | A9  |

| 11  | vcc  | D7         | T3   | Т6           | GND  | T10        | T11          | 10   | vcc    | 13    | <b>Y</b> 9 | D8          | vcc |

| 12  | A7   | T1         | T2   | T5           | GND  | <b>T</b> 7 | S0           | S1   | vcc    | 12    | 14         | A8          | Y8  |

| 13  | Y7   | ТО         | Т9   | T4           | GND  | T8         | СР           | S3   | vcc    | n     | \$2        | 15          | FC  |

CD010380

<sup>\*</sup>Pins facing up.

## PIN DESIGNATIONS (Sorted by Pin No.)

|         |                   |            |            | ,00                | ,          |            | ,               |            |            |                 |            |

|---------|-------------------|------------|------------|--------------------|------------|------------|-----------------|------------|------------|-----------------|------------|

| PIN NO. | PIN NAME          | PAD<br>NO. | PIN<br>NO. | PIN NAME           | PAD<br>NO. | PIN<br>NO. | PIN NAME        | PAD<br>NO. | PIN<br>NO. | PIN NAME        | PAD<br>NO. |

|         |                   |            | C-5        | Y <sub>2</sub>     | 115        | H-2        | Мз. з           | 10         | M-5        | A <sub>13</sub> | 80         |

|         |                   |            | C-6        | GND                | 113        | H-3        | VCC             | 68         | M-6        | D <sub>12</sub> | 81         |

|         |                   |            | C-7        | A <sub>4</sub>     | 52         | H-11       | l <sub>0</sub>  | 34         | M-7        | Y <sub>12</sub> | 82         |

|         |                   |            | C-8        | Vcc                | 53         | H-12       | S <sub>1</sub>  | 95         | M-8        | Y <sub>11</sub> | 25         |

| A-1     | M <sub>0, 0</sub> | 1          | C-9        | Y <sub>5</sub>     | 109        | H-13       | S <sub>3</sub>  | 94         | M-9        | A <sub>10</sub> | 86         |

| A-2     | D <sub>0</sub>    | 120        | C-10       | Y <sub>6</sub>     | 48         | J-1        | GND             | 11         | M-10       | D <sub>9</sub>  | 87         |

| A-3     | Vcc               | 59         | C-11       | T <sub>3</sub>     | 44         | J-2        | EQUAL           | 71         | M-11       | D <sub>8</sub>  | 89         |

| A-4     | A <sub>1</sub>    | 58         | C-12       | T <sub>2</sub>     | 104        | J-3        | A-FULL          | 70         | M-12       | A <sub>8</sub>  | 30         |

| A-5     | GND               | 56         | C-13       | T <sub>9</sub>     | 41         | J-11       | · Vcc           | 37         | M-13       | 15              | 91         |

| A-6     | A <sub>3</sub>    | 114        | D-1        | M <sub>2, 1</sub>  | 4          | J-12       | Vcc             | 38         | N-1        | D <sub>15</sub> | 16         |

| A-7     | Y <sub>3</sub>    | 54         | D-2        | M <sub>1, 1</sub>  | 63         | J-13       | Vcc             | 39         | N-2        | A <sub>15</sub> | 76         |

| A-8     | D <sub>5</sub>    | 51         | D-3        | M <sub>0. 1</sub>  | 3          | K-1        | RST             | 13         | N-3        | Vcc             | 17         |

| A-9     | GND               | 50         | D-11       | T <sub>6</sub>     | 102        | K-2        | OED             | 72         | N-4        | Y <sub>14</sub> | 19         |

| A-10    | D <sub>6</sub>    | 49         | D-12       | T <sub>5</sub>     | 43         | К-3        | ERROR           | 12         | N-5        | GND             | 20         |

| A-11 .  | Vcc               | 47         | D-13       | T <sub>4</sub>     | 103        | K-11       | l <sub>3</sub>  | 92         | N-6        | Y <sub>13</sub> | 21         |

| A-12    | A <sub>7</sub>    | 106        | E-1        | Cin                | 5          | K-12       | l <sub>2</sub>  | 33         | N-7        | D <sub>11</sub> | 24         |

| A-13    | Y <sub>7</sub>    | 46         | E-2        | M <sub>0. 2</sub>  | 65         | K-13       | 11              | 93         | N-8        | A <sub>11</sub> | 84         |

| B-1     | M <sub>1, 0</sub> | 61         | E-3        | M <sub>3, 1</sub>  | 64         | L-1        | INTR            | 14         | N-9        | GND             | 26         |

| B-2     | Αο                | 60         | E-11       | GND                | 97         | L-2        | INTEN           | 74         | N-10       | Ag              | 28         |

| B-3     | Yo                | 119        | E-12       | GND                | 98         | L-3        | INTA            | 73         | N-11       | Vcc             | 29         |

| B-4     | Y1                | 117        | E-13       | GND                | 99         | L-4        | D <sub>14</sub> | 18         | N-12       | Y <sub>8</sub>  | 90         |

| B-5     | A <sub>2</sub>    | 116        | F-1        | M <sub>1, 2</sub>  | 6          | L-5        | D <sub>13</sub> | 79         | N-13       | FC              | 31         |

| B-6     | D3                | 55         | F-2        | M <sub>2, 2</sub>  | 66         | L-6        | GND             | 23         |            |                 |            |

| B-7     | D <sub>4</sub>    | 112        | F-3        | GND                | 8          | L-7        | A <sub>12</sub> | 22         |            |                 |            |

| B-8     | Y4                | 111        | F-11       | T <sub>10</sub>    | 100        | L-8        | VCC             | 83         |            |                 |            |

| B-9     | A <sub>5</sub>    | 110        | F-12       | T <sub>7</sub>     | 42         | L-9        | D <sub>10</sub> | 85         |            |                 |            |

| B-10    | A <sub>6</sub>    | 108        | F-13       | T <sub>8</sub>     | 101        | L-10       | Y <sub>10</sub> | 27         |            |                 |            |

| B-11    | D <sub>7</sub>    | 107        | G-1        | M <sub>1, 3</sub>  | 9          | L-11       | Y <sub>9</sub>  | 88         |            |                 |            |

| B-12    | T <sub>1</sub>    | 45         | G-2        | M <sub>0</sub> , 3 | 67         | L-12       | 14              | 32         |            |                 |            |

| B-13    | To                | 105        | G-3        | M <sub>3, 2</sub>  | 7          | L-13       | S <sub>2</sub>  | 35         | [          |                 |            |

| C-1     | M <sub>2, 0</sub> | 2          | G-11       | T <sub>11</sub>    | 40         | M-1        | SLAVE           | 75         |            |                 |            |

| C-2     | M <sub>3, 0</sub> | 62         | G-12       | s <sub>0</sub>     | 36         | M-2        | HOLD            | 15         | l          |                 |            |

| C-3     | D <sub>1</sub>    | 118        | G-13       | CP                 | 96         | M-3        | Y <sub>15</sub> | 77         |            |                 |            |

| C-4     | Do                | 57         | H-1        | Moo                | 60         | M-4        | 115             | 70         | l          |                 |            |

69

M-4

A<sub>14</sub>

78

57

H-1

M<sub>2, 3</sub>

C-4

$D_2$

## PIN DESIGNATIONS (Sorted by Pin Name)

| PIN NAME        | PIN<br>NO. | PAD<br>NO. | PIN NAME        | PIN<br>NO. | PAD<br>NO. | PIN NAME           | PIN<br>NO. | PAD<br>NO. | PIN NAME        | PIN<br>NO. | PAD<br>NO. |

|-----------------|------------|------------|-----------------|------------|------------|--------------------|------------|------------|-----------------|------------|------------|

| _               | 1 _        | 37         | Dg              | M-11       | 89         | INTEN              | L-2        | 74         | Т6              | D-11       | 102        |

| _               | _          | 39         | Do              | M-10       | 87         | INTR               | L-1        | 14         | T <sub>7</sub>  | F-12       | 42         |

| _               | _          | 97         | D <sub>10</sub> | L-9        | 85         | Mo, o              | A-1        | 1          | T <sub>8</sub>  | F-13       | 101        |

| _               |            | 99         | D <sub>11</sub> | N-7        | 24         | M <sub>0</sub> , 1 | D-3        | 3          | T <sub>9</sub>  | C-13       | 41         |

| A-FULL          | J-3        | 70         | D <sub>12</sub> | M-6        | 81         | M <sub>0, 2</sub>  | E-2        | 65         | T <sub>10</sub> | F-11       | 100        |

| A <sub>0</sub>  | B-2        | 60         | D <sub>13</sub> | L-5        | 79         | M <sub>0</sub> , 3 | G-2        | 67         | T <sub>11</sub> | G-11       | 40         |

| A <sub>1</sub>  | A-4        | 58         | D <sub>14</sub> | L-4        | 18         | M <sub>1.0</sub>   | B-1        | 61         | GND             | J-1        | 1.         |

| A <sub>2</sub>  | B-5        | 116        | D <sub>15</sub> | N-1        | 16         | M <sub>1. 1</sub>  | D-2        | 63         | GND             | N-5        | 20         |

| A <sub>3</sub>  | A-6        | 114        | GND             | E-12       | 97         | M <sub>1, 2</sub>  | F-1        | 6          | GND             | A-9        | 50         |

| A <sub>4</sub>  | C-7        | 52         | GND             | E-13       | 98         | M <sub>1, 3</sub>  | G-1        | 9          | GND             | N-9        | 2          |

| A <sub>5</sub>  | B-9        | 110        | GND             | E-11       | 99         | M <sub>2</sub> , 0 | C-1        | 2          | GND             | A-5        | 5          |

| A <sub>6</sub>  | B-10       | 108        | GND             | F-3        | 8          | M <sub>2</sub> , 1 | D-1        | 4          | Vcc             | N-3        | 1          |

| A <sub>7</sub>  | A-12       | 106        | GND             | L-6        | 23         | M <sub>2, 2</sub>  | F-2        | 66         | Vcc             | N-11       | 2          |

| A <sub>8</sub>  | M-12       | 30         | GND             | C-6        | 113        | M <sub>2</sub> , 3 | H-1        | 69         | Vcc             | A-3        | 5          |

| A <sub>9</sub>  | N-10       | 28         | Vcc             | J-13       | 38         | M <sub>3</sub> , 0 | C-2        | 62         | Vcc             | A-11       | 4          |

| A <sub>10</sub> | M-9        | 86         | Vcc             | H-3        | 68         | M <sub>3, 1</sub>  | E-3        | 64         | Y <sub>0</sub>  | B-3        | 11         |

| A <sub>11</sub> | N-8        | 84         | Vcc             | C-8        | 53         | M <sub>3, 2</sub>  | G-3        | 7          | Y <sub>1</sub>  | B-4        | 11         |

| A <sub>12</sub> | L-7        | 22         | Vcc             | L-8        | 83         | M <sub>3. 3</sub>  | H-2        | 10         | Y <sub>2</sub>  | C-5        | 11         |

| A <sub>13</sub> | M-5        | 80         | Vcc             | J-12       | 37         | OED                | K-2        | 72         | Y <sub>3</sub>  | A-7        | 5          |

| A <sub>14</sub> | M-4        | 78         | Vcc             | J-11       | 39         | RST                | K-1        | 13         | Y4              | B-8        | 11         |

| A <sub>15</sub> | N-2        | 76         | EQUAL           | J-2        | 71         | S <sub>0</sub>     | G-12       | 36         | Y <sub>5</sub>  | C-9        | 10         |

| Cin             | E-1        | 5          | ERROR           | K-3        | 12         | S <sub>1</sub>     | H-12       | 95         | Y <sub>6</sub>  | C-10       | 4          |

| CP              | G-13       | 96         | FC              | N-13       | 31         | S <sub>2</sub>     | L-13       | 35         | Y <sub>7</sub>  | A-13       | 4          |

| D <sub>0</sub>  | A-2        | 120        | HOLD            | M-2        | 15         | S <sub>3</sub>     | H-13       | 94         | Y <sub>8</sub>  | N-12       | 8          |

| D <sub>1</sub>  | C-3        | 118        | lo              | H-11       | 34         | SLAVE              | M-1        | 75         | Y <sub>9</sub>  | L-11       | 8          |

| D <sub>2</sub>  | C-4        | 57         | l ii            | K-13       | 93         | Τo                 | B-13       | 105        | Y <sub>10</sub> | L-10       | 2          |

| D <sub>3</sub>  | B-6        | 55         | l <sub>2</sub>  | K-12       | 33         | T <sub>1</sub>     | B-12       | 45         | Y <sub>11</sub> | M-8        | 2          |

| D <sub>4</sub>  | B-7        | 112        | 13              | K-11       | 92         | T <sub>2</sub>     | C-12       | 104        | Y <sub>12</sub> | M-7        | 8          |

| D <sub>5</sub>  | A-8        | 51         | 14              | L-12       | 32         | T <sub>3</sub>     | C-11       | 44         | Y <sub>13</sub> | N-6        | 2          |

| D <sub>6</sub>  | A-10       | 49         | 15              | M-13       | 91         | T <sub>4</sub>     | D-13       | 103        | Y14             | N-4        | 1          |

| D <sub>0</sub>  | B-11       | 107        | ÎNTA            | L-3        | 73         | T <sub>5</sub>     | D-12       | 43         | Y <sub>15</sub> | M-3        | 7          |

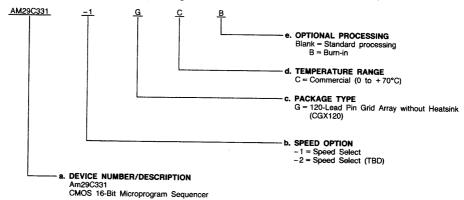

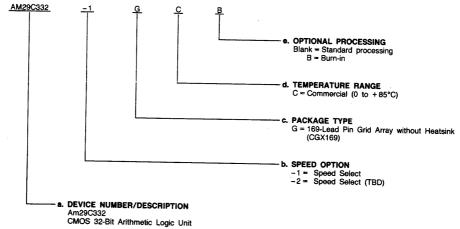

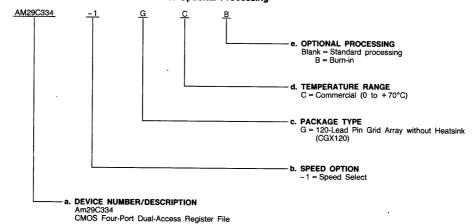

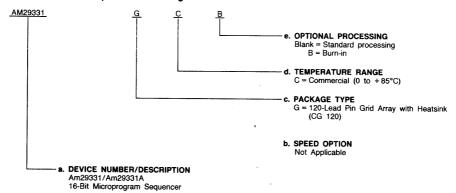

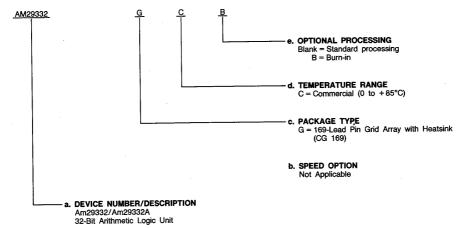

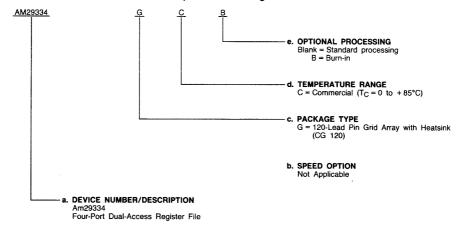

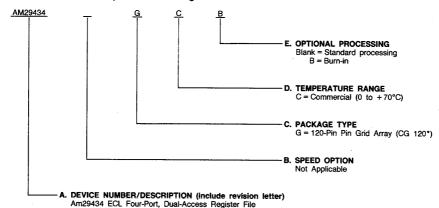

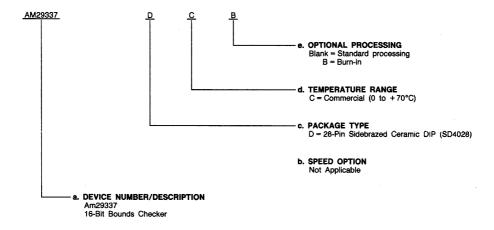

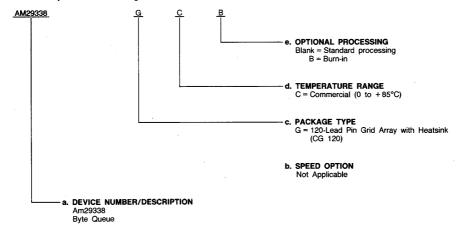

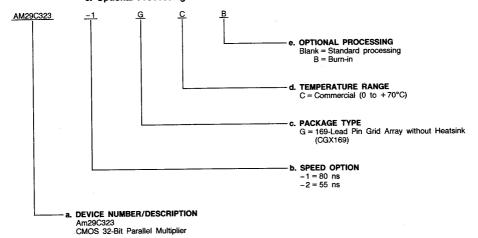

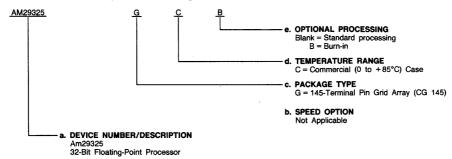

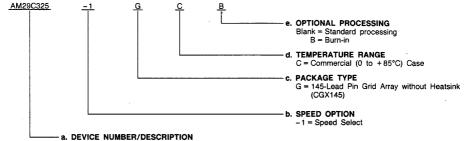

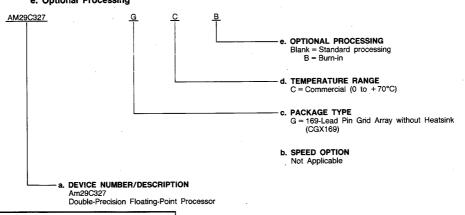

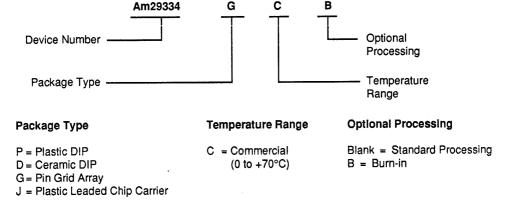

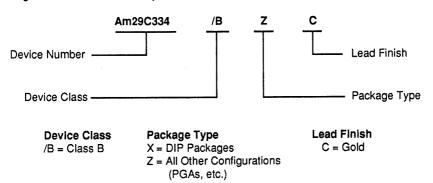

## ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

# Valid Combinations AM29C331 AM29C331-1 GC, GCB

## Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

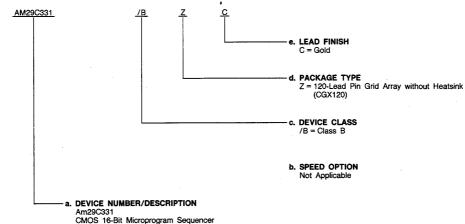

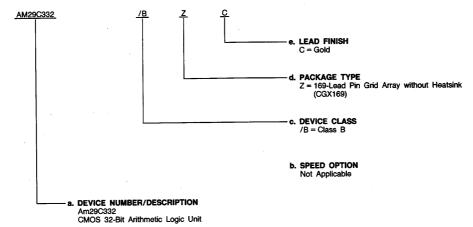

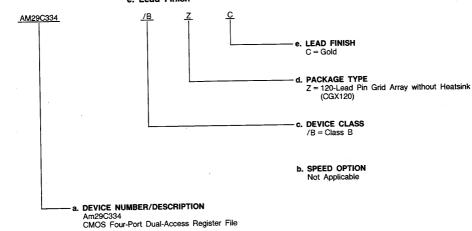

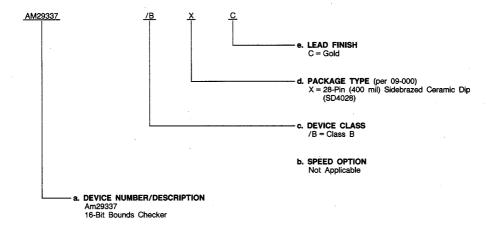

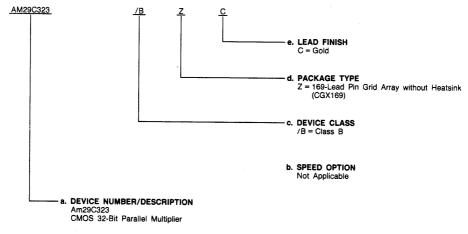

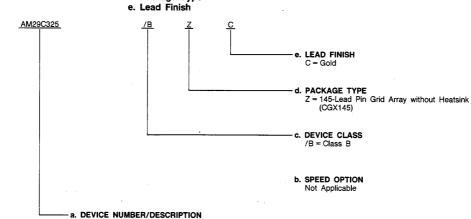

## MILITARY ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid    | Cor | nbinations |  |

|----------|-----|------------|--|

| AM29C331 |     | /BZC       |  |

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

## **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

## PIN DESCRIPTION

## A<sub>0</sub> - A<sub>15</sub> Alternate Data (Input)

Input to address multiplexer and counter.

## A-FULL Almost Full (Bidirectional; Three-State)

Indicates that  $28 \le SP \le 63$  (meaning there are five or less empty locations left on stack). Also active during stack underflow.

#### Cin Carry In (Input, Active LOW)

Carry-in to the incrementer.

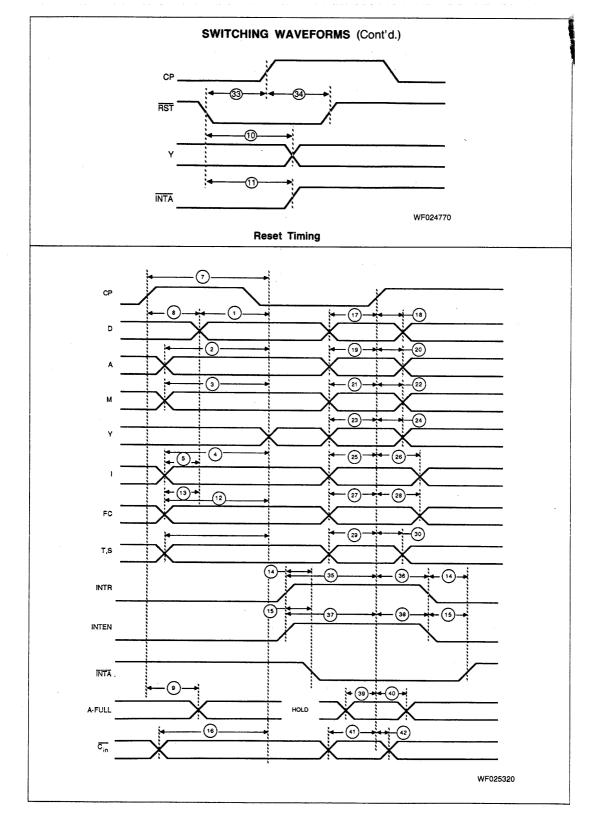

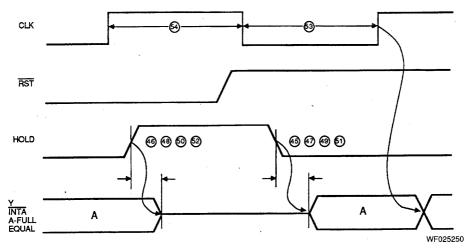

#### CP Clock Pulse (Input)

Clocks sequencer at the LOW-to-HIGH transition.

## D<sub>0</sub> - D<sub>15</sub> Data (Bidirectional, Three-State)

Input to address multiplexer, counter, stack, and comparator register. Output for stack and stack pointer.

#### EQUAL Equal (Bidirectional, Three-State)

Indicates that the address comparator is enabled and has found a match.

#### ERROR Error (Output)

Indicates a master/slave error in the slave mode. Indicates a malfunctioning driver or contention of any output in the master mode.

## FC Force Continue (Input)

Overrides instruction with CONTINUE.

#### HOLD Hold (Input)

Stops the sequencer and three-states the outputs.

## l<sub>0</sub>-l<sub>5</sub> Instruction (Input)

Selects one of 64 instructions.

### INTA Interrupt Acknowledge (Bidirectional; Three-State, Active LOW)

Indicates that an interrupt is accepted.

### INTEN Interrupt Enable (Input)

Enables interrupts.

#### INTR Interrupt Request (Input)

Requests the sequencer to interrupt execution.

#### M<sub>0-3, 0-3</sub> Multiway (Input)

Four sets of multiway inputs providing 16-way branches. The first index refers to the set number.

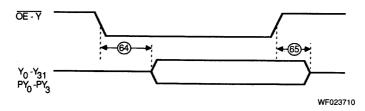

#### OE<sub>D</sub> Output Enable — D-Bus (Input)

Enables the D-bus driver, provided that the sequencer is not in the hold or slave mode.

## RST Reset (Input; Active LOW)

Resets the sequencer.

### S<sub>0</sub> - S<sub>3</sub> Select (Input)

Selects one of 16 test conditions.

#### SLAVE Slave (Input)

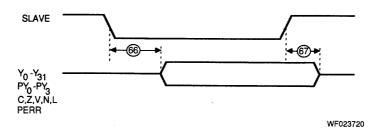

Makes the sequencer a slave.

#### T<sub>0</sub>-T<sub>11</sub> Test (Input)

Provides external test inputs.

#### Y<sub>0</sub> - Y<sub>15</sub> Address (Bidirectional: Three-State)

Output of microcode address. Input for interrupt address.

## **FUNCTIONAL DESCRIPTION**

### **Architecture**

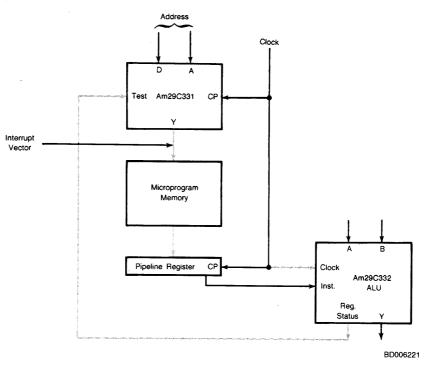

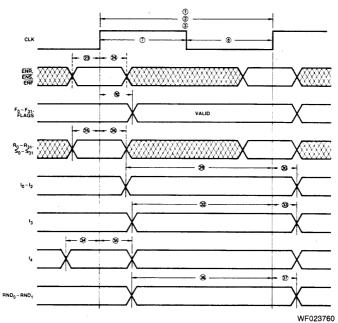

The major blocks of the sequencer are the address multiplexer, the address register (AR), the stack (with the top of stack denoted TOS), the counter (C), the test multiplexer with logic, and the address comparison register (R) (Figure 1). The bidirectional D-bus provides branch addresses and iteration counts; it also allows access to the stack from the outside. The A-bus may be used for map addresses. There are four sets of four-bit multiway branch inputs (M). The bidirectional Y-bus either outputs microprogram addresses or inputs interrupt addresses. The buses are all 16 bits wide. Figure 1 shows a detailed block diagram of the sequencer.

#### Address Multiplexer

The address multiplexer can select an address from any of five sources:

- 1) A branch address supplied by the D-bus

- 2) A branch address supplied by the A-bus

- 3) A multiway-branch address

- 4) A return or loop address from the top of stack

- 5) The next sequential address from the incrementer

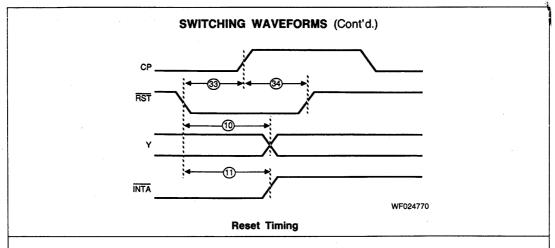

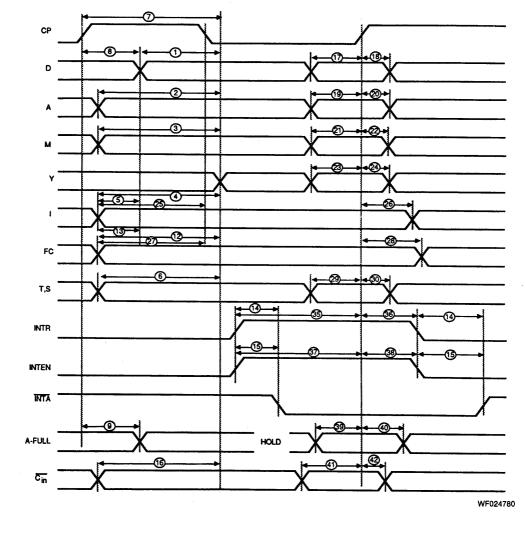

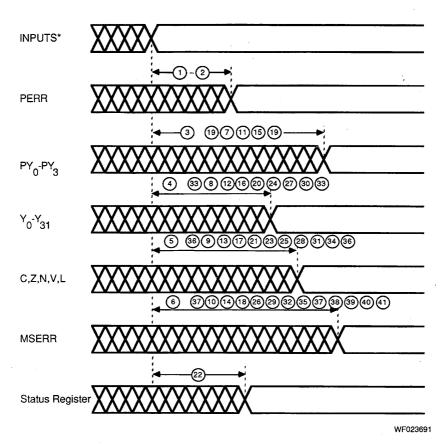

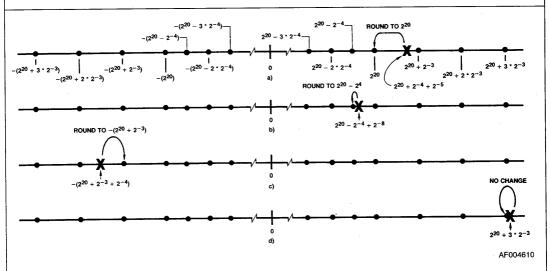

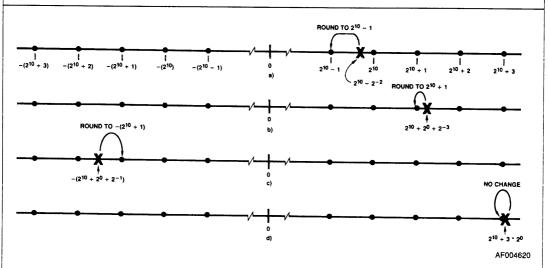

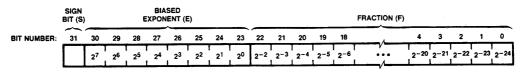

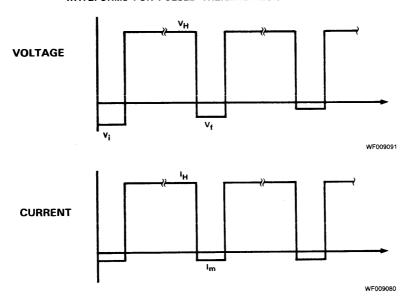

#### **Multiway-Branch Address**